低启亮电压全溶液加工量子点发光器件

曹丽娟, 江从彪, 罗 宇, 李妙姿, 黎佳立, 寸阳珂, 王 坚, 彭俊彪, 曹 镛

(华南理工大学 材料科学与工程学院,广东 广州 510640)

1 引 言

胶体量子点发光材料(Colloidal quantum dots, QDs)因其具有发射波长可调、发射光谱窄、效率高、光热稳定性好等优点,在学术界和工业界都引起人们的极大关注[1-9]。近年来,R-,G-,B-QLEDs的外量子效率(External quantum efficiency, EQE)均超过20%,突显了QLEDs在显示中的巨大应用潜力[10-14]。QDs具有可溶液加工成膜的特点,量子点发光器件的各功能层的制备可以采用溶液加工的制备方法,但目前QLEDs的金属阴极仍然需要通过真空蒸镀的方法沉积。为在制备溶液加工的QLEDs时实现更好的工艺兼容性,降低器件制备成本,全溶液加工QLEDs(包括阴极)工艺是值得研究的。溶液加工电极材料可以选择碳纳米管[15-16]、导电聚合物[17-19]、金属网格、石墨烯[20-21]和金属纳米线[22]等材料,但这些材料存在不同方面的问题,如导电聚合物(如PEDOT∶PSS)的导电性较低,电/热稳定性较差;石墨烯和碳纳米管由于其自身的非极性性质,在普通溶剂中分散性较差;金属纳米线薄膜的线与线之间易形成较大接触电阻,会限制载流子的注入。然而,以银、铜等金属纳米粒子为基础的电极材料可以在较低的退火温度下实现高电导率,已广泛应用于印刷电子领域[23]。但是用于电致发光器件仍然面临一定的挑战,比如金属纳米颗粒油墨的溶剂对其下面功能层的侵蚀和渗透,会影响功能层的性质,导致发光器件性能的劣化。

用导电银浆做阴极,前期已有研究。对于有机发光器件,曾文进[24]等人用刮涂的方法将导电银浆涂敷在一种聚电解质薄膜PFNR2(水/醇溶性共轭聚合物,聚[9,9-二辛基芴-9,9-双(N,N-二甲基胺丙基)芴])上,制成了聚合物发光二极管,实现了全溶液加工的红、绿、蓝高效率聚合物发光二极管(Polymer light-emitting diodes, PLEDs),但由于PFNR2被银浆溶剂侵蚀,导致器件Vt相较于蒸镀电极器件偏高。随后,郑华[25]等人用喷墨打印方法制备Ag NPs薄膜作为阴极,实现了印刷全彩色高分子发光显示器件。为了防止导电银浆中的溶剂侵入到器件的功能层中,将界面材料PFN与环氧树脂共混,共同作为电子注入层(Electron inject layer, EIL)与溶剂阻挡层。从结果看,PFN/环氧树脂还不能严格抵抗银浆中溶剂的侵蚀,同样存在显示器件发光效率较低、驱动电压较高等问题。为解决这一问题,宋晨[26]等人使用无机纳米氧化锌(Zinc oxide, ZnO)作为电子传输层(Electron transport layer, ETL),旋涂Ag NPs作为阴极,制备了全溶液加工的有机电致发光器件(Organic light-emitting diodes, OLED),结果表明ZnO层不仅可以使电子有效注入,而且表现出了抵挡银浆中溶剂对功能层的侵蚀和渗透作用,使OLED器件具有较好的发光效率,但是器件Vt仍然偏高。

针对QLEDs,为实现全溶液加工QLEDs的低Vt,本文采用ZnO作为ETL和溶剂阻挡层来制备全溶液加工的QLEDs,发明了低真空与加热干燥组合处理工艺。通过优化阴极处理工艺,制备的QLEDs器件Vt与真空蒸镀Ag电极的基本相同。这一结果为实现低Vt的全溶液加工QLEDs提供了工艺参考。

2 实 验

2.1 实验材料

实验采用的氧化铟锡(indium tin oxide, ITO)基板方阻为15~20 Ω/□,购自中国南玻集团;PEDOT∶PSS(Clevios P VP AI 4083)购自 Heraeus Electronic Materials Division;poly(9,9-dioctyfluorene-co-N-(4-butylphenyl)diphenyla-

mine(TFB)购自American Dye Source;核壳结构的红、绿、蓝CdSe/ZnS QDs,配体分别为油酸、油胺和油酸,荧光量子效率分别约为88%、85%和80%,购自嘉兴纳鼎光电技术有限公司; ZnO购自广东省普加福光电科技有限公司;Ag NPs墨水(溶剂为三乙二醇单甲醚(triethylene glycol monomethyl ether, TGME))购自Advanced Nano Products;实验中用到的二甲苯和乙醇纯度为99.9%,购自Sigma-Aldrich。

2.2 器件制备

实验采用QLEDs的结构为ITO/PEDOT∶PSS(40 nm)/TFB(35 nm)/QDs(Xnm)/ZnO(40 nm)/Ag NPs或Ag。这里PEDOT∶PSS、TFB、QDs、ZnO、ITO和Ag NPs或Ag分别为空穴注入层(Hole inject layer, HIL)、空穴传输层(Hole transport layer, HTL)、发光层(Emitting material layer, EML)、ETL、阳极和阴极。在制备QLEDs器件之前,先对ITO基板进行预处理,ITO基板分别在四氢呋喃、洗液、去离子水和异丙醇中依次超声清洗10 min,最后放在70 ℃的烘箱中干燥。在旋涂制备PEDOT∶PSS薄膜之前,先对ITO玻璃进行UV处理5 min,清洁ITO表面并提高ITO的功函数,然后在空气中旋涂制备40 nm厚度的PEDOT∶PSS。将PEDOT∶PSS基板转移到氮气手套箱中,在180 ℃下退火10 min。再旋涂二甲苯TFB溶液,得到厚度为35 nm的TFB薄膜,然后在120 ℃下退火10 min。QDs溶解在正辛烷中,浓度为15 mg/mL,分别在TFB层上旋涂制备厚度为30,25,27 nm的R-、G-、B-QDs薄膜,并将QDs层在100 ℃退火11 min。然后在QDs层上旋涂厚度为40 nm的溶解于乙醇、浓度为20 mg/mL的ZnO,在120 ℃下退火30 min。最后,在1×10-4Pa的压力下沉积120 nm厚度的Ag(记为:eva. Ag)。对于使用Ag NPs为阴极的器件,在ZnO上旋涂厚度为150 nm的Ag NPs薄膜,先在真空度为1×103Pa的真空过渡舱中干燥10 min,然后在氮气手套箱中进行130 ℃退火15 min(记为:sol-vac. Ag NPs)。而直接在130 ℃下退火15 min的器件,标记为sol. Ag NPs。最后将制备完成的量子点发光器件进行包封,待测试。

2.3 器件表征

器件的光电性能表征使用电源(Keithley2400)和色彩亮度计(CS-200,Konica Minolta公司)。薄膜厚度测量使用台阶扫描仪(Dektak 150,Veeco公司)。器件截面形貌图使用高分辨率热场发射扫描电子显微镜进行观察(ZEISS公司)。薄膜方块电阻使用四探针测试仪测量(KDY-1,广州昆德科技有限公司)。薄膜表面功函数使用扫描开尔文探针测试仪进行测量(UHVSKP,KP Technology Ltd.公司)。光生伏打效应测试是将器件置于 AM 1.5G(air mass 1.5 global)强度的太阳(SAN-EI,Japan)模拟光照下,通过使用电源采集器件的电流-电压特性曲线。

3 结果与讨论

3.1 全溶液加工量子点器件

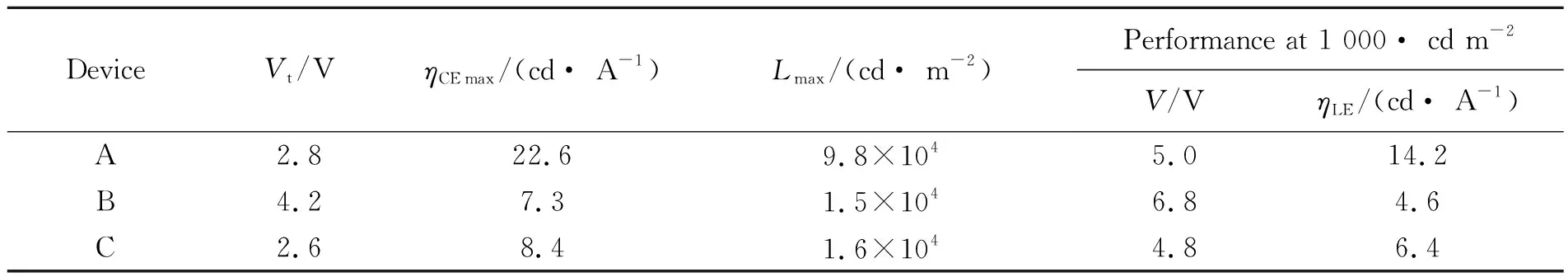

量子点电致发光的器件结构和能级结构如图1所示。为了进行对比,相同条件下制备了蒸镀Ag电极的器件。ZnO因其高的电子迁移率(2×10-3cm2·V-1·s-1)和与QDs层具有良好的能级匹配而被用作ETL。并且,ZnO层在热退火后具有良好的抗溶剂侵蚀性,这有利于制备全溶液加工的多层器件。共轭聚合物TFB由于其较高的空穴迁移率(1×10-2cm2·V-1·s-1)用于HTL,有助于载流子平衡和提高器件电致发光(Electroluminescent,EL)性能。为了研究采用不同加工工艺的阴极对量子点电致发光器件Vt的影响,制备了3种不同加工类型阴极的G-QLEDs。3种发光器件的电流密度(J)和亮度(L)随电压(V)变化的J-V-L特性曲线以及J与电流效率(ηCE)的J-ηCE特性曲线,如图1(c)和1(d)所示。其中,3种发光器件除阴极制备工艺不同外,其余各层制备方式相同。Device A阴极为sol-vac. Ag NPs,Device B阴极为sol. Ag NPs,Device C阴极为eva. Ag。从图中可以看出,Device B 具有较差的EL性能,表现为较低的ηCE7.3 cd·A-1和较高的Vt4.2 V。3种器件的性能数据总结在表1中。

图1 (a)溶液加工Ag NPs 阴极量子点器件结构图;(b)器件能级图;(c)不同阴极的QLEDs的J-V-L光电特性曲线;(d)J-ηCE特性曲线。Fig.1 (a) Device structure of QLEDs with solution-processed Ag NPs cathode; (b) Energy diagrams of the devices; (c) J-V-L characteristics; (d) J-ηCE characteristics of G-QLEDs with different cathodes.

表1 3种G-QLEDs的性能汇总表Tab.1 Device performances of the three kinds of G-QLEDs

3.2 启亮电压分析

由于ZnO具有较好的抗溶剂渗透和侵蚀性,因此导致溶液加工阴极器件的Vt较高的原因主要集中在阴极侧,也就是主要在ZnO/Ag NPs界面处。该处界面势垒的提高可能有以下方面的原因:(1)残余极性溶剂TGME在阴极界面可能会引入偶极子阻挡电子注入;(2)Ag NPs 退火温度较低,表面的配体脱落不完全,银膜导电性差;(3)ZnO和Ag NPs在退火过程中可能在界面形成共混,形成电子陷阱,从而影响电子注入。

由于银浆的溶剂TGME的沸点较高(249 ℃),在130 ℃的退火温度和15 min的时间下,溶剂可能没有完全被去除。残留的TGME溶剂可能会在ZnO薄膜的表面引入偶极子[27],这可能会导致电子注入势垒的提高。为了探索TGME残留是否会引起器件Vt升高,制备了TGME处理ZnO的蒸镀Ag器件。具体处理方式为:待器件完成ZnO层的制备后,以3 000 r/min的转速和30 s的时间旋涂TGME溶剂在ZnO表面,并在130 ℃下退火15 min。G-QLEDs的V-L曲线如图2(a)所示,器件的Vt均为2.8 V。可见,在阴极界面中引入TGME没有影响器件Vt。

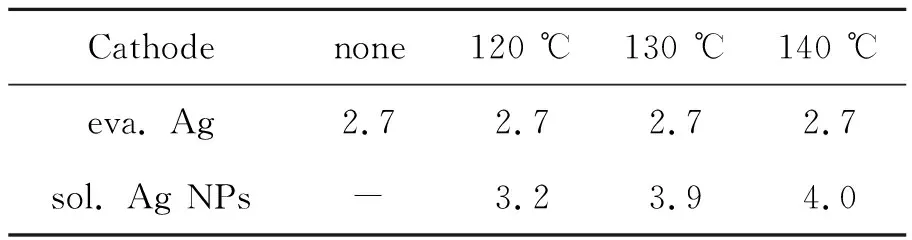

通常情况下,Ag NPs表面被有机配体包围,以保护不稳定的活性裸金属表面并保持纳米颗粒的高表面积体积比,防止其自聚集,维持均匀分散状态[28]。但是,这些绝缘配体将阻止电子在Ag NPs之间的传输。Moon[29]等人报道,Ag NPs薄膜在退火过程中,配体将从Ag NPs的表面脱落,使得纳米颗粒之间接触紧密,且随着退火温度的升高,配体脱落更完全,Ag NPs之间融合得更加致密,从而增加Ag NPs薄膜的电导率。因此,为了提高Ag NPs薄膜的电导率,降低Vt,制备了阴极在不同退火温度下的G-QLEDs器件。图2(b)和2(c)显示了在120,130,140 ℃退火温度下G-QLEDs的V-L曲线。由表2可见,采用sol. Ag NPs阴极器件的Vt随着退火温度从120 ℃升高至140 ℃不仅没有降低,反而从3.2 V增加到4.0 V,而eva. Ag为阴极器件的Vt则保持在2.8 V。由此可知,全溶液加工器件出现较高Vt的原因不是由于Ag NPs膜中配体的残留引起阴极导电性差导致的。

表2 不同退火温度器件的启亮电压

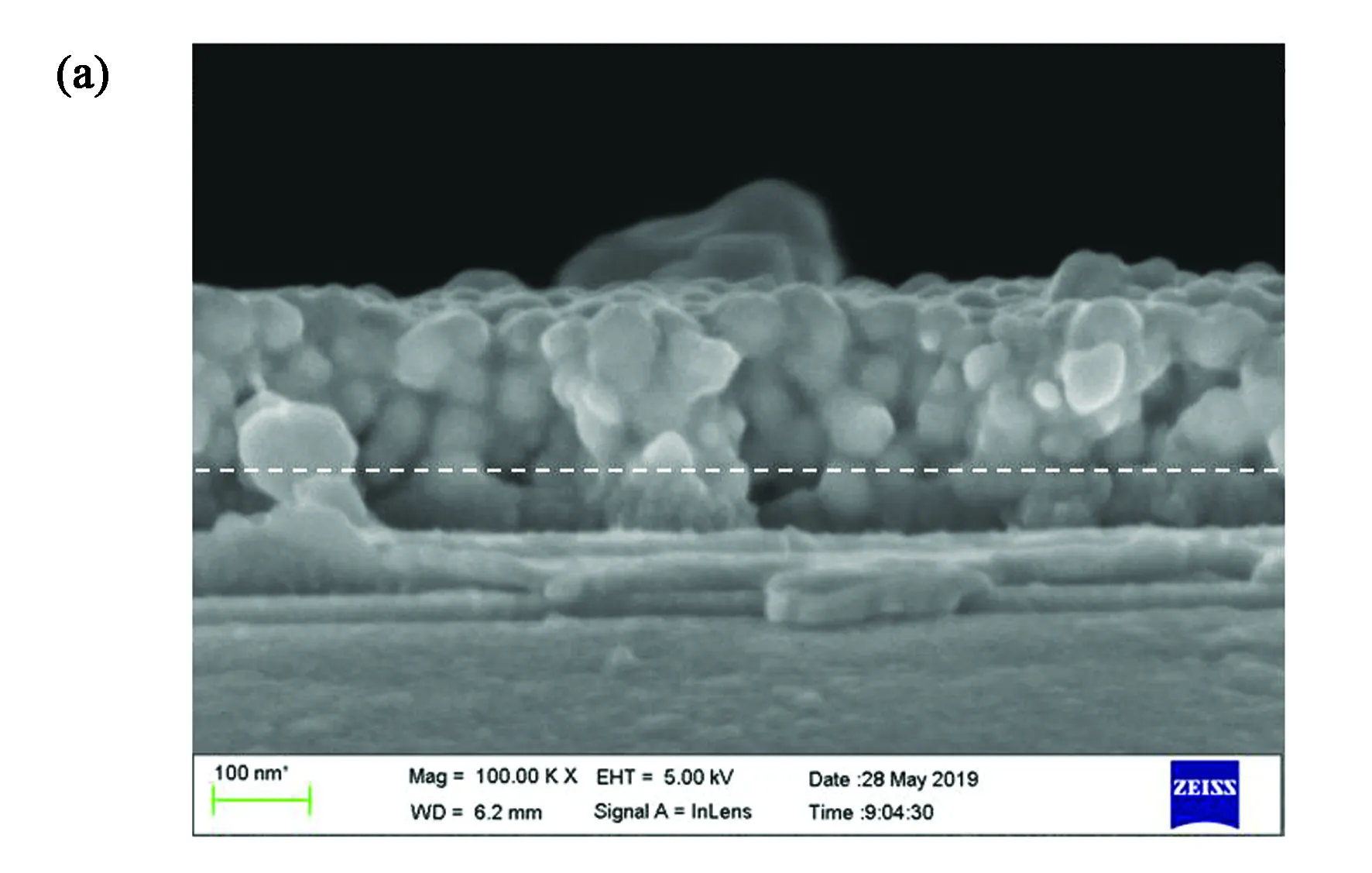

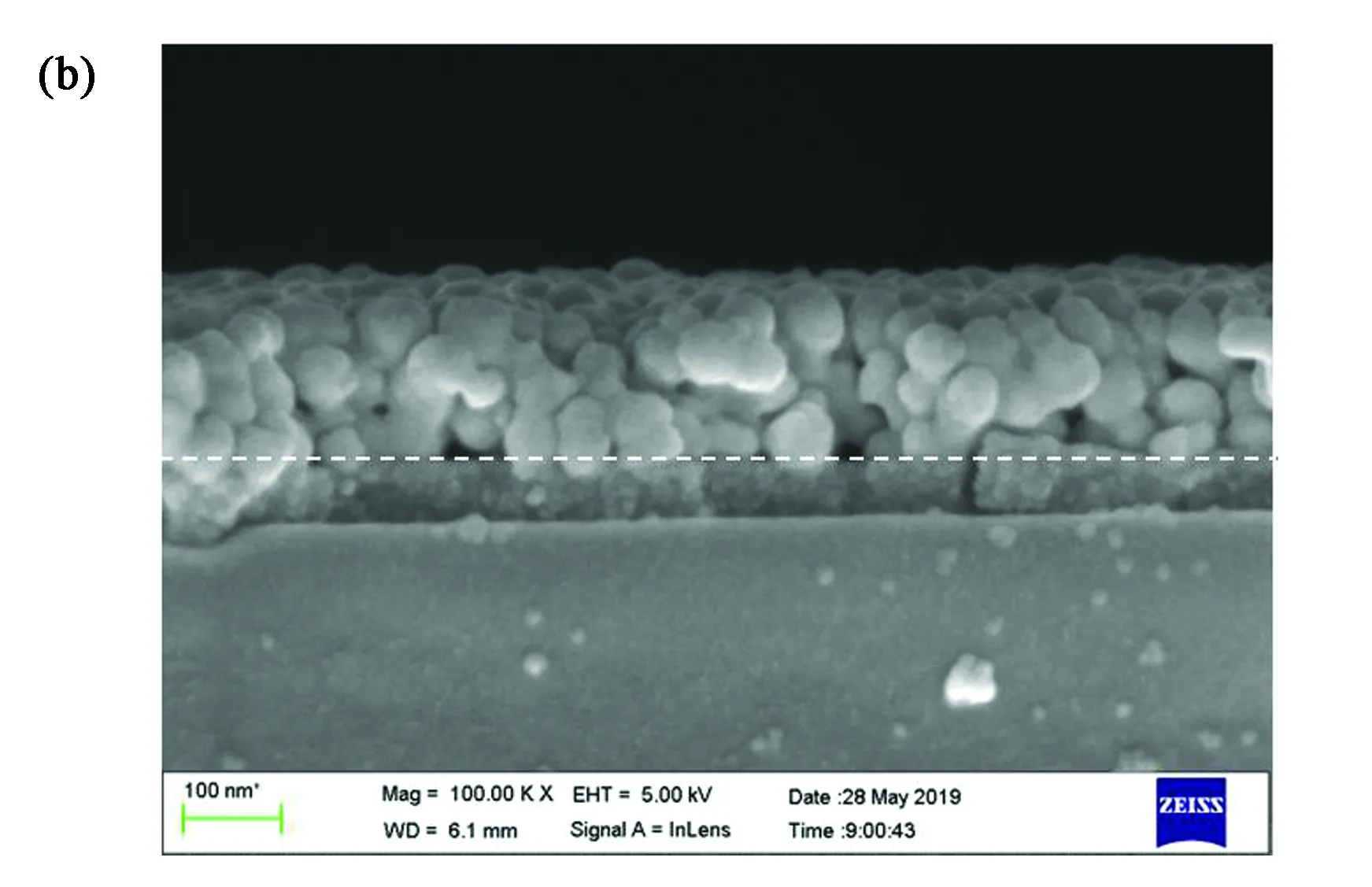

为了探索溶液加工阴极器件Vt变化的原因,对ZnO/sol. Ag NPs截面的形貌进行了SEM表征,如图3(a)所示。ZnO/sol. Ag NPs的界面不清晰,可能产生了界面共混,为了验证共混情形的存在,我们分别测量了ZnO、sol-vac. Ag NPs、sol. Ag NPs、eva. Ag、ZnO/sol-vac. Ag NPs、ZnO/sol. Ag NPs 和 ZnO/Ag 薄膜的膜厚,如表3所示。可以看到,直接退火的ZnO/Ag NPs薄膜总厚度小于分别测量的ZnO和Ag NPs厚度之和,说明ZnO/sol. Ag NPs界面发生共混,共混可能产生更多的界面陷阱,俘获电子能力增强,使得G-QLEDs的Vt升高。为了探究界面共混产生的具体原因,我们利用TGME溶剂蒸汽和Ag NPs溶液蒸汽对制备好的器件(除阴极)进行蒸汽处理。具体的操作如下:将TGME溶剂和Ag NPs溶液分别装在小玻璃瓶里,瓶口大小刚好可以放下ITO玻璃片;然后将两个瓶子放到130 ℃的温度下加热;将制备好的器件放在瓶口,用蒸汽处理3 min;处理后再将器件放在热台上退火15 min,待冷却后刮出阳极边,放入真空蒸镀舱进行Ag阴极制备。图4(c)为蒸汽处理的示意图。

图3 ITO/ZnO/Ag NPs横截面的SEM图。(a)直接退火;(b)退火前低真空干燥。Fig.3 SEM images of ITO/ZnO/Ag NPs cross section. (a) Annealing directly; (b) Low vacuum drying before annealing.

表3 不同加工工艺薄膜厚度统计表Tab.3 Film thickness for different processes (nm)

蒸汽处理G-QLEDs的光电性能如图4(a)和4(b)所示。从图中可知,用高温蒸汽处理器件,无论是TGME蒸汽还是Ag NPs蒸汽都会使得器件性能急剧变差,Vt升高至4.8 V和7.5 V,ηCE下降至0.54 cd/A和0.20 cd/A。其中,用Ag NPs溶液蒸汽处理的器件性能更差,说明Ag NPs溶液中还有其余添加剂在影响器件的性能。并且,对比图2(a)中TGME处理ZnO的器件Vt为2.8 V,而TGME蒸汽处理器件的Vt为4.8 V可知,溶剂处理方式对器件性能的影响不同。旋涂TGME处理ZnO表面,在进行后退火的过程中,溶剂挥发的方向是四面挥发,只有小部分溶剂可能正面影响ZnO,对ZnO的影响较小。而蒸汽处理是直接对ZnO表面进行影响,因而两种器件性能表现差异较大。因此推测,界面共混的产生是由于Ag NPs溶液中的其他添加剂在高温退火过程中侵蚀ZnO,导致溶解的ZnO在界面渗入Ag NPs间隙中,形成共混并引起薄膜厚度发生变化。

图4 蒸汽处理QLEDs的(a)J-V-L曲线和(b)J-ηCE曲线;(c)蒸汽处理示意图;(d)不同阴极QLEDs的 I-V特性。Fig.4 (a)J-V-L curves and (b) J-ηCE curves of QLEDs with steam treatment; (c) Illustration of steam treatment; (d) I-V characteristics of G-QLEDs with different cathodes.

为了进一步验证共混可能导致阴极势垒的形成,利用光生伏打效应来测试器件的内建电势,以研究接触电势与Vt之间的关系,图4(d)显示了不同阴极的G-QLEDs的光生伏打测试曲线。此处Device A、Device B、Device C的制备工艺与图1(c)中的各器件制备工艺相同且一一对应。Device B和Device C的开路电压(Voc)分别为0.68 V和1.01 V。较小的Voc意味着较大的电子注入势垒,表明在ZnO/sol. Ag NPs界面处的混合导致更高的阴极势垒和Vt。随着退火温度的升高,共混程度也越来越严重,所以高温退火使器件的Vt进一步升高。为了抑制共混现象的发生,我们将干燥过程分为两步,首先采用低真空干燥的方式将Ag NPs薄膜内部残留的溶剂和添加剂抽干,使其挥发方式为向上挥发,降低对ZnO的影响。其次将Ag NPs薄膜进行130 ℃退火处理,促使表面配体脱落以提高Ag NPs的电导率。基于以上干燥工艺,制备了全溶液加工的G-QLEDs。如表1所示, Device A具备相对较低的Vt,约2.6 V,这与Device C相似。并且截面SEM表征结果和光生伏打效应测试同样表明了低真空预处理可以消除界面共混现象,抑制势垒的产生。

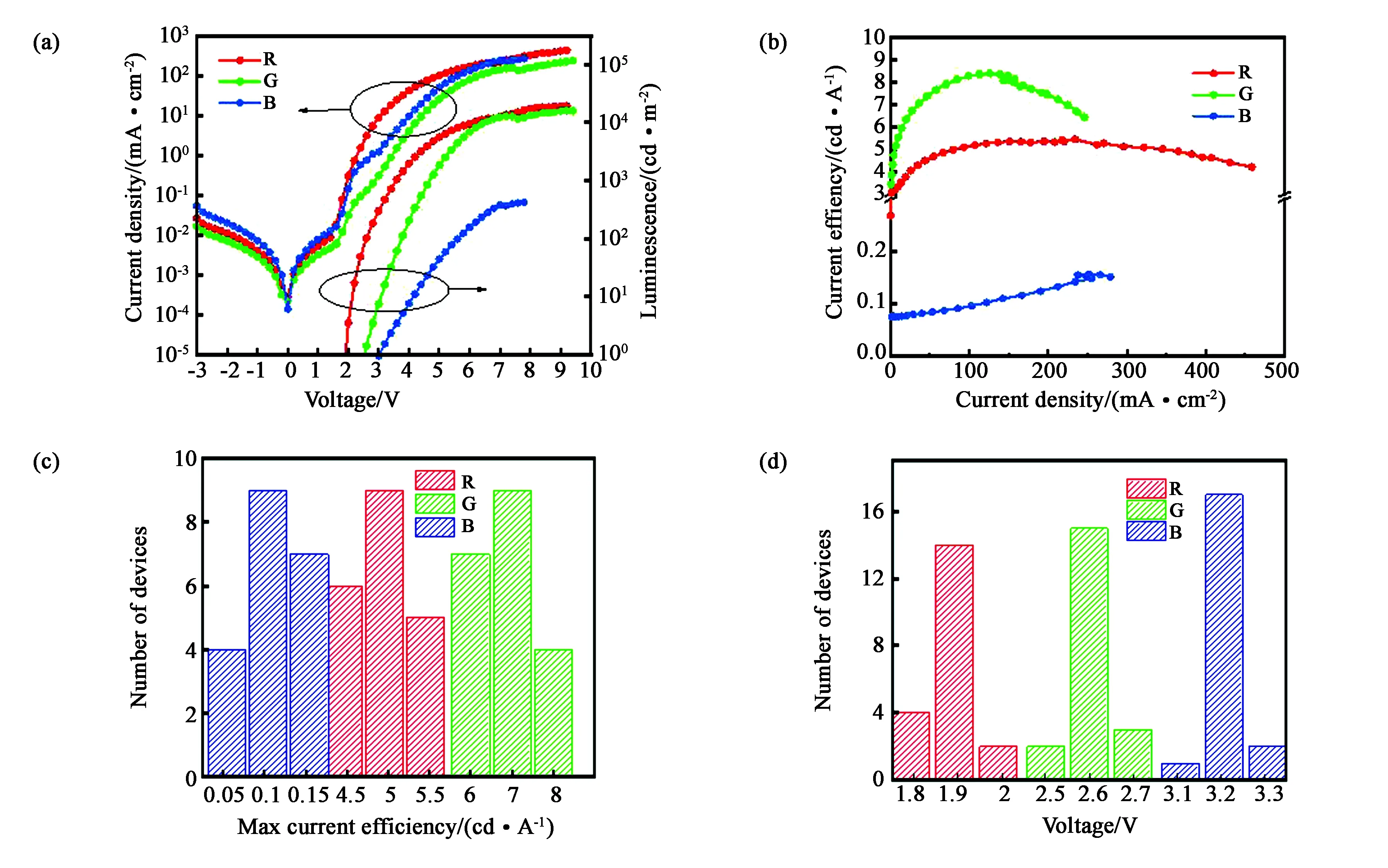

基于真空/热退火的干燥工艺,我们制备了全溶液加工的R-、G-、B-QLEDs,器件的J-V-L曲线和J-ηCE曲线如图5(a)和(b)所示,R-、G-、B-QLEDs的Vt分别为1.9,2.6,3.2 V,最大亮度分别为1.9×104,1.6×104,4.2×102cd/m2,最大ηLE分别为5.4,8.4 ,0.16 cd/A。R-、G-QLEDs均显示带隙启亮,表明阳极和阴极均是欧姆接触。 由于蓝色QDs的价带较深,因此QDs和HTL之间较大的势垒差会导致相对较高的Vt。该全溶液加工制备QLEDs的方法可实现良好的器件重复性。图5(c)和(d)所示,来自4个批次的20个器件分别显示R-、G-、B-QLEDs的平均Vt为1.9,2.6,3.2 V和平均峰值ηCE为5.0 ,6.8,0.11 cd/A。

图5 溶液加工Ag NPs阴极的R-,G-,B-QLEDs的(a)J-V-L特性和(b)J-ηCE特性;(c)分别从20个器件测量的R-,G-,B-QLEDs的峰值ηCE的直方图;(d)分别从20个设备测量的R-,G-,B-QLEDs的Vt直方图。Fig. 5 (a) J-V-L characteristics and (b) J-ηCE characteristics of R-,G-,B-QLEDs with solution-processed Ag NPs cathodes; (c) Histogram of peak ηCE measured from 20 devices for R-,G-,B-QLEDs respectively; (d) Histogram of Vt measured from 20 devices for R-,G-,B-QLEDs respectively.

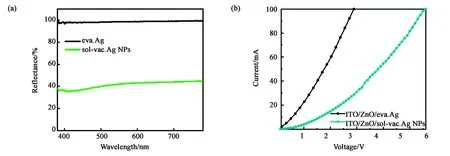

图6 (a)不同阴极薄膜反射率谱图;(b)不同电极的单电子I-V曲线。Fig.6 (a) Reflectance of different cathodes film; (b) I-V curves for electron-only device with different cathodes.

尽管新的干燥工艺使得全溶液加工QLEDs 的Vt与蒸镀Ag阴极QLEDs一致,但器件的ηCE和亮度均较差(表1)。如图6所示,sol-vac. Ag NPs薄膜反射率仅有eva. Ag薄膜的一半,而以sol-vac. Ag NPs为阴极的电子电流密度低于eva. Ag为阴极的器件。Chen等[30]在Ag NPs与功能层界面检测到大量的碳元素的存在,该工作指出界面残留的有机物会阻挡电子的传输。因此,全溶液加工器件性能的降低是由于Ag NPs薄膜的反射率低,减少了光输出,以及Ag NPs薄膜在退火过程中,脱落的有机配体残留在阴极界面处阻止电子传输,降低注入电子电流密度,减少激子形成数量导致。

4 结 论

本文探索了一种干燥工艺处理Ag NPs薄膜,制备了全溶液加工的QLEDs,使R-、G-、B-QLEDs的Vt分别为1.9,2.6,3.2 V,与蒸镀Ag器件基本一致。退火前的低真空干燥过程抑制了ZnO和Ag NPs界面处的共混形成,使得界面清晰,并在阴极中形成欧姆接触。尽管阴极势垒产生的具体物理机制尚不清楚,但实验证明了这种新工艺是抑制阴极额外势垒的形成,使得器件Vt较低的可行方式。本文首次具体研究了使用Ag NPs作为阴极,影响阴极界面势垒,器件Vt升高的原因,为以后低成本印刷制造发光显示器件提供了新的工艺思路。