一种降低时钟锁相环抖动的技术研究*

冯 景 ,张 繁

(1.亿嘉和科技股份有限公司,江苏 南京 210012;2.上海诺基亚贝尔股份有限公司,江苏 南京 210037)

0 引言

随着通信和计算机技术的发展,数据传输速率不断提高,高速SERDES(Serializer-Deserializer)数据率已经达到10Gbps、25Gbps 或以上,在这些高速SERDES 系统中,都需要锁相环为其提供工作时钟。在数据传输速率提高的同时,对锁相环时钟抖动的要求也越来越严格,锁相环输出很小的抖动都可能造成数据传输的错误。

1 PLL 在高速SERDES 的应用

高速SERDES 是点对点的串行通信技术,在发送端由Serializer(串行器)将多路并行信号转换成一路高速串行信号,经过传输介质,在接收端又由Deserializer(解串器)将一路高速串行信号重新转换成多路并行信号。高速SERDES 接口的芯片,将参考时钟通过锁相环倍频到和高速SERDES 数据率一致的时钟,此时钟作为发送时钟将数据通过串行器发送出去。从传输介质中传输过来的高速SERDES 数据进入解串器,通过数据时钟恢复电路提取出与高速SERDES 数据同源的时钟信号,用此时钟采样高速SERDES 数据将其转换成多路并行信号。

2 降低PLL 抖动的电路设计优化研究

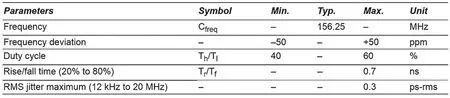

高速SERDES 串行器内部锁相环的参考时钟有严格的要求,速率越高的SERDES 接口芯片对参考时钟要求越高,特别是对RMS Jitter(随机抖动均方差)要求很高。图1 是某25Gbps 数据率SERDES 芯片的156.25MHz 参考时钟要求,156.25MHz 时钟是高速SERDES 源时钟,要求RMS Jitter 不超过0.3ps。

SERDES 芯片的156.25MHz 参考时钟要求为RMS Jitter 不超过0.3ps,上升时间、下降时间都不超过0.7ns,此方案可选用TI 公司的LMK03806 可编程超低抖动时钟发生器输出156.25MHz 参考时钟,锁相环LMK03806 芯片的时钟抖动可以达到0.15ps 范围内(12 kHz~20 MHz),上升时间、下降时间可达到0.2ns,满足图1 的高速SERDES 芯片要求。[1]

按照要求进行锁相环电路设计,但是最初使用锁相环LMK03806 芯片设计出来的156.25MHz 参考时钟,相噪分析仪测量RMS Jitter 值为0.6984ps,不能满足高速SERDES 芯片要求的不超过0.3ps,测试数据如图2 所示,锁相环LMK03806 芯片输出的156.25MHz 时钟相噪曲线包含大量的杂散噪声。

图1 SERDES 芯片的156.25MHz 参考时钟要求

图2 LMK03806 输出的156.25MHz 时钟RMS Jitter

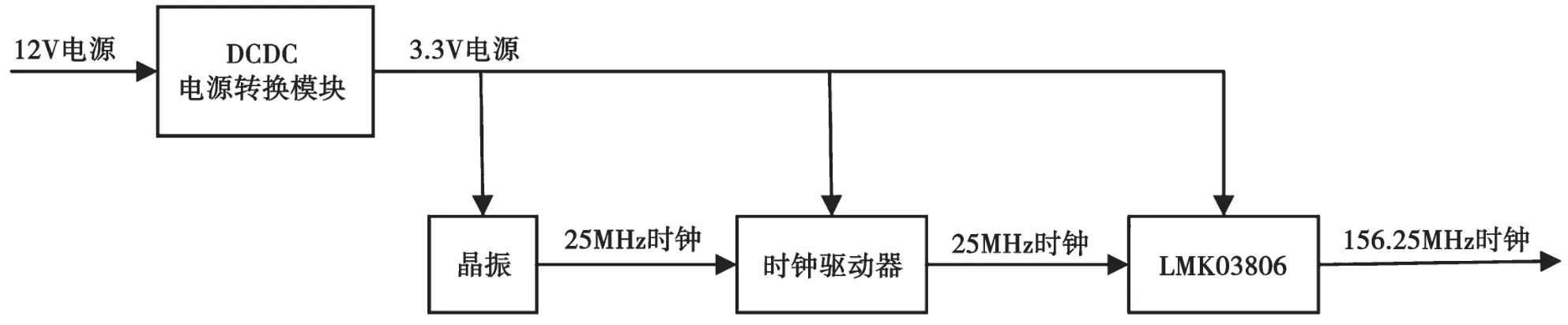

为了研究清楚杂散噪声的来源,让156.25MHz参考时钟满足高速SERDES 芯片要求,对锁相环LMK03806 电路进行分析。图2 锁相环输出的156.25MHz 时钟相噪曲线中杂散噪声主要分布在相噪谱带宽1Mhz 以内,这个范围正好和电源开关频率噪声的范围很近。检查最初设计的锁相环LMK03806 芯片电源和时钟硬件拓扑图,如图3 所示,晶振输出的25MHz 时钟,通过时钟驱动器分出一路25MHz 时钟作为锁相环LMK03806 芯片的输入时钟。晶振、时钟驱动器和锁相环LMK03806芯片的供电电源都是12V 转3.3V 的DCDC 电源转换模块直接供电。

图3 LMK03806 电源和时钟硬件拓扑图

12V 转3.3V 的DCDC 电源转换模块和晶振、时钟驱动器和锁相环虽然做了电源滤波处理[2],但是无法滤除电源纹波中的电源开关频率分量,电源开关频率分量再通过晶振、时钟驱动器、锁相环的供电接口耦合到时钟链路中,导致锁相环LMK03806 输出的156.25MHz 时钟RMS Jitter 超出指标要求。

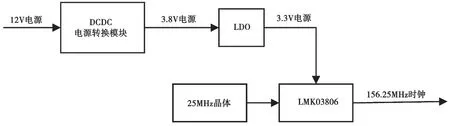

针对电源开关频率分量产生的噪声干扰,在硬件设计上进行优化,优化后的LMK03806 电源和时钟硬件拓扑图如图4 所示。DCDC 电源转换模块输出3.8V 电源,3.8V 电源再通过LDO(low dropout linear regulator,低压差线性稳压器)转出锁相环使用的3.3V 电源,将锁相环LMK03806 芯片使用单独的LDO 供电,对DCDC 电源转换模块进行隔离,避免电源开关频率噪声影响锁相环性能。同时,简化锁相环LMK03806 芯片输入时钟链路,使用无源晶体作为输入时钟,减少时钟驱动器,避免长走线和电源平面噪声影响输入时钟。[3]

图4 优化的LMK03806 电源和时钟硬件拓扑图

按照图4 电源和时钟硬件拓扑图优化后的时钟系统,使用相噪分析仪再测量锁相环LMK03806 芯片输出的156.25MHz 时钟RMS Jitter 值为0.3962ps,测试结果如图5 所示。但是锁相环LMK03806 芯片输出的156.25MHz 时钟RMS Jitter 值还是超出高速SERDES 芯片要求的0.3ps,不能满足设计要求。

为了进一步优化锁相环LMK03806 输出时钟的RMS Jitter 指标从锁相环原理进行分析。图6 是锁相环工作原理框图,由三部分组成:PFD(phase and frequency detector,鉴频鉴相器)、LPF(loop filter,环路滤波器)和VCO(voltage controlled oscillator,压控振荡器),加到鉴相器的两个信号的频率差为:Δω(t)=ωr-ωi;此时瞬时相位为:θe(t)=θr-θi,当环路锁定时,两个频率相等,相位差恒定,该稳态相位差经鉴相器转换为电流误差信号,通过LPF 后控制VCO;当两个频率不相等时,两个信号的相位差不是恒定值,鉴相器充电泵输出电流脉冲宽度也发生变化,这个变化经环路滤波后变为电压信号,从而控制VCO 频率改变,直到两者相同。[4][5]

图5 优化输入电源和时钟拓扑后156.25MHz 时钟RMS Jitter

图6 锁相环工作原理框图

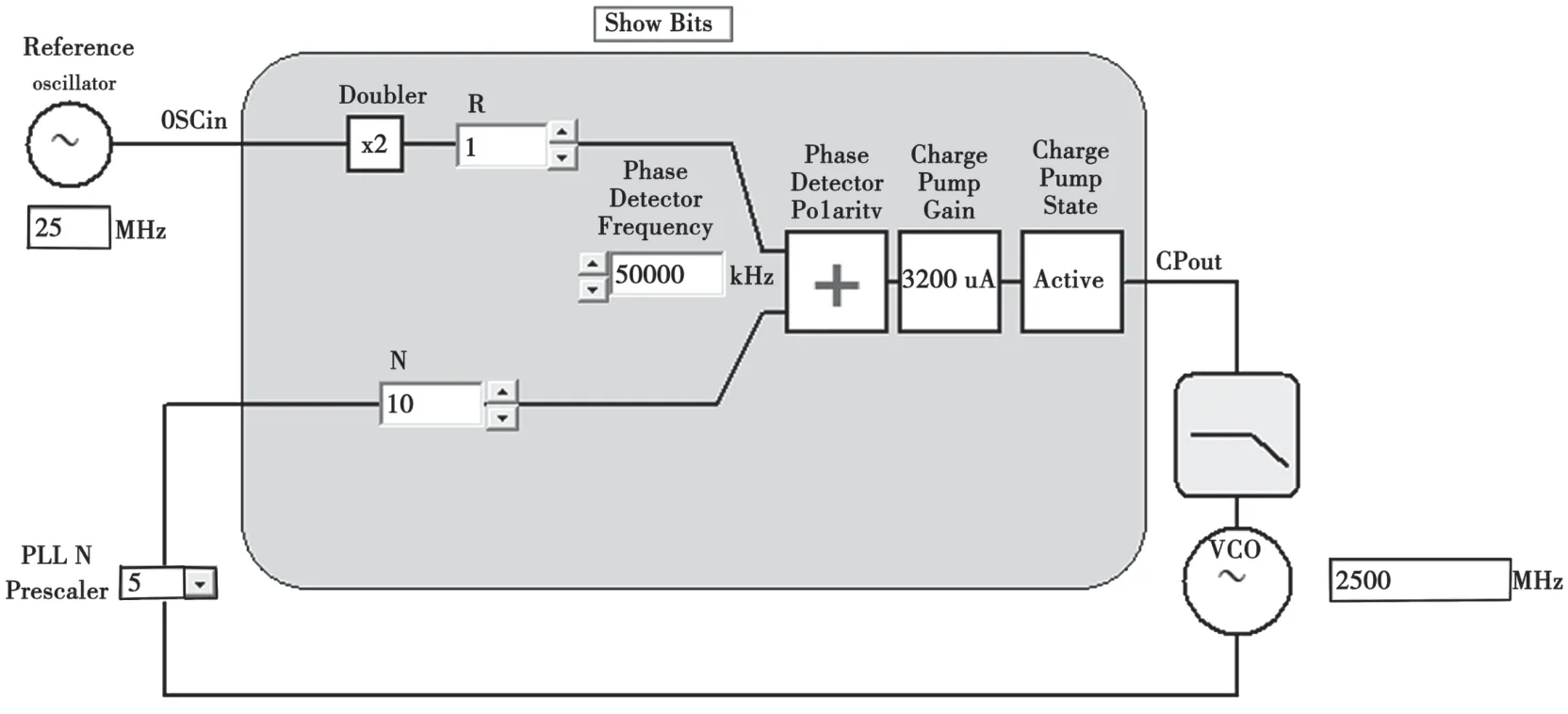

根据锁相环原理,检查LMK03806 的PLL 配置参数,如图7 所示。LMK03806 输入参考时钟设置为25Mhz,VCO 频点设置为2500MHz,鉴相器频率使用默认值12.5MHz,环路滤波参数选择默认配置,通过Divider 输出156.25Mhz 时钟。默认的鉴相器频率12.5MHz,是输入参考时钟25Mhz 频率的一半,而提高鉴相频率可以减少鉴相噪声,因此提高鉴相频率及减小N 值可以优化相噪,减少输出的156.25MHz 时钟RMS Jitter。

通过调整锁相环LMK03806 的PLL 配置参数,优化鉴相频率和N 值,并将输入参考时钟的Doubler 开启,使得输入频率提高一倍,再将鉴相频率提高到50MHz,锁相环LMK03806 详细配置如图8 所示。

3 时钟抖动测试结果

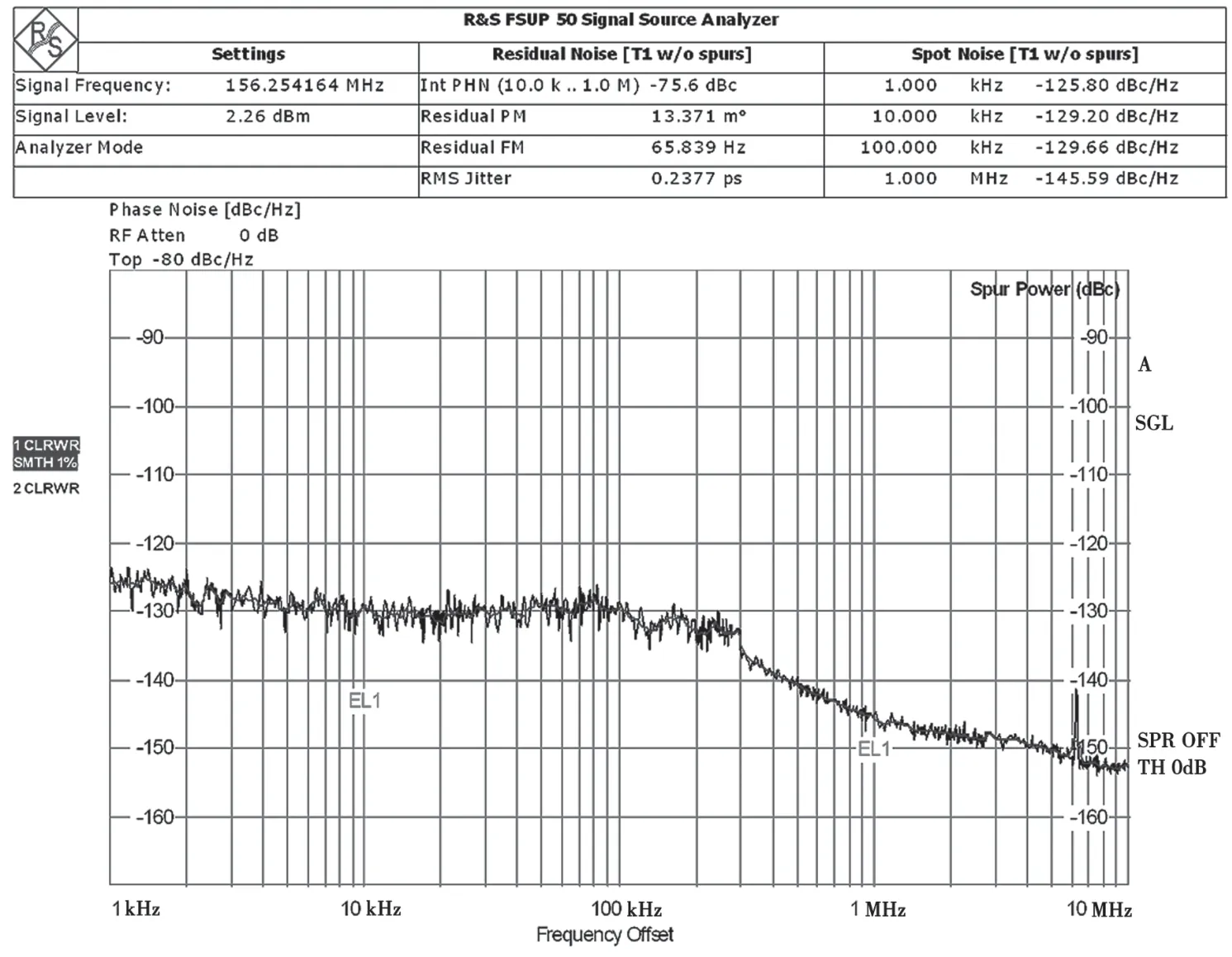

按照将锁相环LMK03806 PLL 优化后的配置,使用相噪分析仪再测量锁相环LMK03806 芯片输出的156.25MHz 时钟RMS Jitter 值为0.2377ps,测试结果如图9 所示,此时已经能够满足高速SERDES芯片要求的RMS Jitter 小于0.3ps 的要求。

图7 锁相环LMK03806 PLL 配置

图8 优化后的锁相环LMK03806 PLL 配置

图9 优化后的锁相环配置后156.25MHz 时钟RMS Jitter

4 结语

时钟设计是高速电路设计中最重要的环节,数据传输速率越高,对系统时钟的要求也越高。本文从时钟电路电源供电系统拓扑和锁相环参数优化,研究出降低时钟锁相环抖动方法,设计出高质量时钟电路,保证整个硬件系统稳定运行。