全数字双混频鉴相技术亚稳态抑制方法研究

崔广利,向渝,华宇

全数字双混频鉴相技术亚稳态抑制方法研究

崔广利1,2,3,4,向渝1,2,华宇1,2,3,4

(1. 中国科学院 国家授时中心,西安 710600;2. 中国科学院 精密导航定位与定时技术重点实验室,西安 710600;3. 中国科学院大学,北京 100049;4. 中国科学院大学 电子电气与通信工程学院,北京 101048)

全数字双混频鉴相技术(DDMTD)是一种高精度的相位检测技术,在White Rabbit中主要负责完成两路同周期信号的高精度相位差检测。在全数字双混频鉴相技术中,可以根据实际功能进行功能模块划分,信号采样放大模块中通常使用D触发器将输入信号的周期进行采样放大,但会存在明显的亚稳态问题。本文主要通过改进DDMTD中信号采样放大模块的设计方案来降低亚稳态对鉴相结果的影响,减小DDMTD相位差检测误差。实验采用40MHz信号进行测试实验,经过原方案与改进方案的结果比对可以得出改进方案对于信号边沿毛刺问题的改善有着明显效果。

White Rabbit;相位差检测;D触发器;触发器亚稳态

0 引言

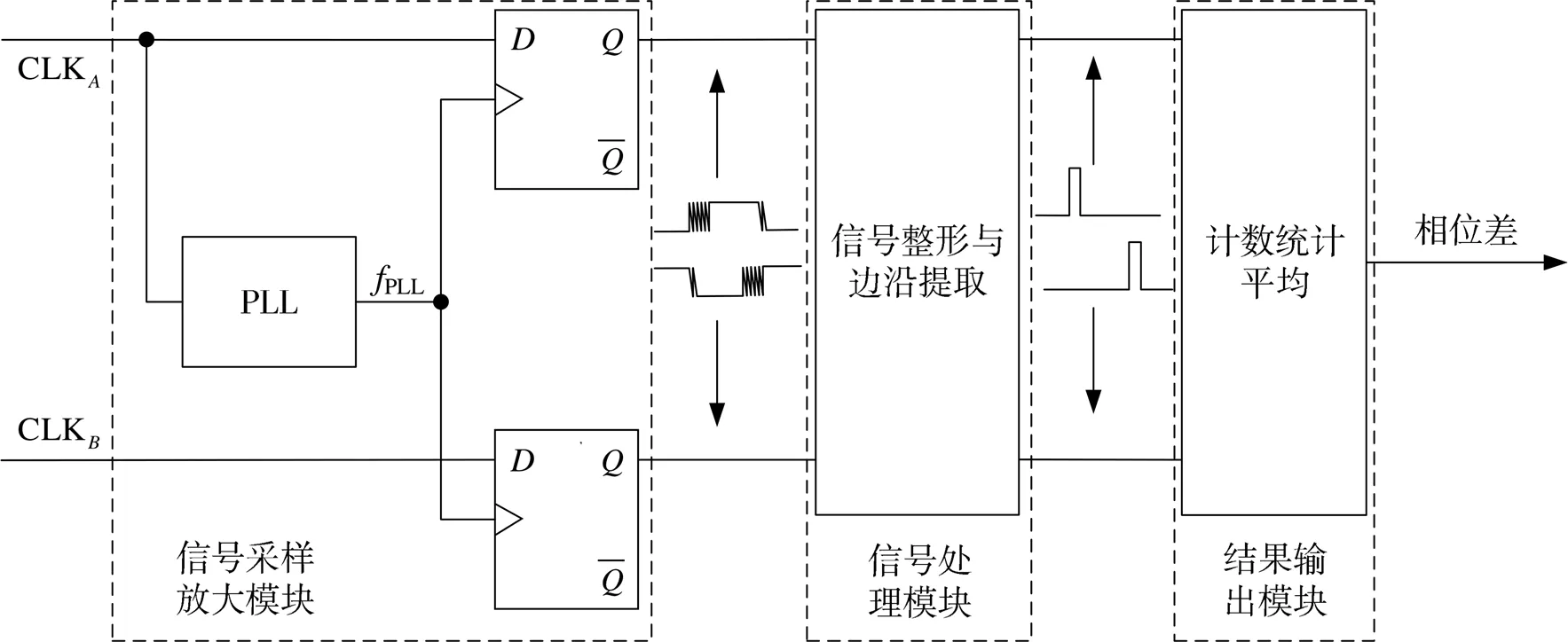

相位检测技术在电路设计中有着广泛的需求,对于不同的应用场景存在着不同的具体要求。目前,比较常见的相位检测技术包括:比相法、差拍法、频差倍增法和双混频时差法[1]。相关方法根据实际的应用场景、误差大小情况、对于参考频率源要求等方面都存在一些差异,但是上述方案存在无法集成在全数字方案中的缺点,无法应用于高度集成需求的全数字方案设计。全数字双混频鉴相技术(digital dual mixer time difference,DDMTD)[2]是一种全数字方案设计的相位检测技术,其在White Rabbit技术中占据着重要地位。White Rabbit是一种高精度的时钟同步技术,可以实现亚纳秒级别的时间同步,主要综合了同步以太技术、精密时间同步协议、全数字双混频鉴相技术。全数字双混频鉴相技术是决定White Rabbit是否能够实现亚纳秒时钟同步的关键部分之一[3],在White Rabbit中发挥着不可替代的作用。全数字双混频鉴相技术根据实际功能主要分为三大功能模块:信号采样放大模块、信号处理模块、结果输出模块。其中,在信号采样放大功能模块中使用D触发器完成信号采样放大的功能,然而当D触发器输入信号与时钟信号频率特别接近的时候,放大输出的信号会存在明显的亚稳态问题[4],影响相位检测结果的精度与准确度。因此,本文提出了全数字双混频鉴相技术改进方法,试图解决亚稳态问题,进而为实现White Rabbit的全数字设计的改进奠定基础。

1 全数字双混频鉴相技术原理

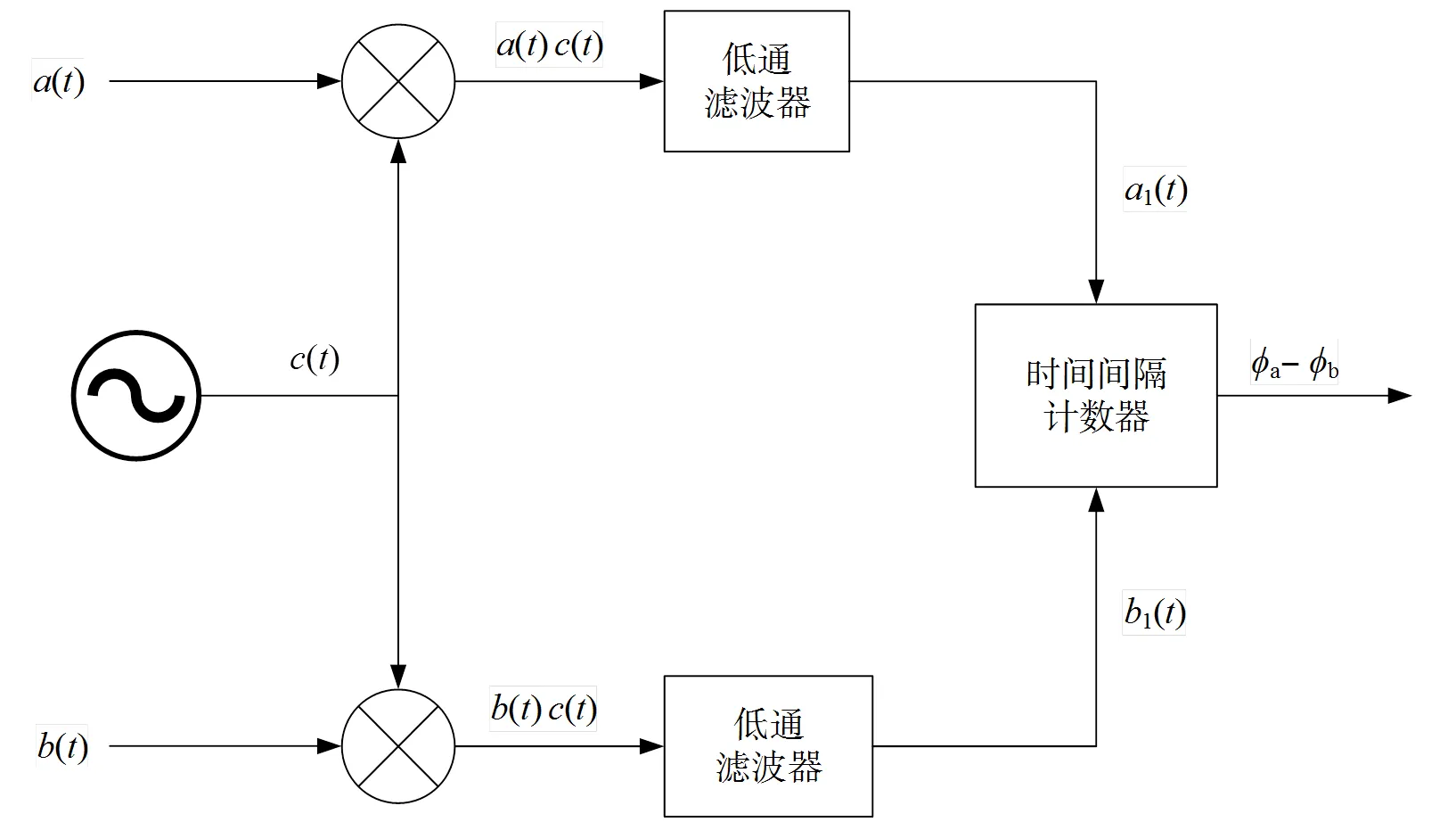

全数字双混频鉴相技术是基于模拟双混频时差法改进而得来的,传统的模拟方案中通过将高频信号降频,信号降频之后会保证待测信号与参考信号之间的相位差信息不发生改变,对降频之后的参考信号与待测信号进行拍频便可获得这两路信号的相位差测量值[5],其基本框图如图1所示[6]。

图1 双混频时差法技术框图

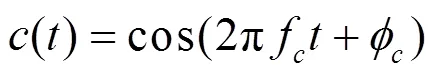

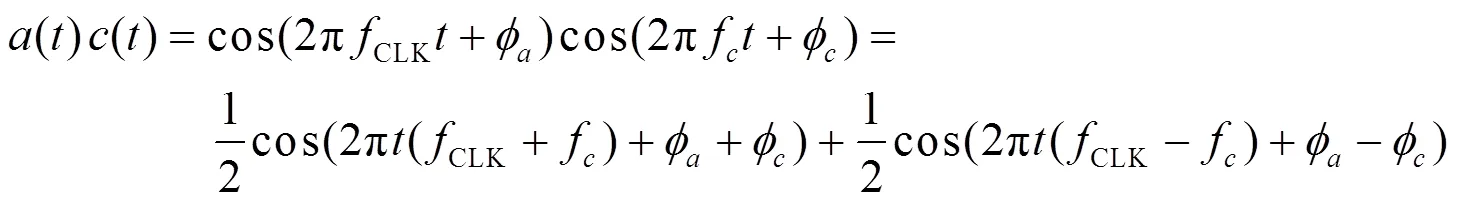

图1中,

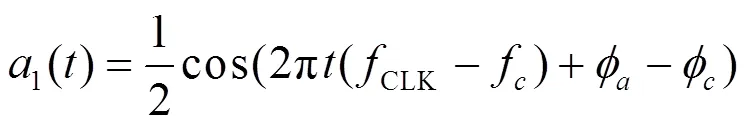

经过低通滤波器之后可得:

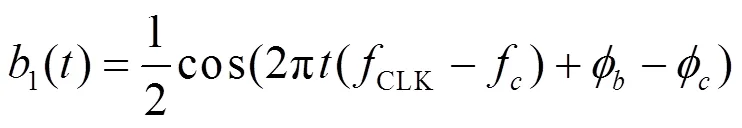

同理,可知:

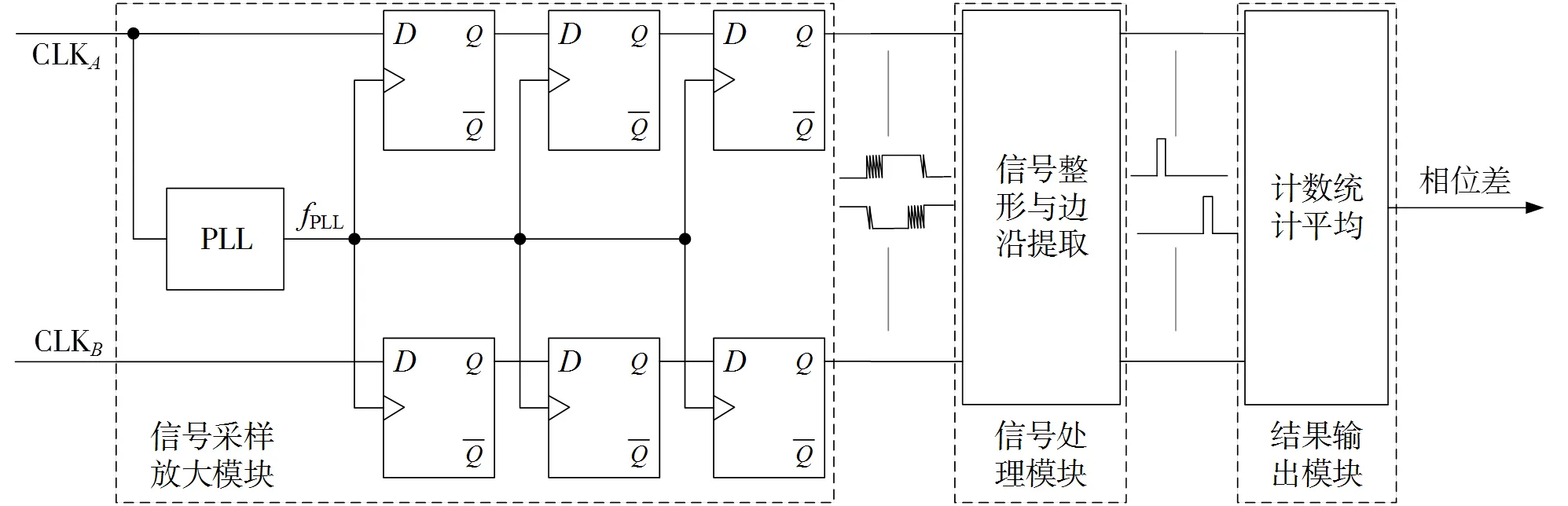

White Rabbit是一种高精度的时钟同步技术,通过FPGA(field programmable gate array)完整实现核心功能,具有精度高、集成度高并且成本低的特点[9]。作为关键技术之一的全数字双混频鉴相技术需要完整地集成在FPGA中,此时相位检测技术需要面对的信号是数字信号,而且要求具有较高的集成度,所以模拟相位差检测方案没有办法使用,需要将模拟方案改为全数字方案才可以作为White Rabbit中相位检测技术进行使用[10]。全数字双混频鉴相技术的基本原理和模拟混频鉴相技术基本原理是一样的:在信号采样放大模块中将两路数字信号都按照同样的倍数进行采样放大,由于两个数字信号的相位差也进行同比例放大,此时只需要测量出放大之后两个数字信号的相位差,然后同比例缩小,即可求出两路原始数字信号的实际相位差[11],其基本的逻辑框图如图2所示[9]。

图2 全数字双混频鉴相技术基本框图

在鼓励相关行业企业参与社区教育的同时,其他社会机构组织也应响应号召自觉参与,充分发挥机构特征与活动的联动作用,利用政府的优惠政策、资金配给、推介平台,与社区教育中心共建一批集教学、培训、体验为一体的社区教育示范基地,培育一批贴近实际、贴近生活、贴近群众的社区教育特色品牌,切实利用社区教育“全员、全程、全面”特征实现非物质文化遗产的传承与创新,促进区域文化和社会经济的全方位发展。

2 全数字双混频鉴相技术误差分析

全数字双混频鉴相技术采用全数字结构,其在相位检测的过程中会存在诸多干扰,使得测量结果与实际值之间存在较大的误差。对于全数字双混频鉴相技术中会对测试结果产生误差的部分进行了如下分析:

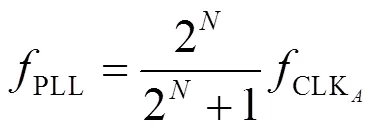

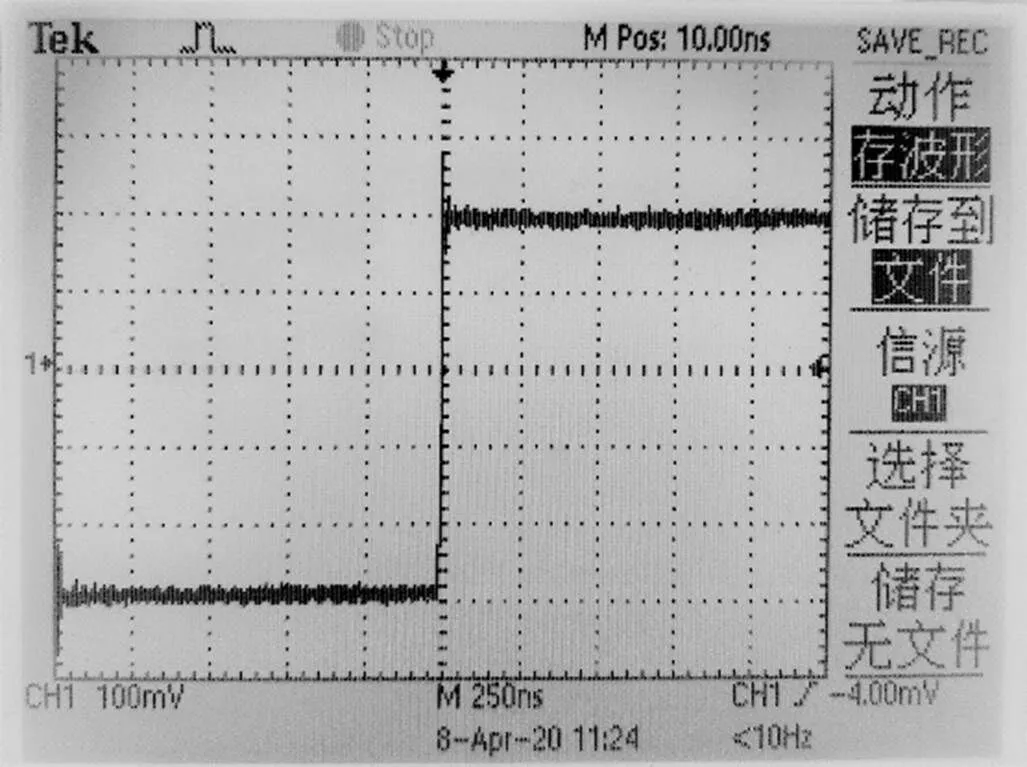

① 信号采样放大模块:该模块采用D触发器作为信号采样放大的关键结构,并且两个D触发器的时钟信号频率十分接近其输入信号频率,这也就会导致两个D触发器的输出信号因为触发器亚稳态问题造成放大之后的信号边沿存在很多的毛刺,而对于该结构中亚稳态问题是导致毛刺过多的主要原因之一[12]。触发器亚稳态的出现是一种概率问题,亚稳态窗的宽度随宽度增大而概率降低。而对于毛刺输出的问题,全数字双混频鉴相技术主要是由触发器亚稳态影响而导致,输出信号存在较多的毛刺会影响信号处理模块对于信号边沿提取结果的稳定度,影响相位差测量结果。为了验证该结论,针对信号采样放大模块部分进行了实际的测试实验,实际的输出信号情况如图3所示。

图3 原始方案输出信号

通过实际测试可以看出原始方案的信号采样放大模块输出信号存在着很明显的毛刺问题,该问题会直接影响信号边沿的提取结果,导致最终相位差测试结果与实际结果之间存在较大偏差。

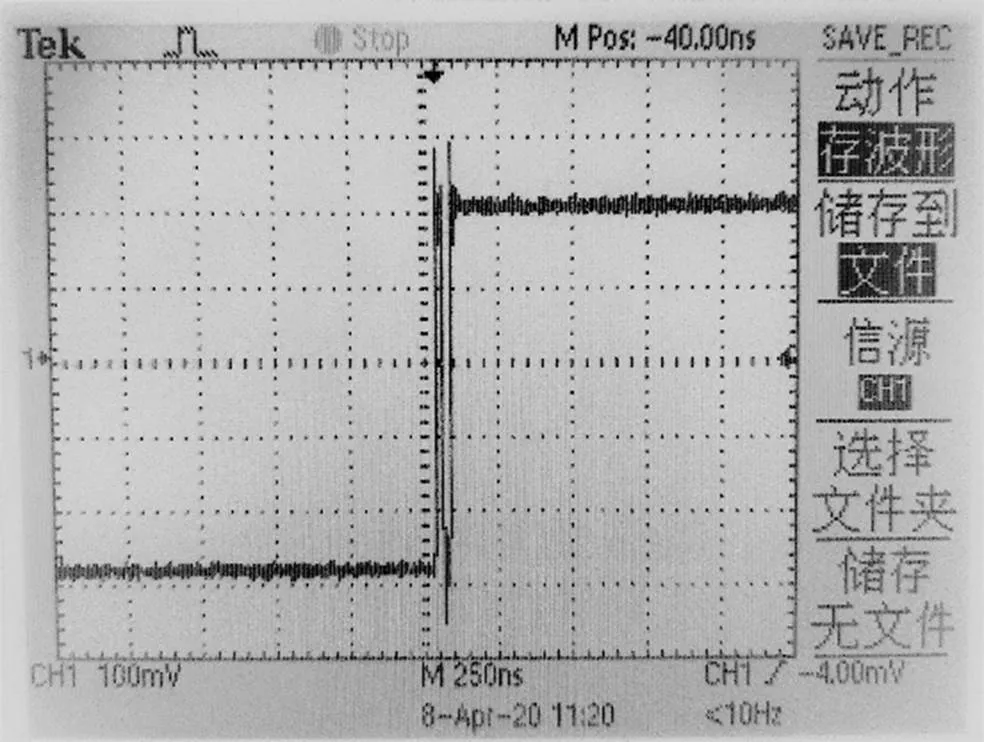

② 信号处理模块:在信号处理模块中采用了Bit Value Median(后续简称:BVM)算法来实现信号边沿的确定。BVM算法的实现原理示意图[9]如图4所示:

高电平时间(t

3 全数字双混频鉴相技术改进设计

毛刺产生的最主要原因之一是D触发器亚稳态问题。对于解决触发器亚稳态问题,通常采用如下方法:采用亚稳态时间窗会比较窄的快速触发器;采用同步多级触发器级联方式;采用性能更加优秀的触发器;降低采样频率;时钟边沿变化速度快的输入时钟信号[4]。但对于纯数字方案设计的全数字双混频鉴相技术而言,D触发器采用的是FPGA的core,而且时钟频率在一些应用场景之中是固定的,因此只有采用D触发器多级级联的方式是可行的。

图5 全数字双混频鉴相技术改进设计逻辑框图

在改进之后的方案中,输入信号与时钟信号经过第一级的触发器之后,由于时钟信号与输入信号频率十分相近,会导致输出信号触发器亚稳态问题很明显,这对于信号上升边沿的确定的准确性有着严重的影响。经过两级D触发器进行缓存,输出信号的触发器亚稳态问题会得到改善,便于通过算法对输出信号的上升边沿进行确定,对于最后相位差检测结果的误差减小有帮助。

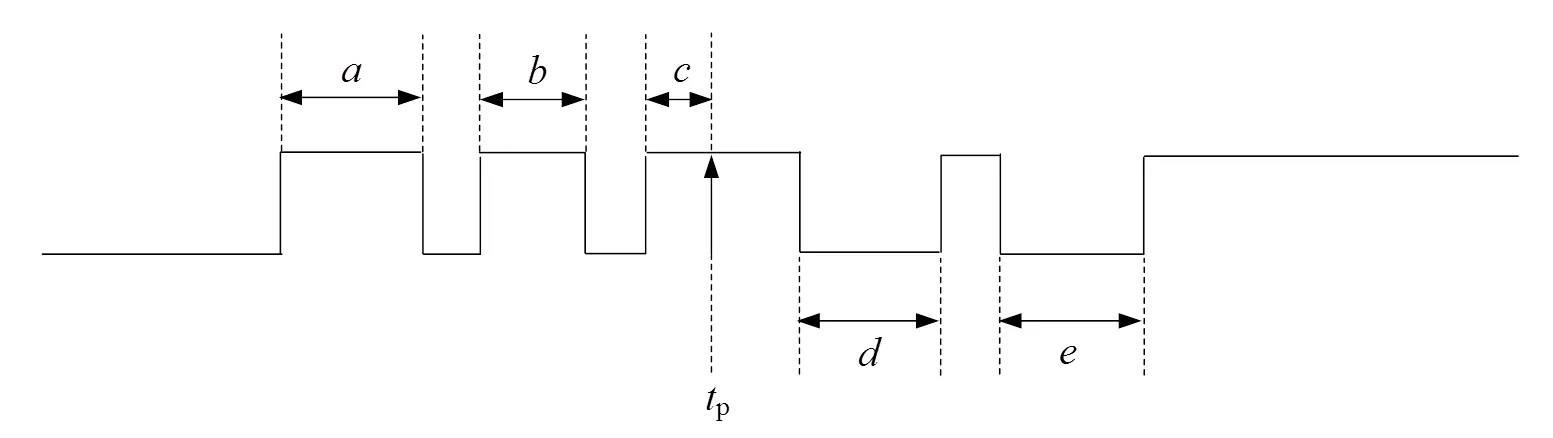

在改进设计中,针对信号采样放大模块进行了改进,在原方案基础上增加了两级D触发器。为了验证该设计的有效性,针对该模块进行了实际的测试实验,实验条件与原方案的实验条件保持一致,测试结果如图6所示。

图6 改进方案输出信号

通过测试结果可以看出,信号放大模块在增加了两级D触发器之后,采样放大信号的输出情况明显得到了改善,改进方案输出信号毛刺数量明显少于原方案输出信号毛刺数量,有利于后续信号边沿提取的稳定性。

4 测试实验与结果分析

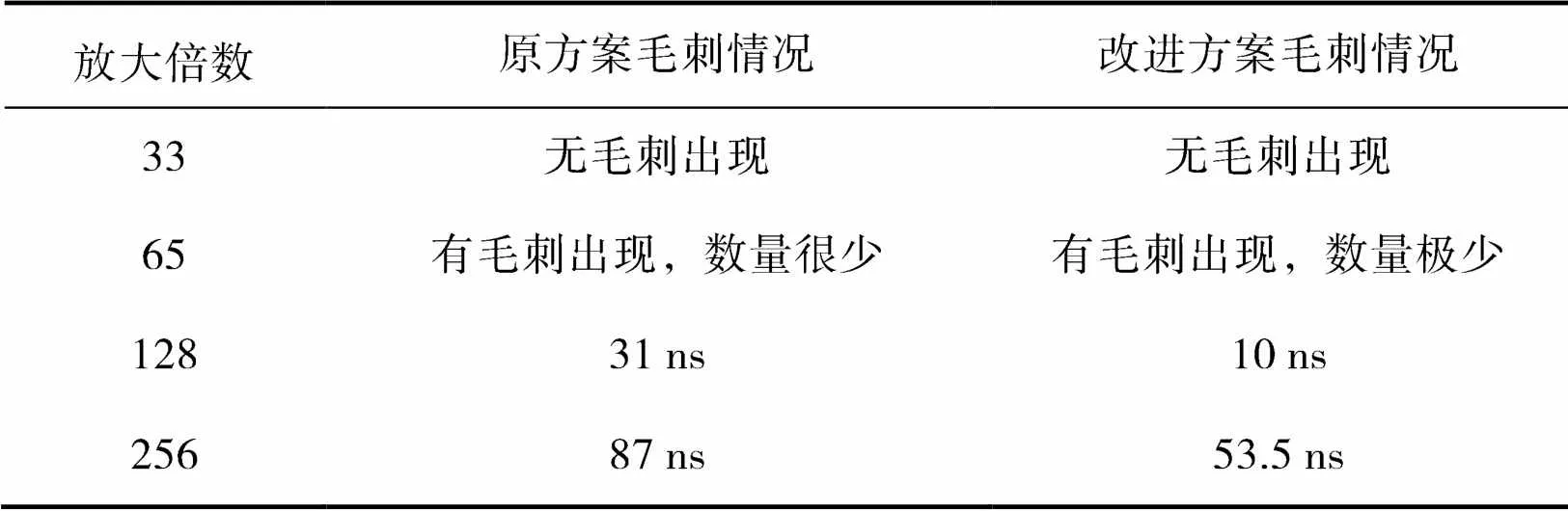

表1 不同放大倍数毛刺情况测试

在该测试实验中,使用FPGA内部的PLL生成D触发器的时钟信号,但是由于平台性能限制,在PLL中设置放大倍数的时候存在倍数无法除尽的情况,导致PLL无法按照设置倍数输出特定频率的信号。因此,在本次实验中仅对40 MHz信号进行了测试分析,并未对White Rabbit中使用的125 MHz信号进行实际的测试实验。

在40 MHz输入信号的条件下,进行了多次的测试实验。通过表1的结果显示,在放大倍数设置为256时,采用原方案的单D触发器进行信号采样放大的方案毛刺的宽度可以达到87 ns,而改进方案中,增加了两级D触发器做缓存的结构,多次的测量结果显示输出信号的上升边沿亚稳态影响明显减小,亚毛刺的宽度可以减少为53.5ns;在放大倍数设置为128时,采用原方案的单D触发器进行信号采样放大的方案毛刺的宽度可以达到31 ns,而改进方案的输出结果为10 ns。通过测试结果的比对,可以得出如下结论:

① 放大倍数越大,毛刺出现的概率会越大,并且毛刺宽度也会越大;

② 改进方案对于信号亚稳态状况的改善是有效的,增加两级D触发器进行缓存的处理方案可以有效地减小毛刺宽度;

由此可见,在全数字双混频鉴相技术中,采用两级D触发器缓存的方案可以改善输出信号的亚稳态问题。测试实验中使用的是40 MHz的时钟信号进行的,结果显示可以有效地降低亚稳态问题,而对于White Rabbit使用的125 MHz信号,该方案也有同样的效果。对于全数字双混频鉴相技术而言,采样放大模块输出信号的毛刺问题单单采用如上述的改进方案并不能够完全的解决,这就需要信号处理模块对毛刺进行处理并进行边沿的提取工作。这里对毛刺处理目的是减小毛刺宽度,使信号边沿在提取的时候结果更加的稳定,使相位检测结果更加的准确。

5 结语

在全数字双混频鉴相技术中,改进方案采用两级D触发器缓存来抑制触发器亚稳态问题,通过实际的测试实验可以得知该方法具有显著的效果。测试实验中使用40 MHz时钟信号频率,测试结果显示改进方案可以明显减小亚稳态导致的毛刺过宽的问题,有利于信号处理模块中边沿提取结果的稳定性。

[1] 何慧征. 数字式双混频时差测量系统的研究设计与仿真实现[D]. 北京: 北京工业大学, 2014.

[2] MOREIRA P, ALVAREZ P, SERRANO J, et al. Digital dual mixer time difference for Sub-Nanosecond time synchronization in Ethernet[J]. 2010 IEEE International Frequency Control Symposium, Newport Beach: IEEE, 2010: 449-453.

[3] DANILUK G. White Rabbit PTP Core the sub-nanosecond time synchronization over Ethernet[D]. Warsaw: Warsaw University of Technology, 2012: 9-11.

[4] 霍华德 J, 马丁 G. 高速数字设计[M]. 沈立, 朱来文, 陈宏伟, 等, 译. 北京: 电子工业出版社, 2002.

[5] 胡锦伦. 一种双混频时差测量系统[J]. 计量学报, 1982, 3(3): 223-226.

[6] 徐超, 刘军良, 胡永辉. 双混频时差测量系统的误差分析与试验研究[J]. 时间频率学报, 2018, 41(3): 206-213.

[7] 闫菲菲, 马红皎, 何在民, 等. 基于FPGA和TDC芯片的高精度时间间隔计数器研制[J]. 时间频率学报, 2019, 42(1): 33-42.

[8] 刘正阳, 刘音华, 李孝辉. 基于FPGA的TDC系统偏差修正方法的研究[J]. 时间频率学报, 2019, 42(2): 142-150.

[9] WLOSTOWSKI T. Precise time and frequency transfer in a White Rabbit network[D]. Poland: Warsaw University of Technology, 2011.

[10] LIPIŃSKI M, WŁOSTOWSKI T, SERRANO J, et al. White rabbit: a PTP application for robust sub-nanosecond synchronization [C]//2011 IEEE International Symposium on Precision Clock Synchronization for Measurement, Control and Communication, Munich, Germany: IEEE, 2011: 25-30.

[11] 潘维斌. LHAASO实验高精度时间测量系统研究[D]. 北京: 清华大学, 2014.

[12] 汪路元. FPGA设计中的亚稳态及其缓解措施[J]. 电子技术应用, 2012, 38(8): 13-15+19.

[13] ANONYMOUS. Altera Corporation; Altera’s embedded systems development Kit accelerates the creation of cyclone III FPGA- based embedded designs[J]. Robotics & Machine Learning, 2009.

Research on meta-stable suppression method of digital dual mixer time difference

CUI Guang-li1,2,3,4, XIANG Yu1,2, HUA Yu1,2,3,4

(1. National Time Service Center, Chinese Academy of Sciences, Xi’an 710600, China;2. Key Laboratory of Precise Positioning and Timing Technology, Chinese Academy of Sciences, Xi’an 710600, China;3. University of Chinese Academy of Sciences, Beijing 100049, China;4. School of Electronics and Communication Engineering, University of Chinese Academy of Sciences, Beijing 101048, China)

Digital dual mixer time difference(DDMTD) is a high-precision phase detection technology. In White Rabbit, it is mainly responsible for the high-precision phase difference detection of two same-cycle signals. In the DDMTD, function modules can be divided according to the actual functions. The signal sampling amplifier module usually uses a D flip-flop to sample and amplify the period of the input signal, but there will be obvious metastable problems. This paper mainly improves the design scheme of the signal sampling and amplifying module in DDMTD to reduce the effect of metastable state on the phase discrimination result and reduce the detection error of DDMTD phase difference. Our experiment uses a 40 MHz signal for the test experiment. By comparing the results of the original scheme and the improved scheme, we conclude that the improved scheme has a significant effect on the improvement of the signal edge glitch.

White Rabbit; time difference detect; D flip-flop; trigger metastable

10.13875/j.issn.1674-0637.2021-01-0010-07

崔广利, 向渝, 华宇. 全数字双混频鉴相技术亚稳态抑制方法研究[J]. 时间频率学报, 2021, 44(1): 10-16.

2020-05-15;

2020-06-19

中国科学院国家授时中心“青年创新人才”资助项目(国授发字〔2017〕48号)