基于负反馈技术的嵌套式直流失调消除电路*

张芳玲 ,雷倩倩 ,张旭东 ,李 弦 ,李连碧

(1.西安工程大学 理学院,陕西 西安 710000;2.深圳市纽瑞芯科技有限公司,广东 深圳 518000)

0 引言

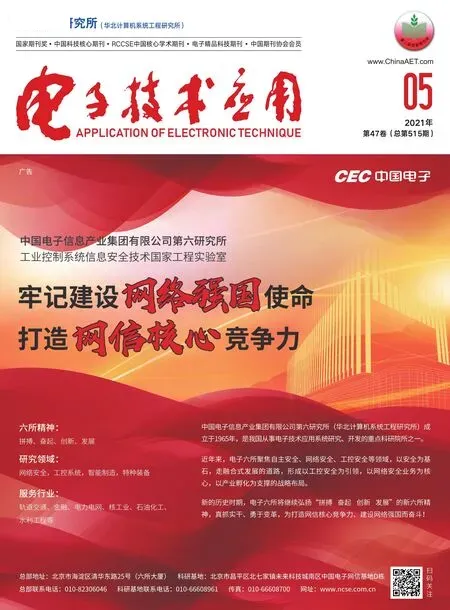

随着可编程增益放大器(Programmable Gain Amplifier,PGA)放大倍数的增大,尤其在给接收链路提供较大增益时[1-3],直流失调的问题就越来越严重,使得下一级电路处于饱和状态。因此,必须使用直流失调消除电路来解决这一问题。常见的直流失调消除技术有四种,一是交流耦合法[4-5],为了得到低的高通截止频率,需要很大的电阻电容,占用面积大,不易集成;二是数字消除技术[6-8]具有极低的高通截止频率,分辨率低,需要额外的量化器和数模转换器,电路实现较复杂;三是前馈消除技术[9-10],由于器件的不匹配等因素,两路的增益不完全相同且这种方法功耗较大;四是直流负反馈消除方法[11-15],这种方法解决了交流耦合所需要的大电容和数字消除电路的复杂性以及前馈消除方法存在的问题。直流负反馈消除技术如图1所示,电阻R、电容C和放大器B组成反馈通路,将输出端out检测到的直流失调信号转换成电压或电流反馈到输入端in,从而消除直流失调。

图1 直流负反馈环路

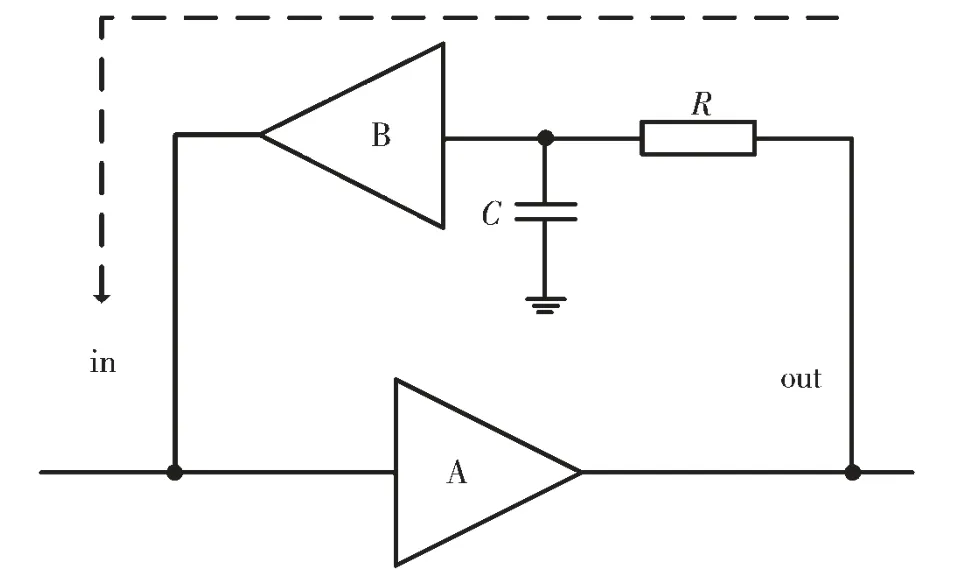

在PGA链路中,通常采用多级级联的方式实现大的可调增益范围。对于多级级联的PGA链路,采用直流负反馈技术消除直流失调的连接方式有两种,如图2所示,图2(a)中的每一级PGA电路都有一个DCOC环路,而图2(b)图中采用多级共用一个DCOC环路的连接方式。图2(a)中每一级DCOC都有一个反馈运放OP,增大了电路的功耗[14],图2(b)中单级DCOC可以简化电路设计和功耗[10],但为了达到与图2(a)相同的直流失调消除效果,需要更大的面积。针对以上两种连接方式存在的不足之处,本文提出一种改进的直流失调消除方法,采用了一种嵌套式电路连接方式,将多个独立的反馈环路通过共用RC组成的低通滤波器和运放OP,再分别通过反馈电阻反馈到每级PGA中,从而减小电路功耗和面积。

图2 采用直流负反馈技术消除直流失调连接方式

1 基于负反馈的嵌套式直流失调电路

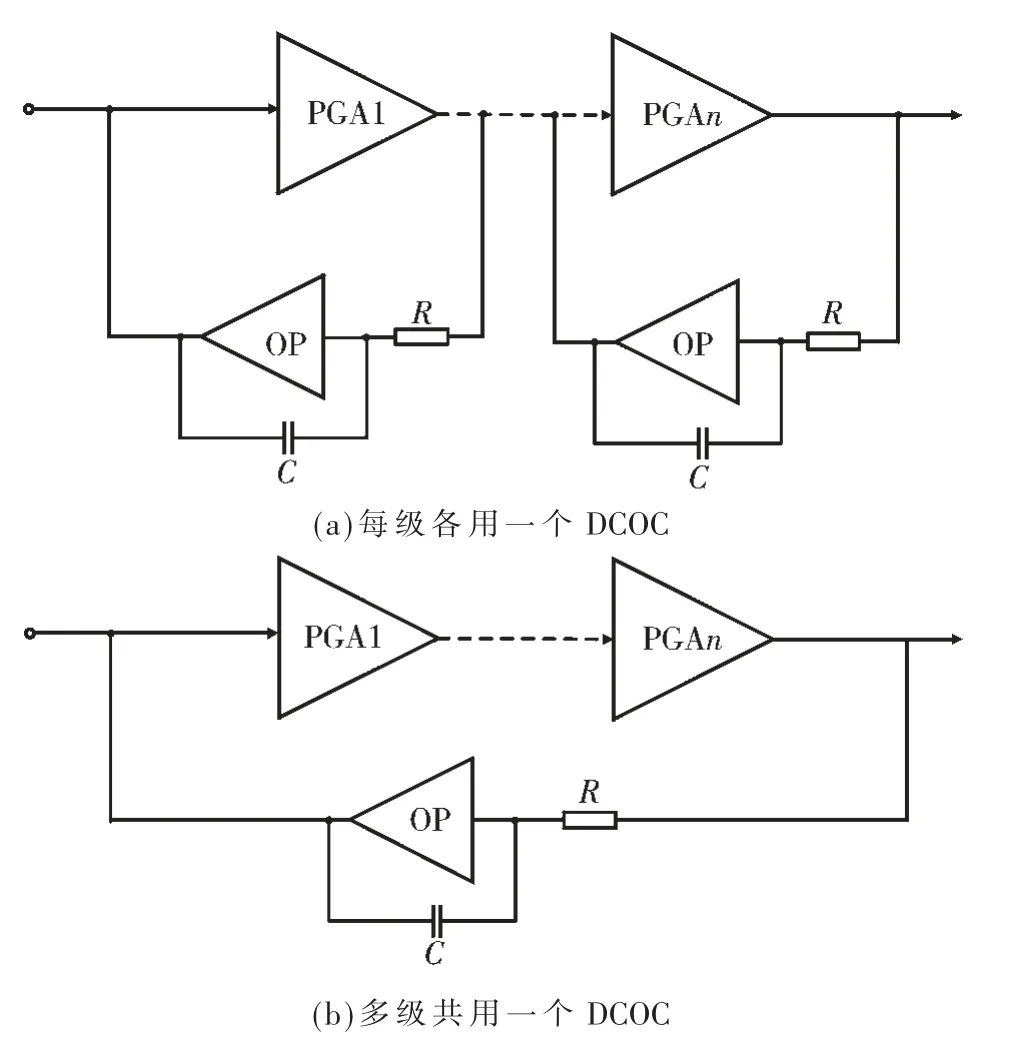

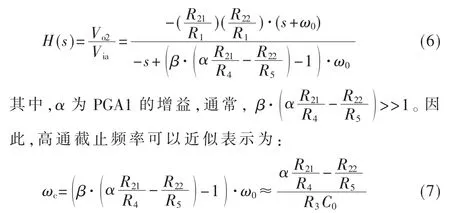

嵌套式DCOC反馈方式的PGA链路如图3所示,PGA电路由两级PGA1、PGA2构成,每级PGA均采用开关电阻反馈网络的结构,PGA1增益变化为0~26 dB,第二级增益从26 dB变化到52 dB,增益步长为2 dB,两级级联实现52 dB的增益变化范围。图3中下方虚线部分为DCOC环路,采用嵌套式反馈的连接方式,将输出节点Vo2的失调电压通过电阻R3和密勒等效电容C1组成的低通滤波器检测,再由运放β 进行放大,一部分通过反馈环路1(FL1),即通过电阻R5转换为反馈电流,注入到第二级的输入端;另外一部分通过反馈环路2(FL2)反馈到第一级PGA的输入端。两级共用R3、C0和运算放大器β,可变电阻R3实现不同高通截止频率的切换。C1为密勒等效电容,等效电容C1近似为密勒补偿电容C0和运放增益β 的乘积。

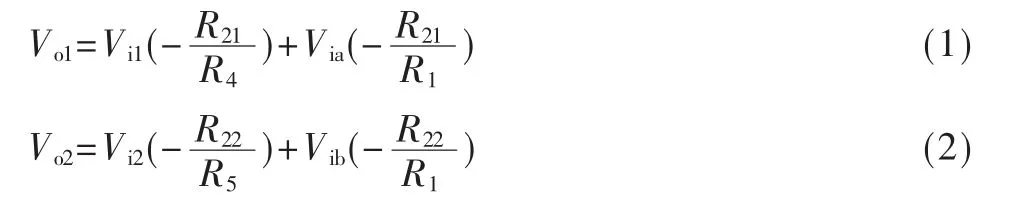

图3中Via、Vib分别为第一级和第二级的输入信号,Vi1、Vi2是第一级和第二级的反馈信号,Vo1、Vo2为第一级和第二级的输出信号,环路FL2和FL1的电压关系式可分别表示为:

图3 新型嵌套式DCOC环路

假设反馈运放β 是单级点系统,则:

由图可知:

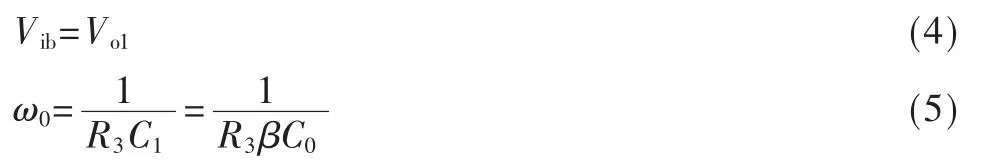

β 为DCOC中运放的增益,ω0为低通滤波器的截止频率。PGA和DCOC环路的传输函数为:

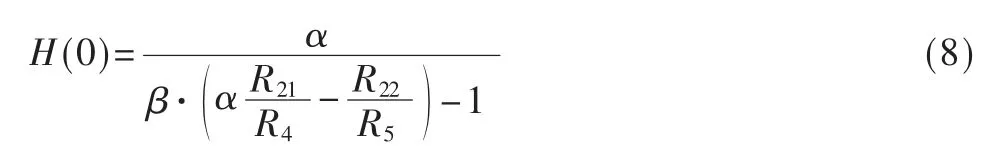

由式(7)可知,高通截止频率ωc的高低与电阻R21(R22)、R3、R4,R5和电容C0的大小有关。对于PGA1,高通截止频率与α 和R21/R4的值有关;PGA2的高通截止频率与R22/R5的值有关,保持α(R21/R4)和R22/R5电阻比值一定时,高通截止频率保持恒定,即高通截止频率不随PGA增益的变化而变化。

由传输函数可知,PGA的直流抑制度可表示为:

2 仿真结果

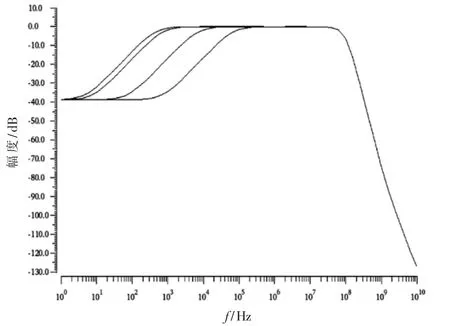

基于UMC 40 nm CMOS工艺,对带有嵌套式DCOC反馈方法的PGA链路进行仿真验证。图4为DCOC的高通截止频率为10 kHz时,PGA不同增益值的频率响应曲线图,PGA增益调节范围为0 dB~52 dB,步长为2 dB,增益误差小于0.2 dB,1 dB带宽大于20 MHz。此时α(R21/R4)和R22/R5电阻比值一定,即高通截止频率恒定,不随PGA增益的变化而变化,恒为10 kHz,DCOC环路的相对抑制度也是恒定的,大于50 dB。

图4 PGA频率响应曲线

图5为增益在0 dB时,调节电阻R3,反馈环路的高通截止频率分别为0.5 kHz、1 kHz、10 kHz、100 kHz时的频率响应曲线。高通截止频率随信号变化可以进行切换,这样可以同时满足信号完整性和直流失调稳定时间的要求。

图5 相同增益下不同高通截止频率

图6为PGA增益为0 dB时,输入端加110 mV失调电压的矫正过程,可以看出,经过DCOC环路矫正后,输出端的直流失调电压小于1 mV。

图6 0 dB时失调矫正过程

表1为DCOC的高通截止频率为10 kHz,相对抑制度为50 dB时,采用负反馈结构,三种DCOC环路连接方式的比较。从表可以看出,对于两级级联的PGA链路来说,本文所提出的嵌套式反馈方法与文献[6]、[9]中的方法相比,在优化功耗的同时,可使DCOC环路的面积减小近一半。

表1 DCOC电路中参数的比较

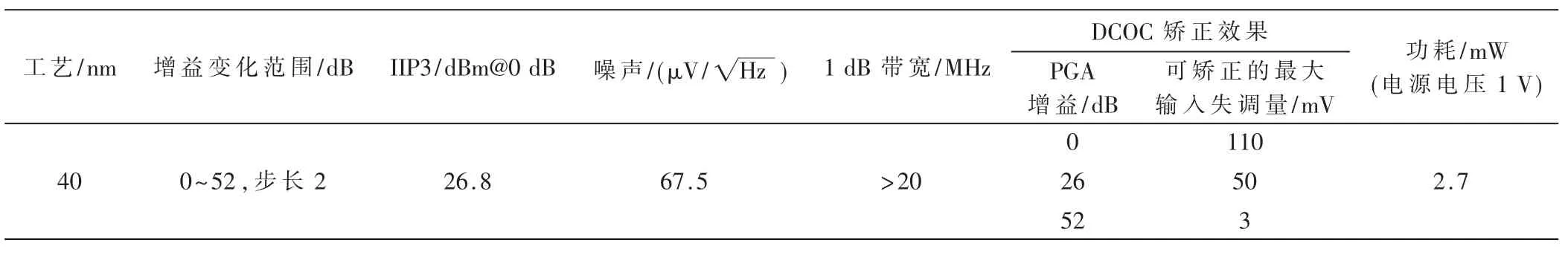

表2 PGA电路性能指标

3 结论

本文在UMC 40 nm CMOS工艺下设计了一种带有DCOC电路的PGA,DCOC环路采用一种嵌套式电路连接方式,可减小电路功耗和面积。仿真结果表明,PGA的增益变化范围为0~52 dB,步长2 dB,增益误差小于0.2 dB,1 dB带宽大于20 MHz,0 dB下IIP3的值为26.8 dBm,噪声为67.5 μV/√Hz。加入DCOC环路后,直流失调能够很好地被抑制,整个电路在1 V电源电压下功耗为2.7 mW。