一种FPGA芯片JTAG接口切换电路的设计

徐方晨 刘陈

【摘要】 本文提供了一种FPGA芯片JTAG接口切换电路的设计实现方法,通过该切换电路,依据实际使用过程中的不同需要,可以将JTAG口从要求的连接器引出,实现了稳定、便捷,在复杂结构的嵌入式系统设计中,能满足多层次的、广泛的应用电路要求,具有重要的实际应用价值。

【关键字】 FPGA JTAG接口 驱动芯片 反向器

引言:

在20世纪80年代,Xilinx公司首次研制出第一款FPGA芯片,其特殊的性能使其在编程和资源配置方面具有很大的灵活性[1]。随着数字化程度的提高,FPGA以其通用性强、开发周期短、集成度高等特点,得到了越来越广泛的应用。面对复杂的FPGA电路设计时,FPGA芯片的调试手段不仅关系到芯片的质量,还影响到研发的效率,因此在FPGA芯片的使用过程中,如何更有效、方便、可靠地使用调试手段对FPGA进行在线仿真调试和代码下载等,也吸引了使用者更多的关注[2]。

一、设计背景

FPGA是易失性器件,即当使用者把电源关闭时它不能保存数据,我们一般使用PROM作为存储介质长期写入并保存数据。FPGA芯片电路常用的配置模式主要有主串模式、从串模式、SelectMAP模式、JTAG调试模式等,本文主要分析最常用的JTAG调试模式。

JTAG接口是一个业界标准,主要用于芯片测试、调试、配置、下载等功能,使用IEEE Standard 1149.1聯合边界扫描接口引脚[3]。JTAG最初用于芯片功能的测试,其工作原理是在器件内部定义一个测试访问端口(Test Access Port,TAP),通过专用的JTAG测试工具对内部节点进行测试和调试,TAP是一个通用的接口,外部控制器通过TAP可以访问芯片提供的所有数据寄存器和指令寄存器。现在对FPGA的开发过程中,JTAG接口常用于对FPGA进行在线仿真调试和逻辑加载。

传统的应用模式中,将每个FPGA对应的JTAG接口引出,通过固定的JTAG口连接器对每个FPGA进行调试,该设计方法的特点是,调试过程简单方便,同事PCB设计阶段容易实现整齐的走线。随着应用的越来越广泛深入,尤其是在现代的嵌入式系统设计中,考虑到散热设计以及其他系统结构设计要求,会出现很多种特殊要求的应用情况。

以下两种应用模式是在工程实践过程中遇到的两种情况:

1.研发过程中,由于散热和系统设计的需要,整个模块设计了外壳体,为了满足系统应用要求,同一片FPGA的JTAG接口需要从两个不同的地方引出,一个接口为专用的JTAG口连接器,由于结构限制,壳体不允许开槽引出,主要用于安装壳体前的调试阶段,另一个接口是从模块的底板连接器引出,便于安装壳体后在不拆卸壳体的情况下完成对JTAG芯片的调试。

2.由于设计需要,模块采用载板加背板的结构,整个模块设计了外壳体,按照设计要求,FPGA芯片置于背板,而结构要求JTAG连接器只能从载板处开槽引出,但为了方便背板单模块调试,需要在基板上增加壳体上不需开槽的JTAG口连接器。

以上两种应用模式是比较典型的FPGA芯片JTAG接口应用模式,实际应用中,都需要在两个不同的JTAG接口间切换,同时面临着由于走线长、接口多而稳定性差的风险。针对该应用需求,设计了一种JTAG接口切换电路,既实现了JTAG接口间的切换,同时克服了走线长、接口多可能引起的接口稳定性差的风险。

针对上述应用模式设计的JTAG口切换电路,创新性的将电路的切换与信号的驱动融合,既解决了多JTAG口切换的问题,同时克服了由于驱动能力可能引起的稳定性问题,以较低的成本解决了设计中的重要技术问题,缩短了研制周期和资源成本,降低了设计风险。

二、设计方案

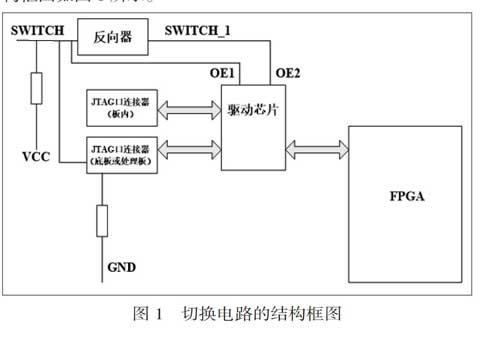

本文设计的电路利用驱动芯片分组控制的特点,将FPGA的JTAG口信号从驱动芯片的不同两组分别引至需要的连接器。根据应用需要,将驱动芯片的方向控制信号DIR置成固定态,将切换控制信号SWITCH利用反向器反向为SWITCH_1信号,切换控制信号控制一组驱动电路的使能信号OE1,其反向信号控制另一组驱动电路的使能信号OE2,实现JTAG口在两个不同引出接口间的切换,切换电路的结构框图如图1所示。

电路设计过程中,切换控制信号SWITCH在板内通过端接电阻置为高,当设计SWITCH信号为高时,JTAG口从板内JTAG口连接器引出,即OE1为高,OE2为低。

当需要从底板连接器或是处理板连接器引出时,将SWITCH信号在连接器引出端接地,此时SWITCH信号变为低,SWITCH_1信号变为高,即OE1为低,OE2为高,实现JTAG口间的切换。

该设计从硬件电路上便可以对该切换电路进行测试,检查JTAG口是否工作正常。

三、设计实现

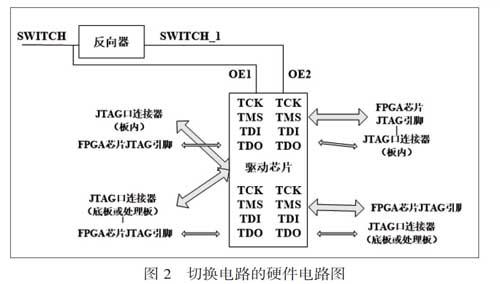

FPGA芯片的JTAG口利用串行数据进行命令和数据的处理,数据首先进入的是测试访问口,主要包括四个引脚:TMS、TCK、TDO、TDI,用于驱动电路和执行规定的操作,各引脚的功能如下:

TDI:测试数据输入,JTAG指令和数据的串行输入端口,在TCK上升沿时被采样。

TDO:测试数据输出,JTAG数据的串行输出端口,在TCK下降沿时输出。

TMS:测试模式选择,用于TAP控制器的内部状态机的状态切换,在TCK上升沿时被采样。

TCK:测试时钟,为寄存器和TAP控制器提供输入时钟。在TCK的同步作用下通过TDI和TDO引脚串行输入、输出数据[4]。

实现JTAG接口的切换,一个关键就是通过控制驱动芯片的使能和方向引脚,最终完成不同JTAG引出接口间的切换功能。

设计实现中,将驱动芯片的驱动方向固定,TDI、TMS、TCK信号输入为JTAG口对外连接器,输出至FPGA芯片的JTAG引脚,TDO信号的输入则为FPGA芯片的JTAG引脚,输出为JTAG口的对外连接器,同时利用反向器形成一组信号,从而控制驱动芯片的使能端,形成切换。切换电路的硬件电路示意图如图2所示。

相对于驱动芯片,两组输入分别为板内JTAG口连接器和底板连接器(或处理板连接器),输出均为FPGA芯片的JTAG口引脚。当需要从板内连接器引出JTAG信号时,SWITCH信号置为高,即驱动电路使能信号OE1为高,OE2为低,FPGA芯片的JTAG口从板内JTAG口连接器引出;当需要从底板连接器或是处理板连接器引出时,将SWITCH信号置为低,SWITCH_1信号置为高,即动电路使能信号OE1為低,OE2为高,完成JTAG口间的切换。

在实际调试过程中,通过Xilinx公司提供的Impact工具对电路的接口进行JTAG边界扫描(Boundary Scan选项),扫描可以在芯片的输入输出管脚增加移位寄存器,这些寄存器将芯片和外围输入输出隔离开,扫描单元连接形成了边界扫描链,通过显示出来的链路,我们可以看到FPGA芯片是否正常或对其调试。

根据上电时的管脚配置,选择片内对应的调试模式配置,当调试模式依次发生时,分别从不同的连接器接口引入,使用Impact工具对FPGA芯片进行扫描,发现FPAG在线,同时对其进行在线逻辑加载,读取引脚信号信息等功能,结果验证该设计方便且可靠。

四、结束语

在工程实践中,可以根据实际的应用情况,以不同的具体使用模式利用该电路进行JTAG接口切换,本文列举出的两种常见模式,满足了工程实践中不同的应用需求。

本文设计的切换电路实现了JTAG口切换,使用典型的驱动芯片和反向芯片,电路简单成熟,设计成本低。创新性的将电路的切换与信号的驱动融合,即解决了切换问题,也克服了由于驱动能力可能引起的稳定性问题,在实现切换的同时提高了可靠性,具有良好的实际应用价值。但同时,我们也要知道使用JTAG调试FPGA芯片也有其局限性,JTAG采用双向串行传输导致了其传输速度较低,因此对JTAG结构的加速方法和新的硬件也将在未来不断涌现[5]。

参 考 文 献

[1]杨佳奇. 基于JTAG的FPGA配置方法与电路设计[D].西安电子科技大学,2018.

[2]姚霁.一种基于JTAG的片内调试系统设计[J].现代电子技术,2020, 43(20):31-33.

[3]吕彩霞. JTAG的设计与研究[D].北京交通大学,2006.

[4]温国忠.JTAG接口电路设计与应用[J].微计算机信息,2007(23):298-299+302.

[5]胡学良,张春,王志华. JTAG技术的发展和应用综述[J]. 微电子学, 2005(06):624-630.