一种基于FPGA的方位增量码产生方法

范越 周晖

关键词:方位角码;增量码;FPGA;RS422

0引言

雷达工作时,显控系统需要从伺服系统接收天线的方位角码。天线使用双通道旋转变压器作为轴角传感器,经粗精通道解码组合后生成16位的天线方位角,提取出高12位作为给显控系统的方位角码。如果用并行接口来传输,且采用差分方式抑制共模干扰,则需要24根线,线缆数量较多,不利于安装调试且可靠性差。如果采用其他接口协议,在某些硬件条件不允许的情况下无法实现,而且舰船航向角变化有时会引起方位角跳变,不能直接使用。因此,需要在只有普通差分接口的条件下,将并行方位角码转换成串行的脉冲信号。

本文提出一种在FPGA中将并行12位(或更高)的方位角码信号经过补脉冲转换成串行的4096(或更多)个脉冲的增量码信号,然后使用RS422接口发送,简化线路,传输方便可靠。

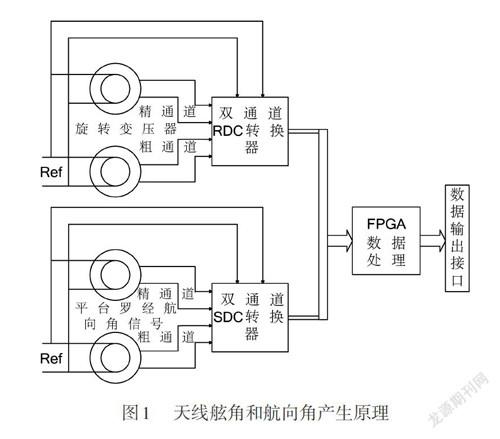

1天线舷角和航向角产生原理

伺服系统使用通用型高速、高精度轴角转换技术,针对高精度双通道旋转变压器和平台罗经航向角信号,运用小型化双通道轴角转换模块,利用大规模可编程逻辑器件的高速处理能力,运用硬件描述语言,通过软件现场調节的方法适应传感器的任意速比的组合纠错处理。其转换速率快、实时性好、精度高,能够适应各种雷达或电子对抗设备需要;电路的集成度高,便于嵌入式岗十;可靠性高,适应各种严苛的环境要求。天线舷角和航向角产生原理如图1所示。

旋转变压器的粗精通道比为1:32,RDC转换器输出数据的分辨率为14位。由于粗精通道比为1:32,粗通道的第8、第7位数据R8R7正好对应精通道的最高两位数据F13F12,当R8R7为“11”时,F13F12为“00”时,将粗通道的高5位数据加1;当R8R7为“00”时,F13F12为“11”时,将粗通道的高5位数据减1;然后将粗通道的高5位数据和精通道的高11位组合得到16位天线舷角码。

航向角信号的粗精通道比为1:36,SDC转换器输出数据的分辨率为14位。由于粗精通道比36不是2的n次方,所以只能通过将粗通道数据左移5位(乘以32)加上粗通道数据先左移2位(乘以4)得到与精通道量纲一致的数据。设这个数据为da-ta_temp[18-0]。判断data temp的第13、第12位数据data_tempi312和精通道的最高两位数据F13F12,当data_tempi312为“11”时,F13F12为“00”时,将data_temp的高5位数据加1;当data_templ312为“00”时,F13F12为“11”时,将data_temp的高5位数据减1;然后将dat_temp的高5位数据和精通道的高11位组合得到16位天线舷角码。

通过FPGA控制双通道RDC转换器,将旋转变压器的粗精通道信号转换后读取,经过粗精通道组合纠错处理后得到16位的天线舷角码。同时FPGA控制双通道SDC转换器,将平台罗经的航向角粗精通道信号转换后读取,经过粗精通道组合纠错处理后得到16位的航向角码。

2方位角码跳变原理

天线的方位角等于天线的舷角加上船的航向角,当船在调舷时,如果航向角的变化方向与天线旋转方向一致时,方位角就可能出现跳变的现象,因此无法通过方位角直接产生增量脉冲,需要在跳变的时候补脉冲确保天线转一圈4096个脉冲不丢失。跳变现象如图2所示。

天线的方位角合成是在时钟CLK的上升沿进行的,当第1个CLK的上升沿到来时,天线舷角为0,航向角为2,方位角即2(0+2);当第2个CLK的上升沿到来时,天线舷角为0,航向角变为3,方位角即3(0+3),未发生跳变;当第3个CLK的上升沿到来时,天线舷角变为1,航向角为3,方位角即4(1+3),未发生跳变;当第4个CLK的上升沿到来时,方位角保持4不变;当第5个CLK的上升沿到来时,天线舷角和航向角同时发生变化,天线舷角从1变成2,航向角从3变成4,方位角直接从4跳到6。此时如果将方位角码直接给显控系统使用则会产生问题。因此需要判断是否跳变并补码产生增量码。

3增量码生成原理

增量码脉冲生成的原理如图3所示。

原始的方位角码有16位,根据显控系统的需求,取原始方位角码的高12位使用来产生增量码。本系统中使用的是10 MHz的时钟,12位的方位角码FW经过1个时钟周期的延时得到FWT,将这2个方位角码作差比较得出天线方位角度的变化量,如果差值为0,不产生脉冲;如果为1,产生1个脉冲;如果为2,则说明方位角发生了跳变,产生2个脉冲;如果为3,则产生3个脉冲。考虑到船的调舷速度,不用考虑跳变3个脉冲以上的情况。

4 FPGA实现

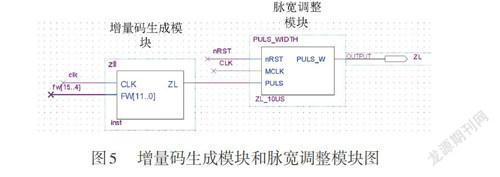

伺服系统以大规模可编程逻辑芯片FPGA作为系统的信号处理、I/O和总线管理核心。使用ALTERA公司的Cyclone系列芯片EPlC6Q24017,本芯片包含5980个逻辑单元,片内存储器92 160 bit,2个锁相环。使用VHDL语言进行编程。增量码生成模块内部如图4所示。

延时模块是将方位角码延时1个时钟周期输出,其中CLK为10 MHz时钟,fw为12位的原始方位角码,输出fwt。

比较模块是将当前方位角码fw和前1个时钟周期的方位角码fwt作差比较,如果发生变化,变化标志位fwbi置1,将变化差值fw-fwt赋给n输出。否则变化标志位fwbi置0,n输出保持不变。

在FPGA中经过延时模块、比较、脉冲生成、增量码合成后产生增量码,集成为如图5所示的“增量码生成”模块,将得到的增量码经过脉宽调整模块调整为所需要的脉冲宽度(10μs),最后发送出去。

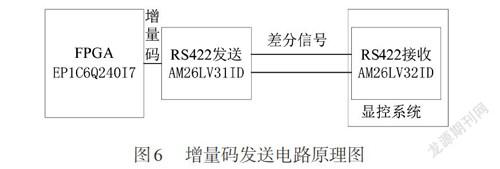

5硬件电路原理

使用RS422接口发送增量码信号的电路原理图如图6所示。

FPGA产生增量码后,经过10口输出,通过RS422发送芯片AM26LV31转换为差分信号发送给显控系统,经过差分接收芯片AM26LV32接收使用。

6结束语

本文介绍了使用高速、高精度轴角转换技术针对高精度双通道旋转变压器和平台罗经航向角信号的组合纠错处理方法,得到16位方位角码后,分析了其产生跳变的原理,并最终提出了一种在FPGA中将并行12位的方位角码信号经过补脉冲转换成串行的4096个脉冲的增量码信号的方法,大大精简了传输线缆数量,提高可靠性。该方法已在实际系统中应用,完全符合系统工作要求,运行良好,证明了方法的有效性。