面向DSP+FPGA通用处理架构检测的硬件系统设计

谢林峰,何敏,李文鑫

(四川九洲电器集团有限责任公司,四川绵阳,621000)

0 引言

基于FPGA+DSP架构的通用信息处理板作为信息处理的核心和标准模块,用它进行信息处理等应用层面的开发能够在缩短开发周期、降低成本、提高产品可靠性方面起到重要作用,因而在信息处理中得到了广泛的应用[1]。由于基于FPGA+DSP架构的通用信息处理板的核心器件均采用了BGA封装的芯片,依照现在的工艺水平,在焊接过程中管脚极易出现粘连的情况[2],加之通用信息处理板上用于存储数据的FLASH和用于运行程序的SDRAM也极易出现粘连坏块的情况,导致存储数据丢失或程序无法正常运行。

目前针对基于FPGA+DSP架构的通用信息处理板出现使用异常的情况,主要通过X射线对器件的所有管脚进行观察后重新进行焊接[3]。但是目前X射线仅限于检测连焊和空洞等有限的集中缺陷的检测,不能覆盖全部BGA焊接缺陷;同时缺乏检测标准[4]。针对上述情况,通过搭建完整的硬件检测系统,能够实现有针对性的对关键器件焊接异常情况进行快速的排查,在提升DSP+FPGA通用处理平台的可靠性和后续应用开发效率的同时,对焊接工艺也具有一定的指导意义。

1 检测系统设计

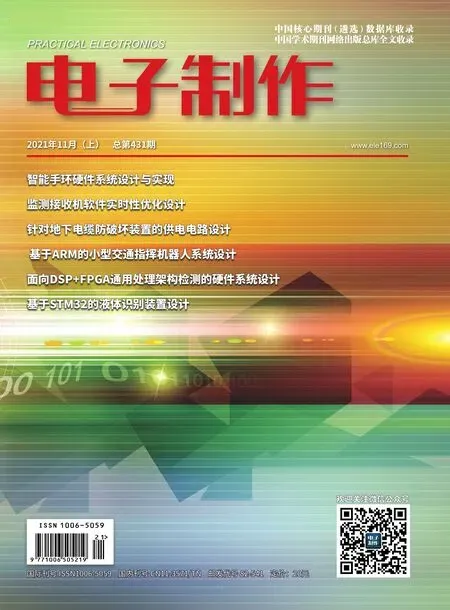

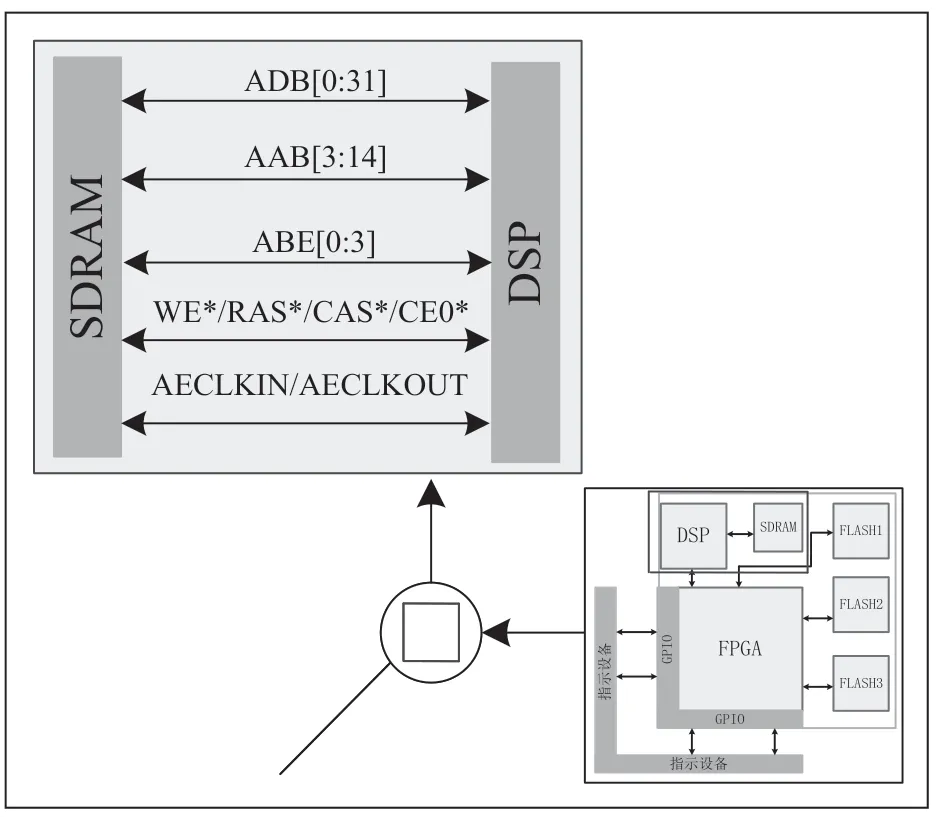

基于FPGA+DSP架构的通用信息处理板的原理图如图1所示,图1显示出通用信息处理板的对外通用输入输出接口(GPIO)由FPGA的管脚引出,与外围接口/设备实现通信。同时,图1也显示了通用信息处理板内部核心器件(IC)间的互连关系,FPGA通过Bank IO与DSP的EMIFB口互连;配置FPGA、存储DSP程序和存储数据等信息的FLASH通过并行总线与FPGA的管脚互连;运行DSP程序的SDRAM通过并行线与DSP的EMIFA口互连[5]。

图1 通用信息处理板的原理图

根据通用信息处理板的原理,采用外围指示设备(LED灯)指示的方法来实现对通用信息处理板的检测,检测的项目和流程如下。

■1.1 通用信息处理板GPIO口的检测

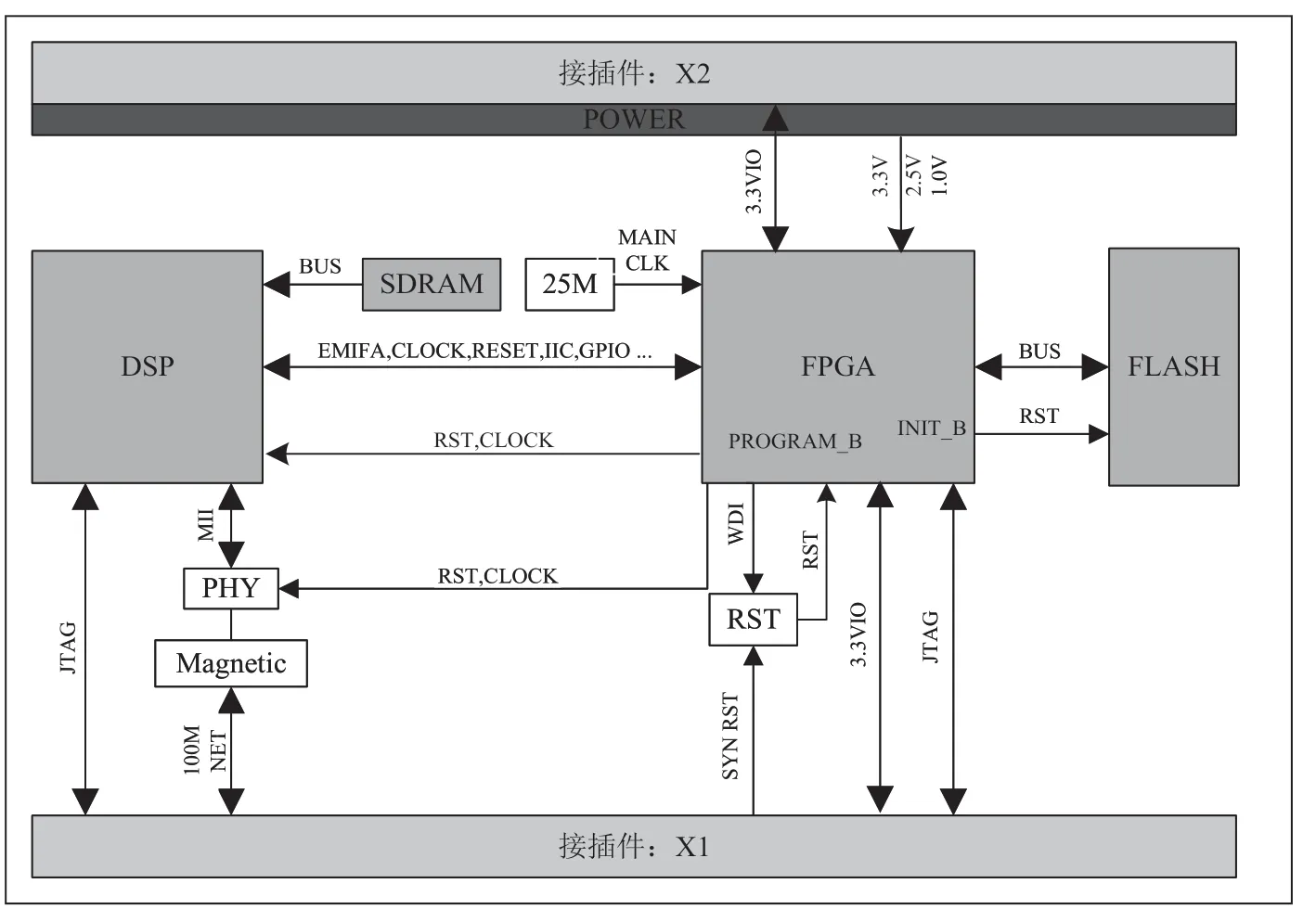

通用信息处理板的GPIO口与外围LED灯逐一相连的示意图如图2所示。

图2 通用信息处理板的GPIO口与外围LED相连的示意图

检测过程中,FPGA产生的信号依次送出高电平到GPIO口,外围LED灯逐一被点亮。若出现多个LED灯同时被点亮则说明引出GPIO口的FPGA管脚存在粘连;若出现LED该亮而不亮的情况,说明引出GPIO口的FPGA管脚损坏(粘连接地)或者该链路通信不畅通。根据分析所得的FPGA引脚的粘连情况,详细检测方案如下。

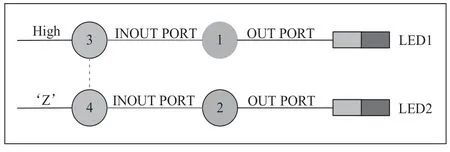

1.1.1 FPGA外部管脚间的粘连及检测

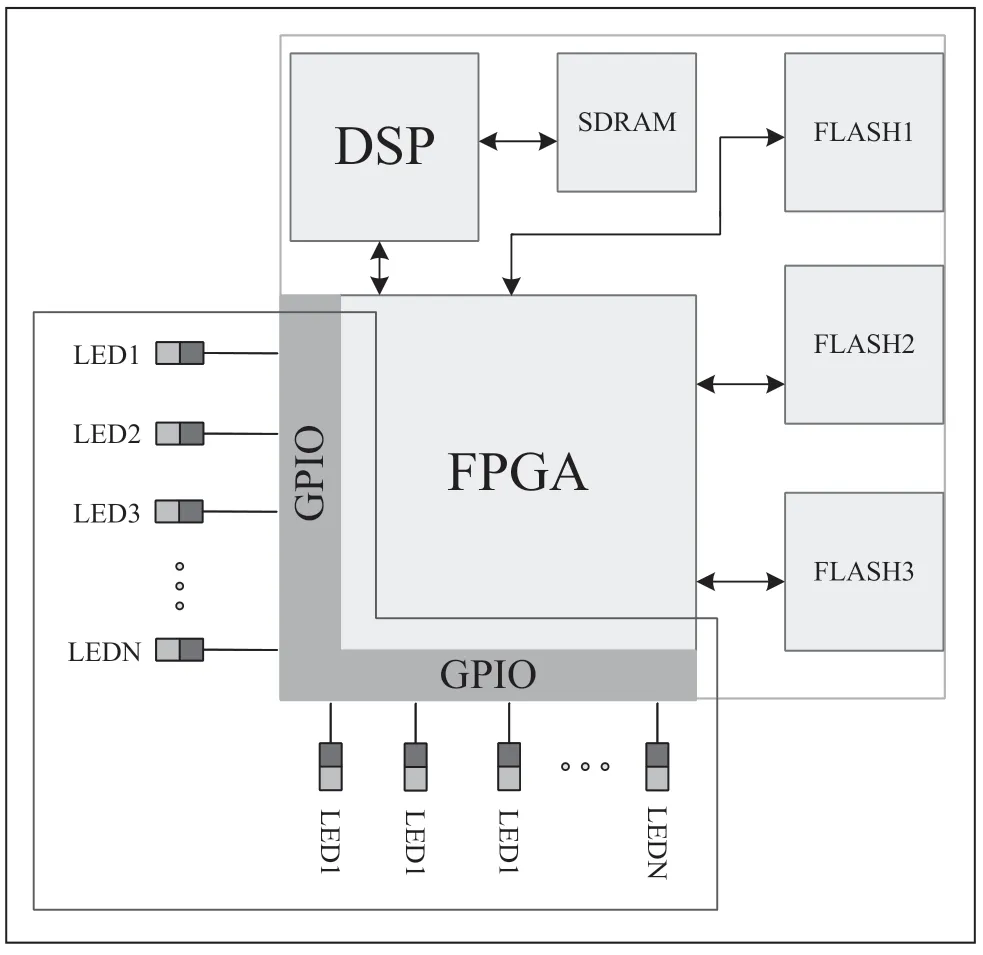

FPGA外部管脚(引至外部插座处管脚,管脚的端口属性为:OUT)之间的粘连情况如图3所示,端口1输入高电平,端口2输入为高阻态“Z”,正常情况下LED1亮,而LED2不亮,若端口1与端口2出现粘连,则LED1和LED2都亮;若端口1或端口2与Vcc粘连,则对应的LED灯常亮;若端口1或端口2与GND粘连,则对应的LED灯常灭(若出现链路不通的情况,也会出现对应的LED常灭的现象)。

图3 FPGA外部管脚之间的粘连情况示意图

根据以上分析,依次给FPGA外部管脚送出高电平,FPGA引至插座处的其他所有管脚都为高阻态“Z”,正常情况下只有一个LED灯亮,其他LED灯都不亮。若FPGA外部管脚之间存在粘连则与之相连的LED都会亮;若FPGA外部管脚存在与Vcc粘连,则对应的LED灯会常量;若FPGA外部管脚存在与地粘连,则对应的LED灯会常灭。

1.1.2 FPGA内部管脚间的粘连及检测

FPGA内部管脚(没有引至外部插座处的管脚,管脚的端口属性为:INOUT)之间的粘连情况如图4所示,端口3通过端口1与LED1灯相连,端口4通过端口2与LED2灯相连。端口3输入高电平,端口4输入为高阻态“Z”,正常情况下LED1亮,而LED2不亮;若端口3与端口4出现粘连,则LED1和LED2都亮;端口3与Vcc或GND粘连,LED1灯的亮灭不受影响;若端口4与Vcc粘连,则对应的LED2灯常亮;若端口4与GND粘连,则对应的LED2灯常灭。

图4 FPGA内部管脚之间的粘连情况示意图

根据以上分析,依次给FPGA内部管脚送出高电平,FPGA内部的其他所有管脚都为高阻态“Z”,正常情况下只有一个LED灯亮,其他LED灯都不亮。若FPGA内部管脚之间存在粘连则与之相连的LED都会亮;若FPGA内部管脚存在与Vcc粘连,则对应的LED灯会常量;若FPGA引至插座处的管脚存在与地粘连,则对应的LED灯会常灭。

1.1.3 FPGA外内部管脚间的粘连及检测

FPGA外部管脚与内部管脚的粘连情况如图5所示, 端口4通过端口2与LED2灯相连。端口1输入高电平,端口4输入为高阻态“Z”,正常情况下LED1亮,而LED2不亮;若端口1与端口4出现粘连,则LED1和LED2都亮;若端口4与Vcc粘连,则对应的LED2灯常亮;若端口4与GND粘连,则对应的LED2灯常灭。根据以上分析,依次给FPGA内部管脚送出高电平,FPGA内部的其他所有管脚都为高阻态“Z”,正常情况下只有一个LED灯亮,其他LED灯都不亮。若FPGA内部管脚之间存在粘连则与之相连的LED都会亮;若FPGA内部管脚存在与Vcc粘连,则对应的LED灯会常量;若FPGA引至插座处的管脚存在与地粘连,则对应的LED灯会常灭。

图5 FPGA外部管脚与内部管脚的粘连情况示意图

■1.2 DSP与FPGA互连链路的检测

通用信息处理板的FPGA与DSP EMIFB口相连的示意图如图6所示[6]。DSP产生一组信号,将DSP EMIFB口的 21位的地址线全部置零,将16根数据线由高位到低位依次送出高电平至与FPGA相连的管脚,经FPGA内部转换后通过链路1从通用信息处理板的GPIO口输出来控制外部LED灯的点亮情况,若出现多个LED灯同时被点亮则说明与DSP相连的FPGA管脚存在粘连;若出现LED该亮而不亮的情况,说明与DSP相连的FPGA管脚损坏或者链路2通信不畅通。同理,将DSP EMIFB口的 16位的数据线全部置零,将21根地址线由高位到低位依次送出高电平至与FPGA相连的管脚,经FPGA内部转换后通过链路1从通用信息处理板的GPIO口输出,依照上述方法观察LED的点亮情况来判断故障。

图6 通用信息处理板的FPGA与DSP相连的示意图

■1.3 FLASH与FPGA互连链路的检测

通用信息处理板的FLASH与FPGA相连的示意图如图7所示。在DSP的协同配合下,通过FPGA构建DSP与FLASH的数据链路,运行DSP程序对FLASH进行擦出、读写等操作,并将检测结果自行显示。

图7 通用信息处理板的FPGA与FASH相连的示意图

■1.4 DSP与SDRAM互连链路的检测

通用信息处理板的SDRAM与DSP EMIFA口相连的示意图如图8所示。DSP作为主动设备程序对SDRAM的存储空间逐一进行擦出、读写等操作[7],并将检测结果通过FPGA构建DSP与外围(指示)设备(LED灯)的数据链路自行显示。

图8 通用信息处理板的SDRAM与DSP相连的示意图

2 检测结果及分析

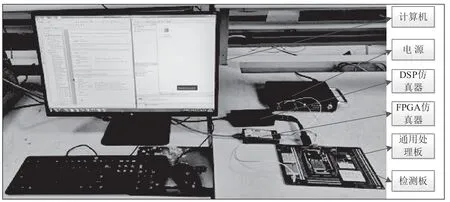

根据对DSP+FPGA通用处理平台硬件检测系统的设计思路开展了软硬件的设计工作,基于设计的硬件检测系统搭建的测试平台如图9所示。

图9 检测通用信息处理板的硬件测试平台

开发的检测硬件搭建对DSP+FPGA通用处理板的检测系统,通过加载不同的检测程序实现了对DSP+FPGA通用处理板所有关键器件(如FPGA、DSP、FLASH、SDRAM等BGA器件)的检测,图10显示了对通用信息处理板FPGA外部管脚间粘连的实验结果,通过实验表明该检测方法准确有效。

3 结论

本文针对基于FPGA+DSP架构的通用信息处理板的核心器件均采用了BGA封装的芯片,依照现在的工艺水平,在焊接过程中管脚极易出现粘连的情况,介绍了一种对DSP+FPGA通用处理架构进行硬件检测的方法,通过设计和构建硬件检测系统,实现对DSP+FPGA通用处理平台硬件状态进行快速检测,提升了DSP+FPGA通用处理平台的可靠性和后续应用开发的效率,同时对焊接工艺也具有一定的指导意义。