新型PD 协议芯片BMC 解码电路的设计与验证*

张万荣,王飞虎

(北京工业大学 信息学部,北京 100000)

0 引言

近年来,随着移动设备快速充电功率的不断提高,USB 标准化组织(Universal Serial Bus Implementers Forum,USB-IF)制定了基于BMC 编码的USB 功率传输(Universal Serial Bus Power Deliver,USB PD)3.0 协议,该协议相比于Qualcomm 公司的快速充电(Quick Charge,QC)协议、Samsung 公司的自适应快速充电(Adaptive Fast Charge,AFC)协议等快充协议具有只占用一根通信线,协议内容可拓展性强等优点,已成为应用最广的快充协议[1-3]。BMC 解码模块是USB PD 3.0 协议芯片的核心模块[4-6]。随着手机快充功率突破120 W,峰值电流可达到6.25 A,电流大范围变化带来的地电位漂移现象愈发严重,地电位漂移导致BMC 信号在传输过程中周期多次连续变化使得BMC 信号周期累计变化范围可达3.3 μs 的±30%[7];随着USB 线中数据传输速率提高到20 Gb/s 使,USB 线包内的电磁环境更加恶劣,从而使得BMC 信号在传输过程中受到大量高频噪声干扰而导致周期单次大幅度突变[8]。为解决上述问题,近年来人们提出了一些对BMC 解码模块优化的方案,文献[9]提出了一种解码电路能够成功解码周期在3.3 μs±25%范围内变化的BMC信号,但是当BMC 信号周期累计变化到±30%时不能成功解码,而是通过错误反馈机制强制USB PD 3.0 协议芯片回到初始状态。

针对上述文献的不足,本文在传统解码模块的基础上,首先,通过调整传统解码系统的结构并加入状态机实现了对信号周期单次变化在±25%以内的BMC 信号成功解码;另外,通过新增的FIR 滤波器产生随BMC 信号周期浮动的解码阈值实现了对周期多次连续变化的BMC 信号成功解码。

1 新型BMC 解码电路的设计

BMC 解码规则如图1 所示,被解码信号在每一比特开始前先进行一次翻转,如果某一比特的1/2 位置发生了一次翻转,则该比特被解码成二进制数1,如图1 中第1 比特和第3 比特所示;如果被解码信号某一比特内不发生翻转,则该比特被解码成0,如图1 中第2 比特和第4 比特所示[10-11]。

图1 BMC 解码规则

传统的BMC 解码系统电路结构如图2 所示,包括滤波模块、边沿检测模块、解码模块[12]。首先,数字BMC信号是由模拟信号经过施密特触发器得到的,容易带有毛刺,滤波模块可以滤除宽度为200 ns 以下的毛刺;然后,边沿检测模块输出的BMC 信号的上升沿和下降沿作为解码模块中计数器开始和结束的条件;最后,解码模块通过对BMC 信号64 比特前导码的过采样求周期的平均值得到解码阈值,通过对比解码阈值和计数器计数值的大小解码数据包的有效数据部分,当计数器的值小于3/4 解码阈值时解码结果为1,否则为0。从而实现了BMC 信号的解码。

图2 传统BMC 解码系统电路结构

为了实现对信号周期单次变化在±25%以内的BMC信号成功解码,本文将计数器从解码模块中分离出来并在解码模块内新增状态机。新型BMC 解码电路架构如图3 所示,其中优化后的解码模块电路原理图如图4所示,Threshold 值进入解码模块后先进行移位操作得到1/2Threshold 和1/4Threshold,然后将1/2Threshold 和1/4Threshold、Threshold 和1/4Threshold、1/2Threshold 和Threshold 分别进行加法运算得到3/4Threshold、5/4Threshold、3/2Threshold 的值,通过比较器后得到它们与Cnt 值的大小关系,将比较结果与Edge 信号做与运算后作为状态寄存器的跳转条件,D register1 和D register2 构成状态机的2 比特位宽的状态寄存器,D register3 为输出寄存器,当状态寄存器值为01 且与门And1 产生的结果为1时输出1,当状态寄存器值10 与门And1 产生的结果为1 时输出0。优化后的解码模块与其他模块间的协作方式如图5 所示。首先,BMC_Signal 信号经过消抖模块打拍后得到BMC_Signal_Filtered 信号,当解码模块检测到BMC_Signal_Filtered 信号后认为数据开始传输,状态机从Idle 状态跳到Counter_First 状态,同时边沿检测模块会检测到BMC_Signal_Filtered 信号的出现,从而激发计数器开始工作。然后,当BMC_Signal 信号发生跳变时会再次被边沿检测模块捕捉到并使得边沿检测模块产生脉冲信号Edge,当解码模块在Counter_First 状态检测到Edge信号时会比较计数器产生的Cnt 和阈值Threshold 的大小,如果Cnt 的值处于3/4Threshold 和5/4Threshold 之间,则将当前比特的BMC 信号解码为0;如果Cnt 的值处于1/4Threshold 和3/4Threshold 之间,则将当前比特的BMC 信号解码为1。因此,新型BMC 解码电路可对信号周期发生1/4 形变的信号解码。

图3 新型BMC 解码系统电路结构

图4 解码模块电路原理图

图5 新型BMC 解码系统协作方式

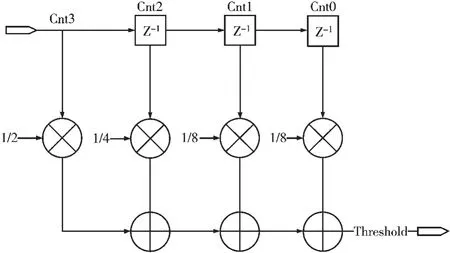

为了实现对周期多次连续变化的BMC 信号成功解码,本文在新型解码电路中增加FIR 滤波模块。新型BMC 解码电路架构如图3 所示,其中FIR 滤波器电路原理图如图6 所示,其为四阶FIR 滤波器,本文设计的FIR滤波器的高通区间为250~350 kHz,通过MATLAB 调用FIR 滤波函数计算得到抽头系数分别为61、30、16、15。为了减小芯片面积且便于电路实现,本文将抽头系数h近似为1/2、1/4、1/8、1/8[13-15],由式(1)可知输出结果Threshold 值不再是固定值,而随相邻Cnt 值同向变化。由图3 和图5 可知,FIR 滤波器的输入Cnt 值由计数器和解码模块共同决定,当解码模块在Counter_First 状态或者在Counter_Second 状态检测到Edge 信号时比较对计数器产生的Cnt 和阈值Threshold 的大小,如果Cnt 的值处于3/4Threshold 和5/4Threshold 之间,则将计数器的值打入FIR 滤波器。FIR 滤波器每接收到一次计数器的传递来的结果就会通过FIR 算法更新一次传送给解码模块的Threshold 值,从而完成更新Threshold 的值的正反馈,达到了连续多比特位宽均变化时仍可以成功解码的目标。

图6 FIR 滤波器电路原理图

2 新型BMC 解码电路的仿真与验证

传统解码算法能够允许的BMC 信号周期变化范围为25%,由于供电功率增大或减小导致BMC 信号周期变化超过25%时会导致解码失败[16]。图7 为传统解码模块对周期连续变化的BMC 信号进行解码的仿真结果。BMC_Signal 为待解码的BMC 输入信号;Number 表示当前输入的BMC_Signal 信号的序号;BMC_Signal_Filtered为BMC_Signal 经过滤波后得到的信号;Edge 信号为边沿检测模块的检测结果;Counter 为计数器的值,计数器以19.2 MHz 的频率对 BMC_Signal 信号进行过采样;Counter_Result 为计数器对前一位BMC_Signal 信号的采样结果,例如,Number 为2 时Counter_Result 为64 表示计数器以19.2 MHz 的频率需计数64 次完成对Number为1 时BMC_Signal 的采样;BMC_Decode_Result 为解码结果。由图7 可知,本文仿真了输入信号BMC_Signal 的前10位的周期以6.25%的速度增加,第10 位到13 位周期保持不变,第13 位到第21 位周期以6.25%的速度升高。周期变化幅度小于25%时,BMC_Signal 的前5 位能够成功解码,第6 位到第17 位变化幅度超过25% BMC_Decode_Result 一直为0,解码失败,第18 位后BMC_Signal 信号周期重新升到3.33 μs±25%的范围内后,传统解码模块再次正确解码。由仿真可知,传统BMC 解码模块只可以对周期在3.33 μs±25%范围内的信号进行解码。

图7 传统解码模块仿真结果

由图8 可知,本文仿真了输入信号BMC_Signal 第4位中的254 ns 宽的毛刺成功被消抖模块滤除,滤波后的信号BMC_Signal_Filtered 没有毛刺;输入信号BMC_Signal 前10 位的周期以6.25%的速度增加,第14 位到第18 位的周期以6.25%的速度减小,由于加入了FIR 滤波器使得Threshold 值随Counter_Result 增大或减小,从而新型BMC解码电路均能成功解码。

图8 新型解码模块仿真结果

本文与文献[9]的性能比较见表1 所列,本文设计的新型BMC 解码电路可对任意频率的BMC 信号进行解码,文献[9]仅可以对周期在300 kHz±25%范围内的信号进行解码,且在华虹半导体0.18 μm 工艺下面积相比于文献[9]减少了57.29%,功耗相比于文献[9]减少了89.10%。

表1 性能比较

3 结论

为了实现对单比特周期突变25%的BMC 信号解码,而且能够对周期多次连续变化的BMC 信号成功解码,本文将计数器从解码模块中分离出来并在解码模块内新增状态机,另外在传统解码电路中增加了FIR 滤波模块。状态机的跳转条件为Cnt 值相对于Threshold 值可变化1/4,实现了对单比特周期突变25%的BMC 信号的解码;新增的FIR 滤波器使得Threshold 值随Cnt 值线性变化,实现了对周期多次连续变化的BMC 信号成功解码。对新型BMC 解码电路的仿真结果表明,可以对周期相差25%的相邻两位BMC 信号解码,可以对周期以6.25%增加的连续十位进行解码。