基于Labview 嵌入式的太赫兹安检仪高速数据传输系统

■ 文/公安部第一研究所 崔晓熙

关键字:太赫兹安检仪 高速数据 Labview

1 引言

主动太赫兹人体安检系统是指通过测量人体和物体,利用其在时域、频域、空域、极化域和功率域物体的散射信息差异,检测隐匿在人体衣物下的各种危险品。重要交通场合尤其是机场快速安检,对太赫兹安检仪系统的实时性提出了新要求,目的是提高检测系统实时性。因此,本文对各个数据流节点的实时性研究是设计重点。一方面,检测系统通过降频滤波方法降低高速A/D 转换后的数据速率,减少回波数据有效数据量;另一方面,可采用万兆网提高FPGA 向PC 传输的回波数据传输速率,实现回波数据的实时采集和传输。

在设计开发过程中,系统从FPGA、RT 和PC 三层构架均使用Labview 图形化开发平台,大大降低了系统程序设计的复杂度,同时节省了人力成本,缩短了开发时间。

2 硬件组成

在数据采集与图像处理过程中,系统硬件组成为射频收发系统、信号采集系统、工控机等。

2.1 射频收发系统

射频收发系统由天线阵列和射频信道组成。天线阵列发射信号并接收回波信号,接收天线将接收到的高频带宽信号送入射频信道,信号经过混频、滤波、下变频处理,最后分IQ 两路输出中频信号。

2.2 信号采集系统

信号采集系统由FlexRIO 数字化仪适配器和FlexRIO控制器构成一个高速数字化仪。FlexRIO 控制器NI-7935及采集卡NI-5761是National Instrument公司提供的较为稳定的模块化硬件数字采集与信号处理平台,目的是为了快速验证中频信号采集及预处理算法程序设计的合理性。

数字化仪适配器NI-5761 在500MHz 的模拟带宽下最高以250MS/s 的速度可同时采集四个通道,可结合高性能A/D 转换器实现模拟数据的实时处理和传输。

FlexRIO 控制器NI 7935 具有可编程的FPGA 和嵌入式处理器,适用于现场部署,为需要高级I/O 功能及嵌入式信号处理的应用提供了可靠的长时间运行。包括Xilinx Kintex-7 K410T FPGA、2GB 板载DDR3 DRAM、运行NI Linux Real-Time 的双核ARM Cortex-A9 处理器和用于数据传输的2 个SFP+端口。系统中最关键的任务分配给FPGA,比如系统中采集、控制循环及安全状态逻辑等。应用的主体分配给Real-Time 处理器,包括系统监控任务、消息处理、序列发生器或数据记录引擎等。

本系统射频模块与5761 适配器通过IQ 两路SMA 接口相连见图1,5761 以125MS/s 的速度同时采集IQ 两路中频回波信号。SMA 连接器普遍适用于微波领域,具有频带宽、性能优、高可靠、寿命长等特点。

图1 系统构架框图

3 数据采集与传输

3.1 数据采集

射频收发系统输出I、Q 两路中频信号,公式如下:

图2 回波信号时域图谱

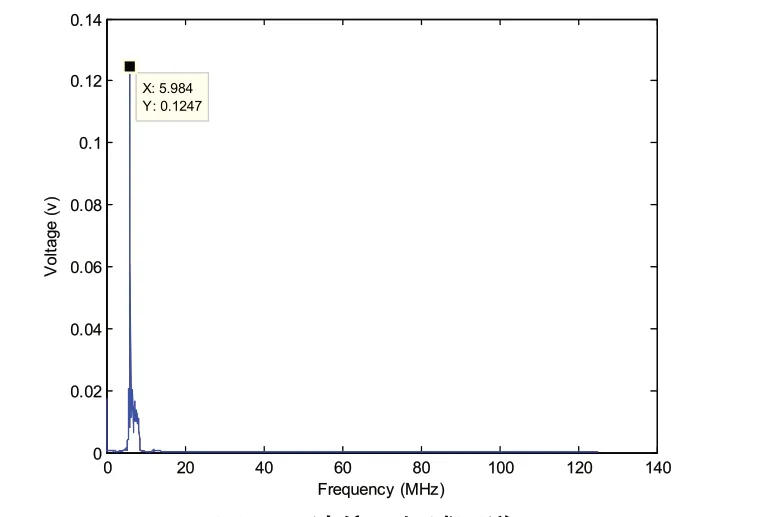

图3 回波信号频域图谱

本系统高速A/D 直接中频采样,由于A/D 采样率fs通常比较高,而实际上基带信号本身带宽相对较窄,高采样率信号会增加后续基带信号处理的难度,所以有必要将高速A/D 转换后的数据速率降低到后级电路可以处理的速度。为满足太赫兹安检仪检测时间的实时性要求,一方面,本系统通过下变频滤波方法降低高速A/D 转换后的数据速率,减少回波数据有效数据量;另一方面采用万兆网提高FPGA 向PC 传输的回波数据传输速率,实现回波数据的实时采集和传输。

3.2 降频滤波算法设计

数字信号预处理算法主要通过数字下变频、滤波抽取的方法输出低速率的43 基带数据。本系统设计降频滤波器(见图4)实现IQ 中频通道采样率输出fs/8,设计中频数字混频器实现数字混频,最终输出零中频或任意中频IQ 信号。正交混频是为了处理掉中频采样中的中频而设计的。

具体的技术要求如下式所示:

经A/D 采集后的数字回波信号进入降频滤波器,经低通滤波及8 倍抽取后,回波信号的频域见图4,数据量降低为原来的八分之一,信号频谱无失真。

图4 滤波抽取后的回波信号

3.3 数据传输

为满足不同系统不同数据量实时传输要求,NI-7935设计了两种数据传输通道。第一种为千兆网小数据量数据传输,数据经降采样后通过FPGA 的DMA FIFO 上传到RT 后通过网络流形式从RT 上传给计算机。第二种为万兆网大数据量数据传输,直接从数字采集系统的SFP接口上传至计算机。这两种上传通道的关系是冗余备份的关系,可以通过上位机的配置实现传输方式的切换,无论哪种上传方式,数据都能够实现实时上传。采集传输状态机的程序框图如图5 所示。

图5 回波数据传输

千兆网数据传输,数据实现了PC、RT、FPGA 三层结构的传输。在本系统中,采集的I、Q 两路数据形式经过预处理算法处理后,最后将IQ 两路合并成一路数据,开辟1 个FIFO 存储器向RT 传输数据。FPGA 端和RT端直接传输缓冲数据最好的方法是使用DMA 传输。DMA FIFO 从FPGA 直接传输数据至RT 终端的内存,且DMA FIFO 可在FPGA 和RT 之间以数据流方式传输大量数据,这使得FPGA 将RT 终端的内存当作其自身内存一样使用。在RT 和计算机两端应用程序之间连接流数据可通过网络数据流的方法,网络数据流不损耗数据,是单向的一对一通信信道,由写入方和读取方端点构成。网络流函数用于通过网络流传输数据。

万兆网数据传输,在计算机端配置PXIe-8238 万兆网卡,在FPGA 端配置10G 以太网IP 核,采集的中频数据流先进入DDR 做缓存处理,协议栈从DDR 中取出数据,进行可靠传输处理,并将数据送入万兆网物理层模块,完成数据包的发送。协议栈同时从物理层模块接收数据包,完成确认通信。万兆网传输采用UDP 协议,使用时需要设置源端与目标端的端口地址、IPv4 地址、MAC 地址以及数据UDP 数据长度。

图6 是万兆网在FPGA 中的数据传输程序,第一个循环是读取10G 以太网IP 核状态,第二个循环与最下面的函数节点是UDP 协议发送数据的程序,其工作过程为当一切就绪时,向UDP 程序发出信号,表示正在启动一个数据报,告诉UDP 程序数据报内部有效负载的大小,然后UDP 程序开始将此数据报的报头数据传输到MAC Writer 程序。当准备好时,使用反馈节点从示例进程请求有效负载数据。反馈节点是集群,包含“准备启动”和“准备有效负载”,由于发送数据报报头数据和发送有效负载数据之间的延迟,存在区别。

图6 万兆网在FPGA 数据传输程序

4 系统测试结果

表1 系统检测时间统计

5 结语

本文通过对Labview 嵌入式太赫兹安检仪高速数据传输系统软件设计分析,介绍基于FlexRIO 控制器和适配器、射频模块以及工控机组成的系统构架,根据数据量需求巧妙设计数据预处理算法及多种数据实时传输方式,并给出实时处理结果以及处理时间评估,实时性和精确性符合技术要求,为满足重要交通场合尤其是机场快速安检的需要奠定了重要基础。

图7 是本项目实时处理系统软件界面。左侧为采集到单通道时域和频域带宽信号,可以实时监测采集信号的正确性,右侧显示测试所得到的太赫兹人体图像,系统工作在毫米波段,扫描范围为2m*1m,图像空间分辨率为5mm*4mm,线分辨率为1mm。图像中所呈物体轮廓清晰,聚焦效果良好,符合 5mm 分辨率要求。

图7 系统软件界面

当处理完成之后,需要对整个处理软件的性能进行评估。评估的重点主要是实时性,即处理软件针对每幅图像的处理时间要求。此处选取 5mm 分辨率下的处理时间进行评估。距离向和方位向的处理点数分别为383 点和250 点。系统检测总时间统计,可知系统检测处理时间短,满足实时传输实时图像处理的技术要求。