一种进位链TDC 的实现及其抽头方式研究

李海涛 ,李斌康 ,2,田 耕 ,2,阮林波 ,2,吕宗瞡

(1.西北核技术研究所,陕西 西安 710024;2.强脉冲辐射环境模拟与效应国家重点实验室,陕西 西安 710024)

0 引言

时间是物理学的7 个基本物理量之一[1],在物理学发展中起到重要作用,精确地获取研究对象的时间信息具有重要意义。对时间信息的获取可以由时间数字转换器(Time to Digital Converter,TDC)来实现,TDC 将时间信息转换为二进制数字编码,输出到后端分析,得到具体时间信息。TDC 广泛应用在高能物理、卫星授时、导航定位、数字通信、医学成像等领域[2-5]。

TDC 有多种实现方法,包括直接计数法、时间间隔扩展法、时间幅度转换法、多相位时钟法、游标法、抽头延迟链法、差分延迟链法等,各种方法既可以独立使用,又可以配合使用,实现从低精度到高精度、从细时间到粗时间的时间测量。从技术上划分,TDC 的实现可以分为模拟方法和数字方法;从平台上划分,TDC 可以在专用集成电路平台 (Application Specific Integrated Circuit,ASIC)、FPGA 等平台上实现。ASIC-TDC 的测量精度、稳定性较高,一般都是针对某一特定场景应用设计,不具有通用性和可扩展能力,并且开发ASIC 芯片的周期很长;FPGA-TDC 具有开发周期短、成本低、设计灵活等优点,但是精度和稳定性较差。随着半导体制造工艺的进步,FPGA-TDC 的测量精度和稳定性等同步提高,实现高精度FPGA-TDC 具有重要研究意义。

目前,实现高精度FPGA-TDC 的研究主要集中在几个方面[2,6-9]:(1)FPGA-TDC 的实现,使用FPGA 内部资源实现高精度TDC,把时间信息转换成二进制数字编码;(2)TDC 码宽的自动校准,选择合适的校准方法,校准TDC码宽,降低FPGA 制造工艺、工作电压、工作温度(Process、Voltage、Temperature,PVT)等对TDC 的影响;(3)针对TDC码宽的不一致性,如何降低测量误差,进一步提高测试精度;(4)动态监测并实时校准TDC 码宽,针对特殊要求(如航天等)进行冗余设计等。对FPGA-TDC 的研究主要集中在前述的第1、第3 方面,在不同FPGA 平台上实现进位链TDC。受限于进位链的线性度,TDC 的线性较差,导致时间测量精度下降。通过多链单次测量求平均[1,8,10]或者单链多次测量求平均[11-12]的方法,可以提高TDC 的线性和时间测量精度。对TDC 的码宽的动态监测、冗余设计等,一般应用在航空航天等特殊领域[2]。对于单链TDC 的码宽校准和抽头方式方面(前述第2 方面),缺少较为深入的研究。

本文利用Xilinx 公司28 nm 工艺的Kintex-7 FPGA内部的进位链资源,通过进位链实现TDC,共使用128个进位链,细时间测量范围大于5 ns。并给出码宽校准的误差计算公式,采用码密度校准方法对TDC 进行逐位校准,测量得到4 抽头模式、2 抽头模式下的TDC 典型码宽,给出不同抽头模式的TDC 典型性能参数。

1 进位链TDC 实现

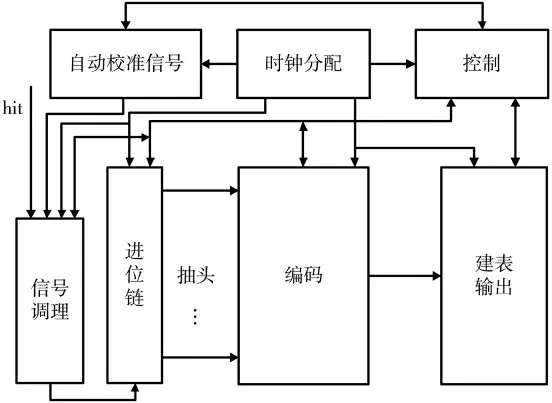

典型的进位链TDC 原理如图1 所示,包含了脉冲信号调理、时钟产生分发设计、进位链设计、温度计码转二进制编码编码电路设计、自动校准设计等。脉冲信号(待测信号或随机校准信号)经过脉冲信号调理单元称为待测信号,从下方进入到进位链中;待测信号一般小于一个TDC 主时钟周期,确保级联延迟链输出为温度计码;温度计码经过2 拍寄存以避免亚稳态传播,进入到编码部分,采用改进的折半查找法完成温度计码的编码,输出对应的二进制码;采用码密度校准方法建立查找表,将二进制码对应的查找表的结果输出到后端处理,便可获得高精度的时间信息。接下来结合FPGA 的具体逻辑资源,介绍进位链TDC 的实现。

图1 进位链TDC 典型原理

基于Kintex-7 芯片内部的进位链资源实现TDC,Kintex-7 系列FPGA 的基本逻辑单元为可配置逻辑块(Configurable Logic Block,CLB),每个CLB 中包含两个Slice 结构,每个Slice 内部进位链结构如图2 所示,设计时可直接调用Xilinx 提供的原语例化进位链。hit 信号从第一个进位链的CYINIT 端口输入[13],输入的hit 脉冲经过脉冲信号调理之后,待测信号沿着进位链向上传播,CIN 和COUT 用来连接上下相邻的进位链形成进位链,其附近的4 个寄存器可分别寄存O0~O3 或CO0~CO3抽头的4 个输出,进位链的综合版图如图3 所示,可以采用多种抽头方式引出数据并寄存,不同抽头方式对应的时间分辨率不同,包括1 抽头、2 抽头、4 抽头等,图中显示为2 抽头方式,抽头分别为CO0、CO3。

图2 slice 内部典型进位链示意

图3 进位链综合后版图(跨时钟域)

进位链TDC 中触发器阵列寄存的数据是温度计码,当没有脉冲信号时,进位链中所有的抽头输出均为0;当有脉冲信号进入进位链时,进位链输出信号将从最低级开始逐级发生0-1 跳变,待测信号经过的进位链抽头将输出数字编码1,没有经过的进位链抽头将输出数字编码0,可以根据进位链抽头输出的1 的个数来判断待测信号在进位链中的延时[14]。当抽头较多时,温度计码位数很多,会占用大量存储资源,且不便于下一步的数据运算处理,故常常需要将温度计码转换为二进制码。

有多种方法可以把温度计码转换成二进制码,如顺序查找法、折半查找法、累加查找法等[11-12,15-16],转换的核心思想都是通过查找温度计码中1-0(0-1)跳变的位置,达到统计温度计码中1 或0 的个数的目的。根据文献[1]的研究结果,受到进位链固有的超前进位特性影响,抽头数据的温度计码可能会发生冒泡(bubble)现象,即是抽头所在的物理位置和时间的对应关系并非严格递增,如对同一个延时的温度计码,没有冒泡的温度计码是“0000…1111…1111”,冒泡的温度计码是“0000…1101…1111”。在编码时充分考虑了冒泡的问题,使用改进的折半查找法进行编码,编码时采用对最后16 bit 温度计码直接数1 的方法解决温度计码的冒泡问题,采用pipeline 的方式进行逐级编码以减小TDC 的死时间,改进的折半查找法具有效率高、资源占用少等优点。

如前述,进位链TDC 受PVT 等因素的影响[17-18],其包含的延迟单元延时会发生变化,每次使用之前需要进行校准,建立新的查找表,TDC 的校准方法主要有平均校准和逐位(bin-by-bin)校准两种方法。平均校准的优点是可以对TDC 进行快速校准,但是所得到的只是所有延迟单元抽头的平均延迟时间,无法对TDC 中每个延迟单元进行校准,会导致较大的测量误差;码密度法可以对进位链中每一个延迟单元抽头进行逐位校准,通过码密度测试可以精确标定每个延迟单元的延时。

码密度校准方法采用和TDC 主时钟不相干的随机信号,以确保在多次测量之中,随机信号近似均匀地落在TDC 的延时路径上。研究表明[1],为了尽可能降低延迟单元的时间误差,需要增加校准次数,增加校准次就会增加校准时间、增加资源占用量,使用时需要根据项目指标要求折中考虑。校准误差和校准次数之间的关系式如式(1)所示:式中,N 为校准次数;k 为级联链抽头数目;T 为参考时钟周期,T=5 ns;σi为单个延迟单元的标准差;στ为平最大标准差。根据式(1)推导可知:本文实现的码密度校准次数为106,对应的TDC 延迟时间的最大标准差小于5 ps。

2 抽头方式研究

在Kintex-7 FPGA 平台上,通过进位链实现了TDC,使用128 个进位链,细时间测量范围大于5 ns,5 ns 为TDC 主时钟周期。进位链延时大于5 ns,这是因为:(1)可以保证TDC 输出为温度计码,不会出现全1 码;(2)进位链自身的延时受到PVT 等因素的影响,本身延时就有变化,5 ns 延迟链对应的抽头数目并不是一个固定值196(这也正是每次上电都需要自动校准TDC 延时的原因之一);(3)进位链数目为2 的幂指数,方便后续的编码解码工作等。

从图2 中可以看到,每个进位链最多可以输出4 个抽头,可以从CO0~CO3、O0~O3 共8 个抽头中的抽出任意4 个,一般采用CO0~CO3 共4 个抽头,输出编码为温度计码,可以达到较高的时间分辨,4 抽头方式的TDC的典型码宽值如图4 所示,(1)4 抽头方式的码宽差别过大,非线性较差;(2)根据文献[1]、[3]、[5]的研究成果,使用该抽头方式,受到进位链固有的超前进位特性影响,温度计码会发生冒泡现象,即在编码时需要充分考虑冒泡问题,增加了编码电路的复杂度,增加编码时间;(3)抽头过多,也会增加编码部分的资源占有量。可以看到,在4 抽头方式下,一个进位链总的典型延时约53 ps,后续的2 个抽头方式下,一个进位链总的典型延时平均约50 ps(如图5 所示),两者之间的差别是统计误差导致的,延时误差值(3 ps)也在文中提到的平均校准误差值(5 ps)分布之内。

图4 进位链4 抽头典型码宽

利用布局布线约束,研究1 个进位链只引出2 个抽头的方式(CO1、CO3),即“1tap+3tap”,如图2 所示的结构1(粗虚线框),第1 个抽头的延迟单元包括asymmetry factor+2MUXCY,第2 个抽头的延迟单元包括2MUXCY。这种2抽头方式的TDC 的非线性要强于4 抽头方式的TDC,其码宽如图5 所示,其非线性如图6、图7 所示。

图5 两种2 抽头方式的码宽

图6 两种2 抽头方式的微分非线性

图7 两种2 抽头方式的积分非线性

为了提高TDC 的线性,本文还研究了另外一种2 抽头的引出方式(CO0、CO3),即“0tap+3tap”,如图2 所示结构2(实线框),第1 个抽头的延迟单元包括asymmetry factor+MUXCY,第2 个抽头的延迟单元包括3MUXCY。这种抽头方式的TDC 的非线性较以上两种抽头方式的TDC 都好,其码宽如图5 所示,其非线性如图6、图7 所示。可以看到,“0tap+3tap”的2 抽头方式的码宽更均匀,非线性也更好一些,时间分辨率约25 ps(对应最低有效位(Least Significant Bit,LSB)),微分非线性范围为-0.84~3.1 LSB,积分非线性范围为-5.2~2.2 LSB。

在图5~图7 中可以看到,每隔100 个抽头就会有两个超宽码(ultra-wide bin),平均的码宽约为25 ps,超宽码约为110 ps。这是因为FPGA 上每个时钟域中最多含有50 个进位链结构,每个进位链引出2 个抽头,共100个抽头,之后再进位链就需要跨时钟域,超宽码就是跨时钟域时产生的,如图3 虚线框所示,本文实现的TDC共使用128 个进位链,上下跨越了3 个时钟域,虚线框即是两个时钟域的交界处,两个时钟域交界处共产生了4 个超宽码,分别是94、95、193、194。

3 结论

本文在Kintex-7 FPGA 上,通过进位链实现TDC,共使用128 个进位链,细时间测量范围大于5 ns。给出TDC码宽校准的误差计算公式,校准次数106,采用码密度校准方法对TDC 码宽进行逐位校准;研究进位链的两种抽头方式(“0tap+3tap”“1tap+3tap”),并测量其码宽、非线性等。在满足测量指标要求的情况,推荐使用“0tap+3tap”的2 抽头方式,该抽头方式的TDC 可以获得较优的非线性和较高的时间测量精度,时间分辨率约为25 ps(对应LSB),微分非线性范围为-0.84~3.1 LSB,积分非线性范围为-5.2~2.2 LSB。研究发现,进位链TDC 一旦跨时钟域,就不可避免引入超宽码(ultra-wide bin)的问题,这会降低TDC 的时间测量精度,可以采用多种方法降低这种影响,包括多链单次平均测量[1,8,10]、单链多次平均测量(wave union A、wave union B、Ripple method)[11-12]等方法。