一种基于FPGA的光学相控阵控制器的设计

宋 振,麻名蕊,赵 静,冯晴晴

(青岛工学院信息工程学院,山东青岛 266300)

0 引言

光学相控阵源于微波相控阵,是一种新型光束指向控制技术[1]。其波束具有指向灵活、扫描速度快、角度驱动范围大等特点,而且容易集成实现,因此,光学相控阵不仅广泛应用于激光显示、激光打印、机器人视觉和产品自动监测等领域,而且可应用在激光测距、目标识别、激光通信等领域。

1 光学相控阵工作原理

光学相控阵的基本构成单元是光移相器,制造光移相器的材料主要是液晶、PLZT压电陶瓷和LiNbO3(铌酸锂)光电晶体等[2]。其基本结构由若干个相控单元构成,光束指向控制的基本原理是通过电压控制调节从各个相控单元(光学移相器)辐射出的光波之间的相位关系。但由于制造光学相控阵的工艺精度限制,光学相控阵各个相控单元存在细微的差异,需要通过控制器对相控单元的控制电压精准调整,同时相控单元的响应时间也取决于控制电压的更新速率,因此输出电压的精度和更新速度是光学相控阵控制器的关键。本文研究的重点是使用FPGA作为光学相控阵控制器中ADC采集板和DAC控制板的核心器件,控制ADC数据采样和DAC高更新率电压输出。

2 系统总体设计

系统总体设计如图1所示,主要由系统供电单元、时钟分配网络、CPU工控机、ADC采集板、DAC控制板组成[3]。CPU工控机通过SFP光模块发出采集指令至ADC采集板,ADC采集板采样数据后将输出至CPU工控机处理,CPU工控机将处理后的控制参数再通过ADC采集板LVDS电路分发至4种DAC控制板。时钟分配网络负责为ADC和DAC控制板提供同步时钟。

图1 光学相控阵控制器功能结构图

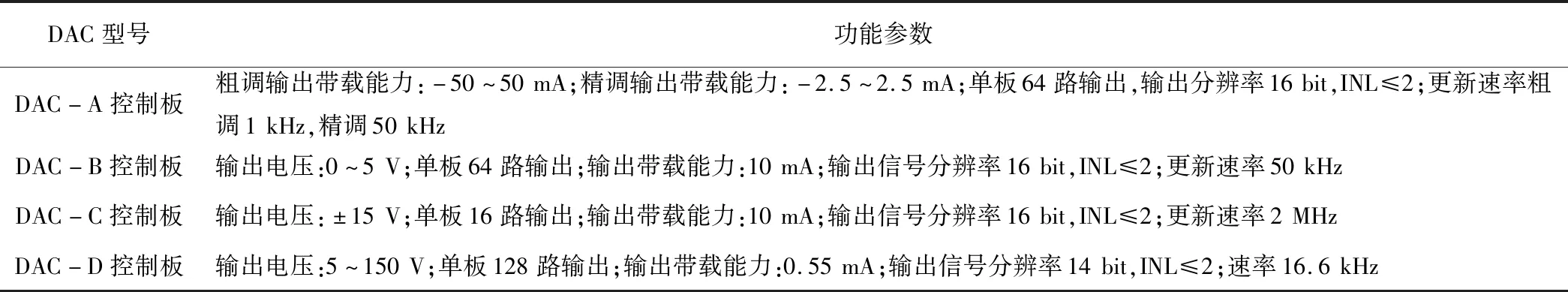

DAC控制板具体分为DAC-A、DAC-B、DAC-C、DAC-D 4种控制板,控制板功能参数如表1所示,其中DAC-A控制指向器,其他3种板负责控制移相器。

表1 DAC控制类型功能参数

3 系统功能模块设计

3.1 ADC采集板设计

ADC采集板的设计要求具备1 Mbps采样率、16 bit采样位数、32路采样通道的采集能力;并且具有和CPU工控机和DAC控制板低时延通信的能力。

根据以上要求,ADC采集控制板核心控制器件选用XC7K325T;ADC器件选用ADS9120共计32片;信号调理选用精密运放ADA4084,共计32片;通信电路选用SN65LVDS31/32为LVDS收发器件[4];时钟信号模块ADCLK946提供同步时钟;Flash芯片N25Q256A13作为备份数据存储模块,ADC采集板整体结构如图2所示。

3.1.1 ADC稳压滤波电路设计

在设计中,参考电压的稳定度决定了ADC输入的INL。由于ADS9120分辨率为16位,本设计中参考电压为5 V,所以设计中需要将参考电压的稳定度设计在0.076 mV以下才能保证ADS9120的最大性能。因此,本设计中使用REF5050AIDR稳压电路为ADS9120提供5 V的参考电压,并且同时为ADS9120的信号调理电路采集通道提供驱动电压。REF5050AIDR具有低噪声、极低漂移、高精度电压基准的特点。

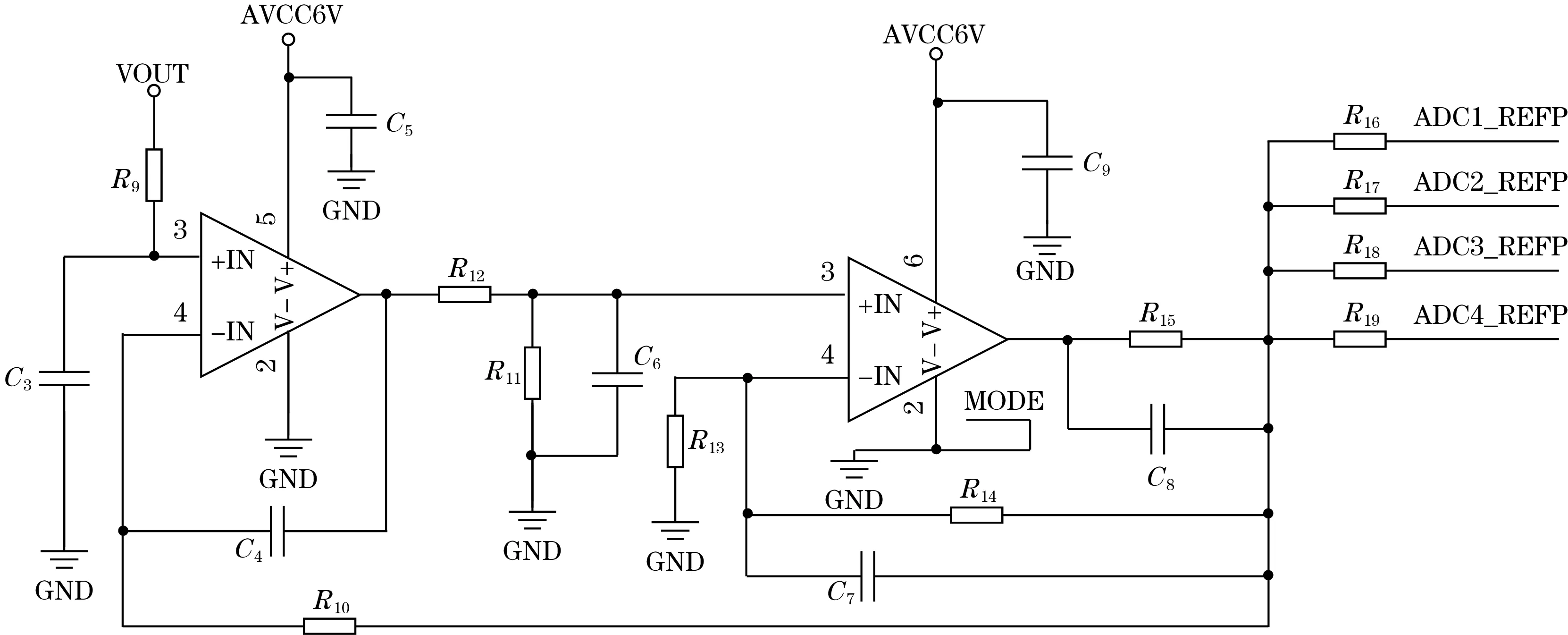

考虑到热噪声,为信号调理电路以及ADS9120的参考电压增加一级低通滤波电路[4]。低通滤波电路带宽为170 kHz,能够显著抑制热噪声的影响。图3中,VOUT为REF5050AIDR稳压电路5 V输出,经过低通滤波输出ADC1_VREF~ADC4_VREF四路电压驱动信号调理电路,滤波后电压变为稳压电路输入电压VOUT的1/4。在图4中,ADC1_REFP~ADC4_REFP为滤波后的ADC参考电压,目的是为去除电路板和稳压电路的热噪声。

图4 ADC参考电压滤波电路

3.1.2 ADC信号调理电路设计

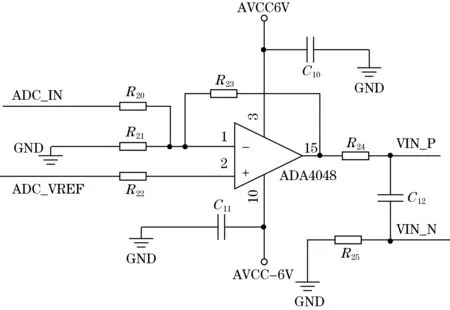

ADC采集板采集的外部信号范围为-5~+5 V,而本设计中ADS9120的输入信号范围为0~5 V,所以设计信号调理电路使用差分运放进行减法电路,转换ADC采集板输入信号以匹配ADS9120采样[5]。

图5信号调理电路VIN_P和VIN_N形成的差分输入信号VIN范围为-5~+5 V;R20等于R21且为R23的2倍,ADC_IN为采集通道,ADC_VREF为参考电压ADC_REEF的0.25倍。则ADC_IN=2ADC_VREF-0.5VIN,输入信号范围变为0~5 V。

图5 信号调理电路

3.2 DAC-A型和DAC-B型控制板设计

DAC-A型板作为指向器控制板具备粗条模式和细调模式,输出精度为16 bit。根据表1功能参数需求,DAC-A控制板选择XC7A100T-2FGG484I作为控制板的控制器,通过44个SPI接口协议IO口控制4片DAC81416芯片器件,4片DAC81416输出接64片双通道电压反馈运放AD8397。FPGA控制器通过LVDS接收ADC采集板分发的参数,再通过转换电路输出电压驱动信号[6],DAC-A型电路输出控制板框图如图6所示。

图6 DAC-A型电路输出控制板框图

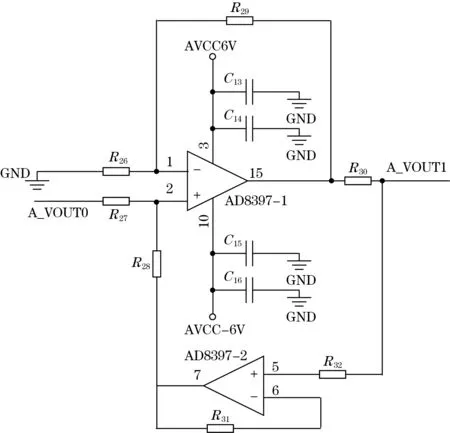

DAC81416具有16位分辨且INL小于等于1,具有灵活的输出配置和±25 mA的高驱动能力。DAC81416通过增强型50 MHz SPI接口实现自身寄存器的刷新,完成全部16通道的刷新时间为6.4 μs,满足指向输出控制50 kHz的刷新时间要求。DAC-A型板要求电流输出,所以需要在DAC81416的输出通道增加一级电压转电流电路以实现指向器电流控制。如图7所示,采用AD8397运算放大器转换电路使电阻R30两端的电压差值为A_VOUT0(DAC81416输出通道电压),则A_VOUT1输出电流的大小即为A_VOUT0与R30的比值,实现了电压转电流输出。

图7 DAC81416电压转电流电路

DAC-B型控制板要求刷新速率50 kHz,16 Bit位数、0~5 V电压输出,DAC-A型控制板的设计满足DAC-B型,所以两者原理结构基本一致。

3.3 DAC-C型控制板设计

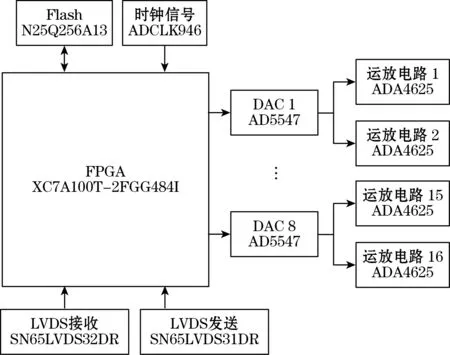

DAC-C作为移相器控制端设计需求最大难点为高更新速率2 MHz,所以相对于DAC-A型控制板不同点在于DAC和运放的设计,而其他结构选型、控制原理与DAC-A相似,如图8所示。

图8 DAC-C型电路输出控制板框图

根据表1功能参数需求,DAC-C型控制板需综合考虑DA输出的噪声性能、刷新速率以及输出范围等指标,AD5547最适合DAC-C型控制板的要求,AD5547具有2路DAC的输出,为并行数据接口。DAC-C型控制板共需8片ADC5547完成16路输出。

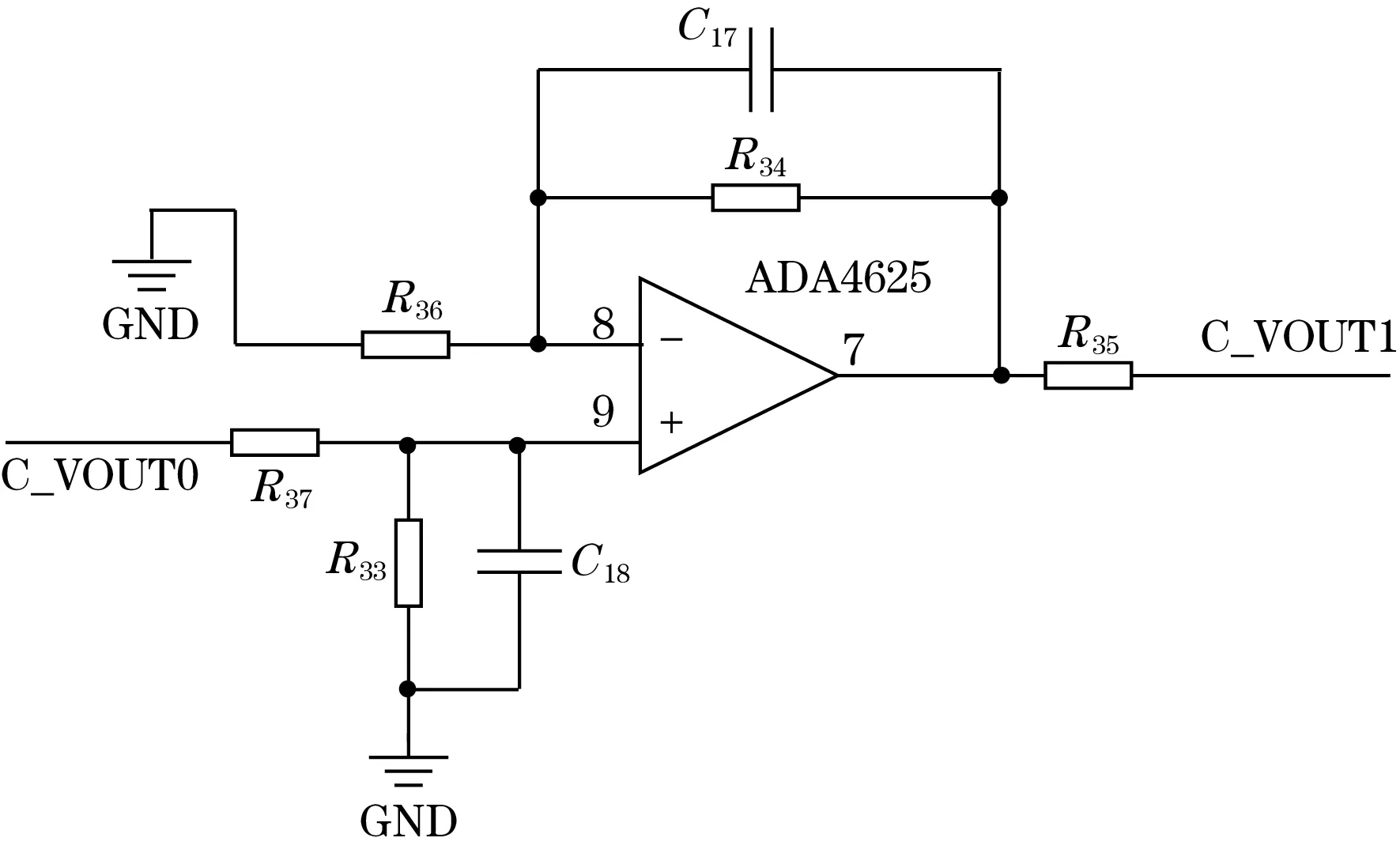

由于DAC-C型控制板的AD5547控制的电压范围为±15 V,通用器件中比较难找到15 V基准电压器件,设计使用AD5547输出±10 V,后级放大1.5倍后±15 V的输出。AD5547输出后,经AD4625放大1.5倍,放大电路如图9所示。

图9 ADA4625输出放大电路

3.4 DAC-D型控制板设计

DAC-D型控制板设计如图10所示,用于控制移相器,其最大的特点在于输出电压范围在5~150 V。

图10 DAC-D型电路输出控制板框图

本设计中使用AD5535B完成DAC输出控制,由于AD5535B的输出单路负载能力较弱,在AD5535B输出后,需使用高压精密运算放大器ADHV4702-1进行信号跟随调理提高负载能力。

3.5 CPU工控机选型

CPU工控机选择CPC-3816B标准 3U CompactPCI 主板,CPC-3816B是一款基于Intel选用六代高性能的处理器,图形核心整合 Intel®HD Graphics图形引擎,支持DX11及3D输出。

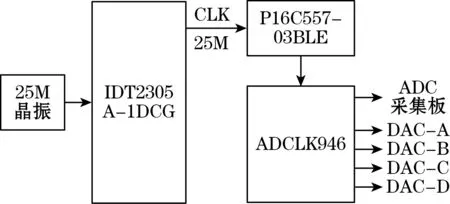

3.6 时钟分配网络设计

时钟分配网络设计见图11,设计中要求系统具有同一时钟源[7],锁相环芯片IDT-2305A-1DCG选用TTETKLJANF-25.000000高稳温补晶振,晶振最大2 ppm(1 ppm=10-6)的频偏,驱动时钟发生器芯片PIC557-03BLE产生同步时钟信号。

图11 系统时钟分配网络

为保证时钟的驱动能力,同步时钟信号经过ADCLK946时钟缓冲器分别为ADC采集板、DAC控制板提供同步时钟。

4 软件设计流程

CPU工控机通过反馈调节控制相控阵输出,反馈控制流程如图12所示。CPU工控机初始化光学相控阵控制参数,发送数据采集命令至ADC采集,ADC采集启动数据转换并将数据通过SFP光模块传输回CPU工控机。CPU工控机获得数据后,通过反馈调节算法计算出相控阵控制参数所对应的DAC数值,ADC采集板通过LVDS传输至DAC调整移相器和指向器,并通过ADC采集板再次将调整后的状态获取,依次循环达到控制目标。

图12 工控机反馈控制流程

5 实验测试与性能

取控制器DAC板电压和电流输出误差特性作为系统性能测试与评判的依据。采用100 Ω RJ711高精密标准取样金属箔电阻作为DAC输出负载,进行电压和电流测量。RJ711电阻精度0.01%温漂5 ppm,能够有效抑制温度对阻值的影响,减小测量误差。

在测试过程中,通过CPU工控机设定预设DAC电压值和电流值,控制器输出后使用高精度数据采集仪测量DAC输出的电压。需要注意的是,DAC-A型板粗调模式和细条模式下的输出电流值是由高精度数据采集仪采用差分输入方法采集负载电压值后再通过计算除以负载阻值获得。

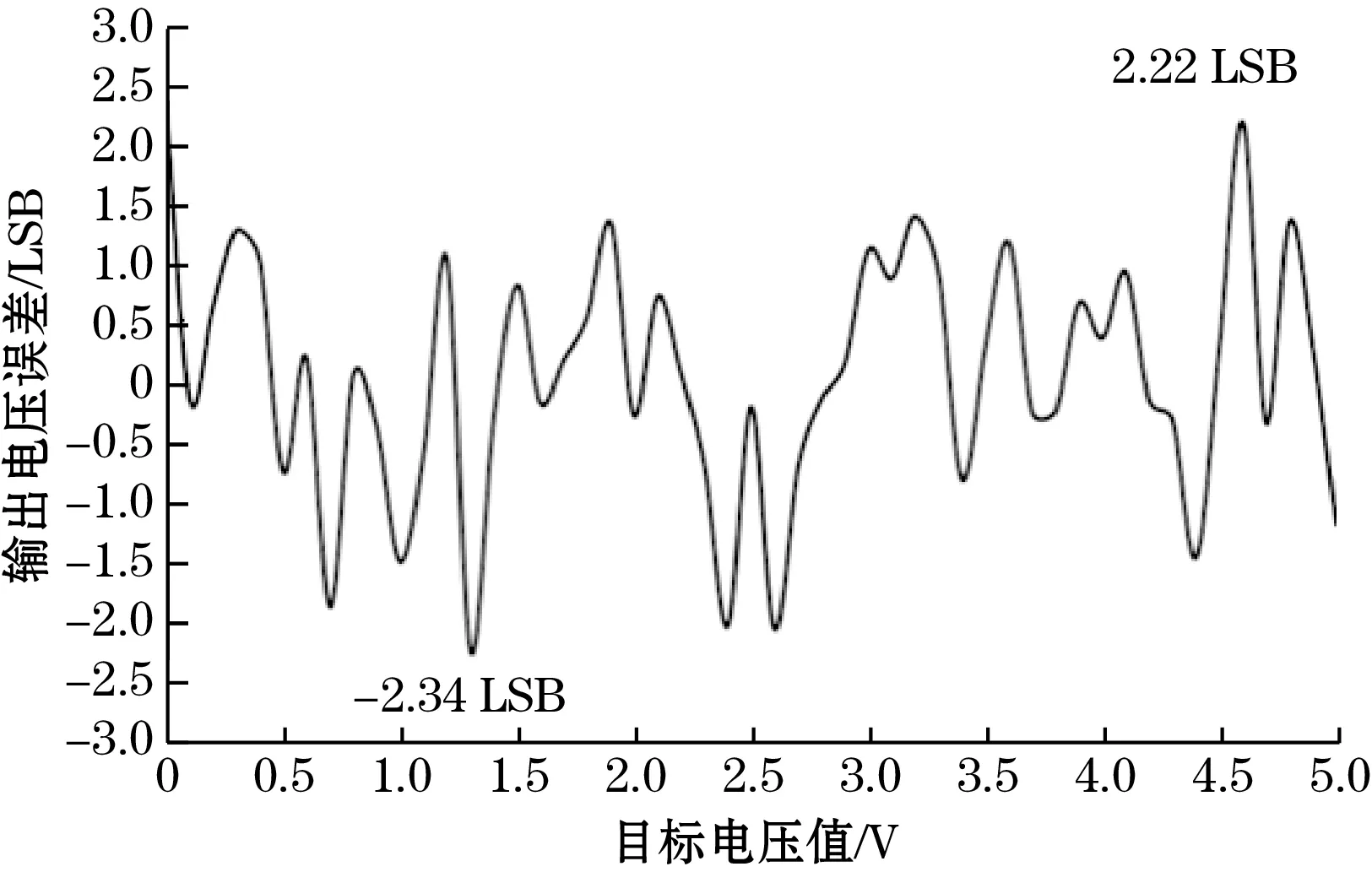

测试结果显示,将输入预设值与实际输出值进行数据处理[8],在规定的更新速率下,DAC所有控制板实际输出误差绝对值不超过2.5 LSB,且误差曲线呈随机分布,误差曲线取DAC-B型实际输出电压误差曲线(图13)为例。

图13 DAC-B型实际输出电压误差曲线

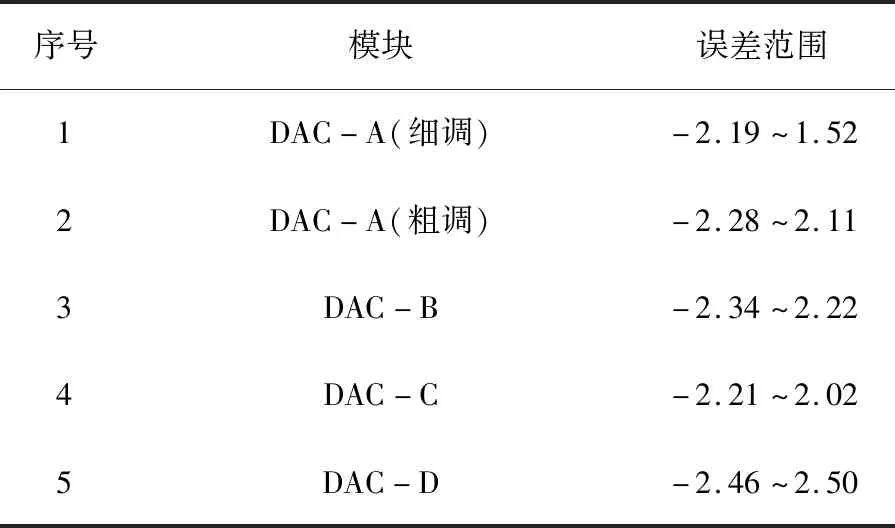

在DAC高更新速率的条件下输出电流电压线性误差范围如表2所示。

表2 DAC电流电压线性误差范围 LSB

6 结束语

针对相控阵控制器大数据量采集和高更新速率、多通道输出的问题,本文设计了基于一种FPGA的光学相控阵控制器。系统根据相控阵需求,设计了4种DAC输出板进行电压电流控制,并采用了32通道高采样率ADC采集相控阵信号进行反馈调节。实验测试,在最高2 MHz更新速率的条件下控制器输出稳定,输出误差绝对值不超过2.5 LSB,可满足光学相控阵的控制要求。