某飞行器同步数据采集存储系统设计

孟园,李孟委,张鹏

(1.中北大学 仪器与电子学院,山西太原 030051;2.中北大学电子测试技术国家重点实验室,山西太原 030051)

飞行器在进行飞行实验时,需要采集并存储飞行器的各种数据,因此通常在飞行器中设计有数据采集存储器,在飞行器飞行实验结束之后将采集存储器中的数据读出,为后续分析和研究提供数据支撑[1-3]。设计的某飞行器同步数据采集存储系统主要用于测量飞行器边界层温度、压力等参数,在对被测对象无影响或影响在允许范围的条件下,开展阵列分布式多参数测试系统一体化协同设计和高时/空分辨率测试。

在传统的数据采集存储系统中,采集通道较少,测量误差较大,存储介质主要为Flash,其速度慢、容量小、集成度低,开发时需要进行复杂的损耗控制、坏块管理以及降低误码率等操作[4-5]。eMMC 是一种内嵌式存储器,其具有速度快、容量大、集成度高、可扩展性强等优点,将Flash 存储阵列及其内部控制器封装在一起,在芯片内部完成Flash 存储阵列的损耗控制、坏块管理、ECC 校验等[6-7]。单片eMMC 存储芯片的容量最大可达256 GB,存储速度最快可达到400 MB/s,远大于Flash 存储芯片。

1 系统总体方案设计

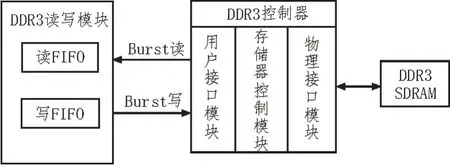

图1 系统结构框图

系统上电启动后,数据采集模块将8 路模拟信号调理后通过AD7606 模数转换芯片转换成数字信号,转换后的数字信号在FPGA 主控模块的控制下缓存在DDR3 芯片中,达到设定的数据量以后,再将DDR3 数据缓存模块中的数据存储到eMMC 存储模块中,完成数据采集及存储任务。在采存任务完成后,可通过读数盒将eMMC 存储模块中的数据读取至上位机中,并显示出原始信号的波形[11]。

2 数据采集模块设计

2.1 硬件设计

数据采集模块选用型号为AD7606 的ADC 芯片,该芯片通过5 V 单电源供电,可以同时采集8 通道真双极性模拟信号,模拟输入范围为±5 V或±10 V,且每个通道最高采样速率可达200 kHz,采样精度为16 bit,支持高速并行或串行输出方式[12]。AD7606 引脚简图如图2 所示。

图2 AD7606引脚简图

其中,AVCC 为AD7606 芯片的供电端口,供电电压为5 V;VDRIVE 为逻辑电源输入端口,决定总线的逻辑电平,输入电压为3.3 V;OS[2:0]为过采样模式选择引脚,模块需要关闭AD7606 的过采样功能,故逻辑值设置为000;PAR/SER/BYTE SEL 为数据输出模式选择端口;RANGE 为前端模拟信号输入电压范围选择端口,由于前端模拟信号经调理后电压范围为±5 V,故该端口设置为低电平;CONVSTAB 为信号模数转换开始启动端口,CONVSTA 控制通道1 至通道4,CONVSTB 控制通道5至通道8;RD/SCLK 为数据读取控制端口,CS 为AD7606 芯片的片选端口,当CS端口为低电平且RD 端口也为低电平时,使能数据输出总线DB[15:0],使转换结果输出在并行总线上。

2.2 软件设计

当AD7606芯片的CONVSTAB 端口接收到FPGA主控模块发送的上升沿时,启动对8 路模拟信号的同步采样,转换期间BUSY 信号保持高电平。当FPGA主控模块检测到BUSY信号的下降沿时,将CS信号拉低,使AD7606 芯片的数据输出总线脱离高阻抗状态,启动数据帧的传输[13]。在CS 信号处于低电平期间,产生8 个RD 的脉冲信号,分别将8 个通道的数据依次读出至FPGA主控模块中,其时序图如图3所示。

图3 AD7606时序图

3 数据缓存模块设计

3.1 硬件设计

数据缓存模块采用DDR3 SDRAM 作为高速缓存单元,完成FPGA 对eMMC 存储模块进行写操作时的数据缓存。该模块选用Micron 公司型号为MT41 J128M16HA 的DDR3 芯片,其颗粒容量为2 GB,时钟频率为200 MHz,突发长度为8,数据位宽为16 bit。芯片内部由8个Bank组成,Bank的地址总线为BA[2∶0],数据总线为DQ[15∶0]。每个Bank 的行列地址线为A[13∶0],其中行地址复用A0-A13,列地址复用A0-A9,其外围电路原理图如图4 所示。

图4 DDR3外围电路原理图

CLK 为时钟线,为增强对共模噪声的抵抗能力,故采用差分时钟的方式;将DDR3 芯片的地址总线和部分控制总线上拉至VTT;VDD 为DDR3 芯片的电源电压,采用1.5 V 电源供电,VDDQ 为DDR3 芯片I/O 口的驱动电压,也采用1.5 V 电源供电;VREFCA为DDR3 芯片地址总线、控制总线的参考电压,VREFDQ 为DDR3 芯片数据总线的参考电压,并连接至VREF 且通过0.1 μF 的电容滤波。

3.2 软件设计

为简化设计,降低开发周期和工作量,软件设计采用Xilinx 公司提供的DDR3 控制器MIG IP 核,通过MIG IP 核可以非常方便地读写DDR3 芯片。DDR3控制器MIG IP 核包含三部分:用户接口模块、存储器控制模块、DDR3 物理接口模块,FPGA 主控模块只需对接用户接口模块就可以完成DDR3 芯片的读写控制[14]。逻辑结构图如图5 所示。

图5 数据缓存模块逻辑结构图

数据缓存模块采用读写双FIFO 将DDR3 读写分离。当DDR3 读写模块中写FIFO 的数据量大于或等于128 时,会产生Burst 写请求信号,FPGA 主控模块向DDR3 控制器发送数据写命令,将写FIFO 中的数据写入DDR3 存储芯片中。数据读操作与写操作类似,当FPGA 主控模块接收到Burst读请求信号时,将DDR3 存储芯片中的数据读出至读FIFO 中。

虽然百色芒果“农超对接”的经营模式已经在部分农副产品被广泛应用和推广,虽然电商、微商、快递行业快速发展,但因破损率高、包裹赔率大,仍没有快递企业愿意承接鲜葡萄散客零买的订单。但由于葡萄鲜果的特殊性,广西快递企业不受理和接收葡萄快递包裹的订单,电商物流在葡萄鲜果产业中的应用无法获得有效推广和实施。

4 eMMC存储模块设计

4.1 硬件设计

eMMC 存储模块选用SanDisk 公司型号为SDINBDA4-128G 的eMMC 存储芯片,支持eMMC5.1协议与HS400 总线速度模式,数据读写速度最快可达到400 MB/s,eMMC 芯片的外围电路原理图如图6所示。

图6 eMMC外围电路原理图

其中,VCC 为NAND Flash 单元及其I/O 口电源电压,采用3.3 V 供电;VCCQ 为内存控制器内核及MMC I/O 口电源电压,采用1.8 V 供电;DAT0-DAT7为eMMC 芯片的双向数据线,用于FPGA 主控模块和eMMC 芯片之间的数据传输;CMD 为eMMC 芯片的双向命令线,用于FPGA 主控模块和eMMC 芯片之间的命令发送与应答;CLK 为时钟信号线,由FPGA 产生;RST_n 为eMMC 芯片的硬件复位端口,当FPGA主控模块发送低电平信号时,复位eMMC 设备。VCC 和VCCQ 分别通过4.7 μF、100 nF 的电容进行滤波处理,数据线DAT0-DAT7 通过10 kΩ的电阻上拉至VCCQ,命令线CMD 通过4.7 kΩ 的电阻上拉至VCCQ,RCLK 通过10 kΩ的电阻下拉至GND。

4.2 软件设计

4.2.1 初始化

在eMMC 设备读写数据之前,首先需要进行初始化操作,匹配eMMC 设备的信息,为其分配相对应的设备地址,并设置其速度模式、数据位宽等[15]。系统选用高速SDR 速度模式进行数据传输,数据传输过程中时钟频率为50 MHz,数据位宽为8位[16]。eMMC 初始化流程图如图7 所示。

图7 eMMC初始化流程图

eMMC 初始化具体操作流程为:1)发送eMMC 设备复位命令CMD0,复位eMMC 设备,进入空闲(Idle)状态;2)发送OCR 寄存器获取命令CMD1,匹配工作电压和寻址模式,进入准备(Ready)状态;3)发送CID寄存器获取命令CMD2,获取设备信息,进入设备识别(Identification)状态;4)发送RCA 分配命令CMD3,对eMMC 设备进行地址分配,进入设备待机(Standby)状态;5)发送CMD9 命令,获取CSD 寄存器的值,得到eMMC 设备的芯片容量、数据块长度等信息[17];6)发送设备选定命令CMD7,选中eMMC 设备,进入传输(Transfer)状态;7)分别发送参数不同的CMD6命令,切换eMMC 芯片的输入时钟,设置eMMC 芯片的工作模式、总线宽度等;8)FPGA 主控模块向eMMC芯片发送CMD19 命令,对eMMC 芯片开始总线测试,当FPGA 主控模块接收到eMMC 芯片返回的响应时,发送总线测试数据;9)FPGA 主控模块再次向eMMC芯片发送CMD14 命令,读取eMMC 芯片返回的数据,然后判断数据是否正确,若正确则进入传输(Transfer)状态,若错误则重新进入空闲(Idle)状态。

4.2.2 数据写操作

eMMC 芯片的数据写操作包含单块写、多块写两种方式,该系统采用单块写方式[18]。eMMC 数据写流程如图8 所示。数据写操作开始后,FPGA 主控模块向eMMC 设备发送CMD16 命令配置eMMC 设备的数据块长度为512 B。然后FPGA 主控模块发送CMD24 单块写命令,若eMMC 设备响应错误或超时,FPGA 主控模块则再次发送该命令。当命令响应正确时,FPGA 主控模块往eMMC 设备中写入数据及CRC 校验值,eMMC 设备内部同样会对写入的数据进行校验。若FPGA 主控模块和eMMC 设备的CRC校验结果不一致,则需要重新发送CMD24 单块写命令,若校验通过,则发送设备状态查询命令CMD13。当FPGA 主控模块检测到Busy 信号为高电平时,则继续发送设备状态查询命令CMD13,直到FPGA 主控模块检测出Busy 信号为低电平时,表示eMMC 设备单块写操作完成。

图8 eMMC数据写流程图

4.2.3 数据读操作

eMMC 设备数据读操作与写操作类似。数据读操作开始后,FPGA 主控模块向eMMC 设备发送CMD16 命令配置eMMC 设备的数据块长度为512 B。然后发送包含读起始地址参数的CMD17 单块读命令,若响应错误或超时,FPGA 主控模块则再次发送该命令。FPGA 主控模块从eMMC 设备中读取的单块数据包含CRC 校验值,FPGA 主控模块将读取的数据进行CRC 校验,然后将FPGA 主控模块的校验值与eMMC 设备的校验值进行比对[19]。若校验结果一致则表明读取的数据正确,eMMC 设备单块读操作完成;若校验结果不同,则需要重新发送CMD17单块读命令。

5 实验测试与分析

为了验证系统的功能及可靠性,首先利用Vivado软件自带的在线逻辑分析仪分别对数据采集模块、eMMC 存储模块进行了调试与分析,然后对整个系统进行了实验测试。

5.1 数据采集模块逻辑分析

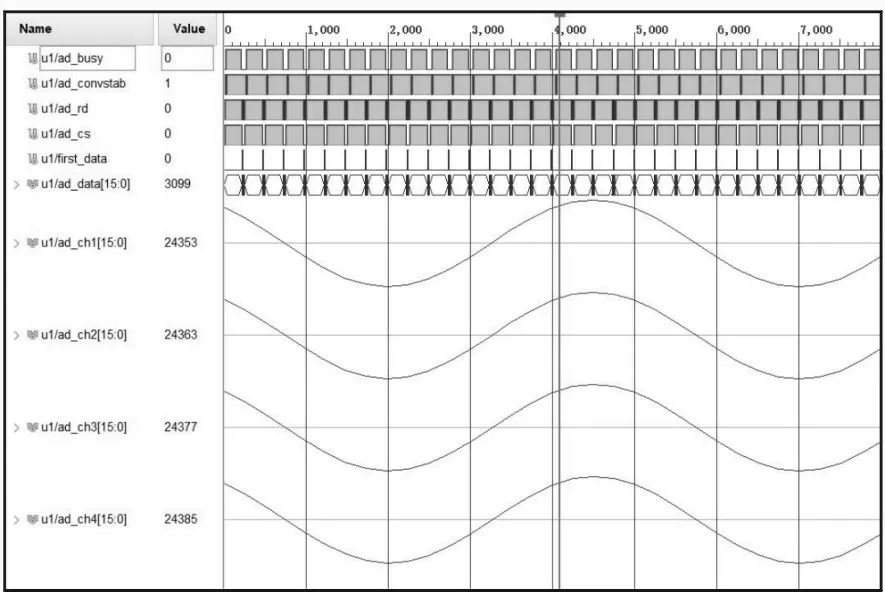

将数据采集模块接入峰值为5 V、频率为10 kHz的正弦波信号,通过在线逻辑分析仪显示出各个信号的变化情况以及各个通道的数据波形。数据采集模块逻辑分析图如图9 所示。

图9 数据采集模块逻辑分析图

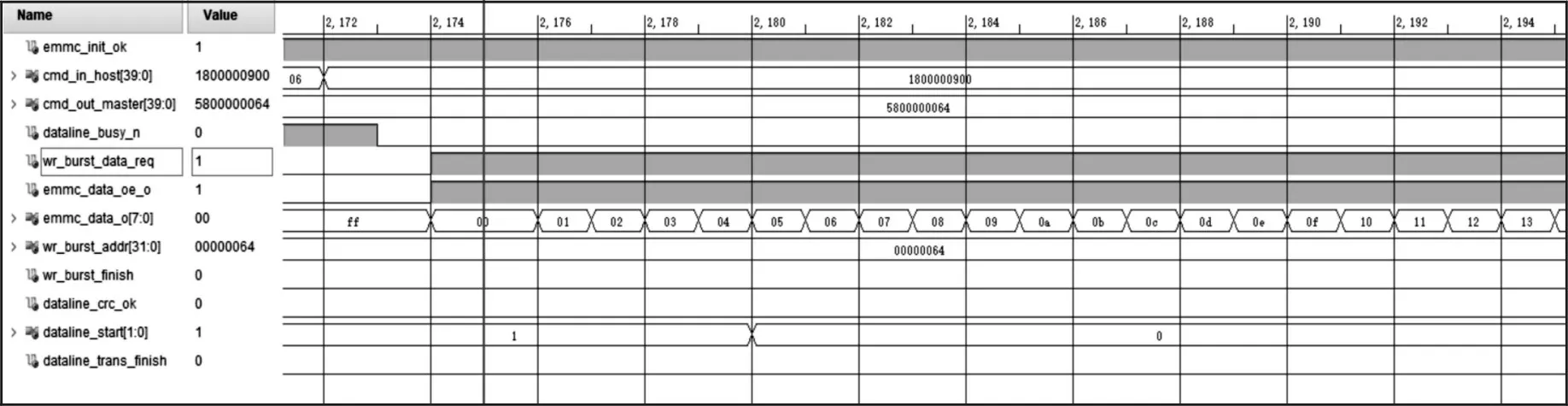

5.2 eMMC存储模块逻辑分析

eMMC 存储模块写入的数据通过计数器生成自加数来模拟产生,有利于发现数据传输中是否出现错误。eMMC 存储模块的数据写逻辑分析图如图10所示,数据读逻辑分析图如图11 所示。当写请求信号(wr_burst_data_req)拉高时,eMMC 数据线使能信号(emmc_data_oe_o)拉高,eMMC数据线(emmc_data_o)先变为低电平再依次写入数据,写入数据块的地址(wr_burst_addr)为0x64。当读请求信号(rd_burst_data_req)拉高时,eMMC 数据线(emmc_data_i)先变 为低电平,再依次读出数据。

图10 eMMC数据写逻辑分析图

图11 eMMC数据读逻辑分析图

5.3 系统测试

首先,在8 个通道的输入端分别接入-1 V、+1 V、-2 V、+2 V、-2.5 V、+2.5 V、-3 V、+3 V 的标准电压信号,通过采集存储系统多次测量计算出其实际测量电压均值,并将测量电压均值与标准电压值进行对比,结果如表1 所示。从表中可看出其相对误差范围在0.2%以内。

表1 标准值和测量值对比表

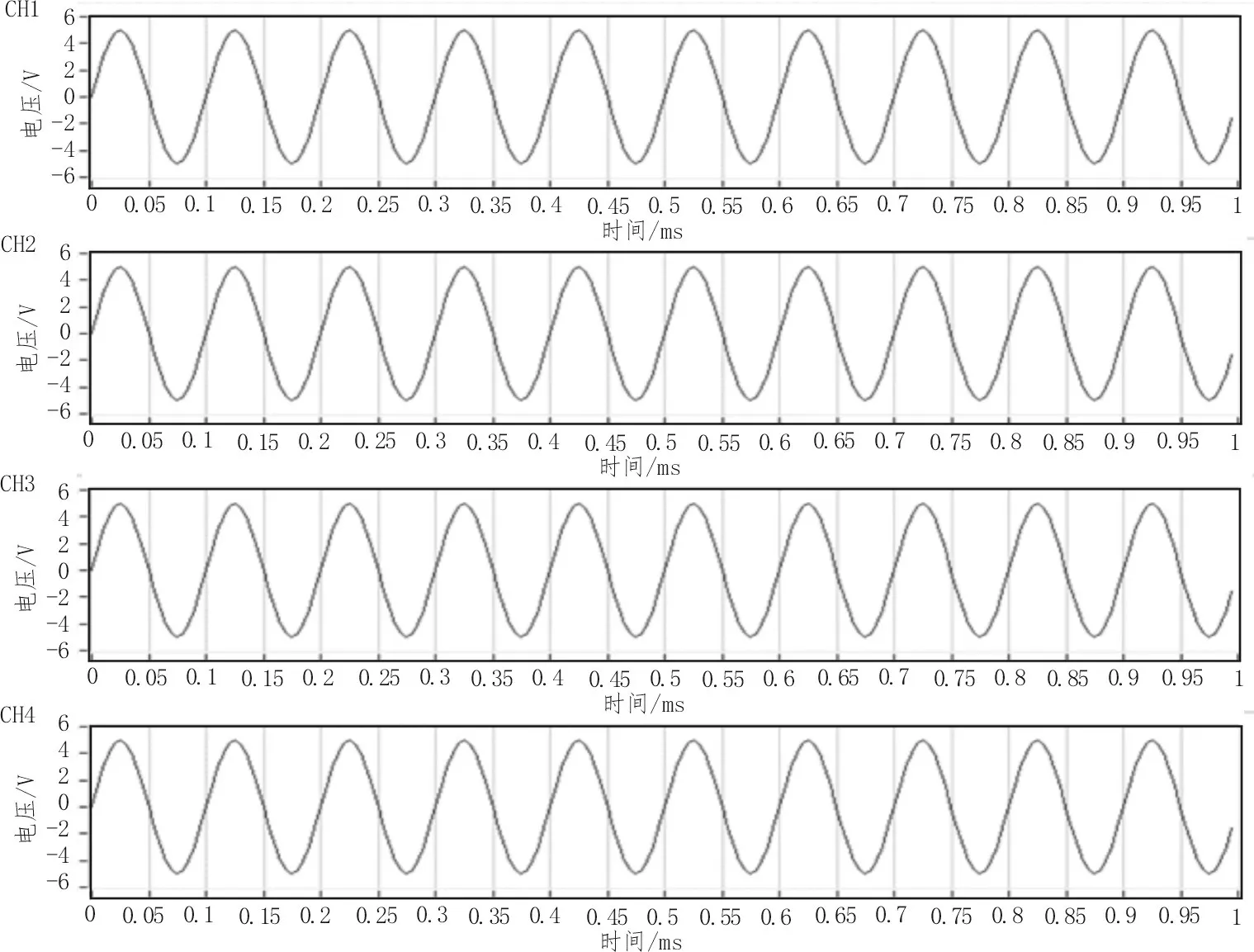

然后,利用信号发生器产生电压峰值为5 V、频率为10 kHz 的正弦波信号接入系统的信号输入端,通过读数盒将存储在eMMC 设备中的数据读取到上位机中,并显示出采集的模拟信号,其波形如图12所示。从图中可以看出,该同步数据采集存储系统可以准确采集并存储电压峰值为5 V、频率为10 kHz的正弦波信号,表明该系统具有可靠的传输性能。

图12 上位机波形显示界面

6 结论

文中介绍了一种基于FPGA 和eMMC 的多通道同步数据采集存储系统,用于采集并存储某飞行器边界层温度、压力等参数。选用单片多通道同步采样ADC,实现了8 通道模拟的同步采集,保证了系统通道间的同步性;选用eMMC 作为存储单元,实现了长时间、大容量的数据存储,也解决了传统以Flash为存储单元的复杂的坏块检测与系统管理等问题。该系统具有测量误差小、存储容量大、存储速度快、集成度高、可扩展性强等特点。测试结果表明,该系统能够同步采集存储及显示8 通道模拟信号,采样频率为200 kHz,模拟输入范围为±5 V,误差范围可控制在0.2%以内,具有良好的可靠性和扩展性。