基于Zedboard硬件平台的假目标干扰信号的实现

刘云涛,陆满君,张文旭,胡建波

(1.哈尔滨工程大学信息与通信工程学院,黑龙江 哈尔滨 150001;2.上海无线电设备研究所,上海 201109;3.哈尔滨工程大学工业和信息化部先进船舶通信与信息技术重点实验室,黑龙江 哈尔滨 150001;4.中国人民解放军91411部队,辽宁 大连 116041)

0 引 言

在现代战争逐步趋向于信息化战的大环境下,为了应对雷达侦察技术,弹载或者机载雷达系统为对抗敌方雷达的搜索,在截获敌方雷达信号的同时要对敌方雷达进行干扰,以保护己方不被跟踪。随着雷达技术的不断发展,数字射频存储(digital radio frequency memory,DRFM)技术很好地解决了对雷达信号接收和发射设备要求较高的问题。多假目标作为一种有效的干扰方式,被广泛应用于弹载或者机载雷达中。本文介绍了一种基于FPGA的假目标干扰信号实现的方法,相比于传统实现方式,本方法既可实现密集假目标压制干扰,也可实现多假目标欺骗干扰,具有灵活、快速的特点。

在实际应用中,雷达干扰信号的生成需要借助硬件平台实现,所以要求硬件平台对雷达信号的处理要快速、精确。现场可编程逻辑门阵列(field programable gate array,FPGA)具有资源丰富、集成度高的优点,其时序和逻辑功能强大,对于数字信号的处理具有高速、精确的优点。刘佑林等[1]介绍了FPGA在信号处理中的应用,这种数字处理系统保持了硬件器件速度快的优势,同时也具有软件系统的灵活性以及并行采集、处理多种参数的能力。

目前诸多雷达干扰系统主要采用DRFM技术[2-4]进行设计和实现。DRFM技术广泛用于干扰机工作体制设计中,能对截获的雷达信号的脉内特征进行精确存储和复制,使发射的干扰信号与雷达回波信号具有相参性,能为干扰相参雷达提供保证。同时,通过对截获信号采用特定的调制方式,可产生多种样式的干扰,从而对辐射源实现特定的干扰。基于延时叠加的间歇采样转发干扰的方法是目前使用较多的干扰生成方法。间歇采样重复转发是指采样一个脉冲片段后,读出当前存储的信号,并进行若干次转发。若在此基础上进行延时叠加,通过控制延时量和叠加次数可以生成数量更多、距离更远的目标,实现多假目标的干扰效果。

1 数字射频存储技术基本原理

DRFM一共由6个基本部分组成:下变频模块、模数转换器(analog-to-digital conversion,ADC)、存储调制器、数模转换器(digital-to-analog conversion,DAC)、上变频模块和控制器。DRFM的主要工作流程为:首先,将接收天线截获到的雷达信号进行下变频得到中频信号;然后,模数转换模块会对中频信号进行采样,并将得到的数字信号存入到存储器中,经过一系列算法处理之后,数字信号经过数模转换模块得到模拟中频信号;最后,经过上变频转换后由发射天线发出。其结构如图1所示,此结构可以有效降低对采样设备的要求,同时可以精确复制雷达信号的脉内特征。

图1 DRFM基本组成结构Fig.1 Basic composition of DRFM

2 间歇采样叠加转发干扰的方法

2.1 延时叠加干扰原理

延时叠加干扰[5]是一种常见的干扰信号生成方法。干扰系统将收到的雷达信号进行存储,然后根据人为设置进行延时叠加,产生若干不同距离信息的假目标信号[6-7],可对敌方雷达起到欺骗或者压制的作用。这种干扰方式可在DRFM结构的基础上进行实现,其结构如图2所示。RF(radio frequency)输入信号经过下变频,得到IF(intermediate frequency)信号;经过ADC采样、信号存储及处理、DAC输出,得到处理后的IF信号;最后经过上变频,将干扰信号搬移到射频段,得到RF输出信号。

图2 基于DRFM的延时叠加干扰组成结构Fig.2 DRFM-based delay superimposed jamming composition structure

设截获的雷达信号为S(t),经过一次延时调制后发射出去的欺骗干扰信号为J(t),回波信号通过雷达接收机匹配滤波器h(t)[8]后输出的信号为y0(t)。由于h(t)是一个线性时不变系统,因此干扰信号经过脉压输出后的信号形式如下:

式中:A为幅度调制系数;t0为延时时间。由式(1)可以看出,干扰信号经过脉冲压缩处理结果与原信号的脉冲压缩处理结果是相同的,只是幅度和延时时间有所不同。当t0>0时,假目标位于真目标后方;当t0<0时,假目标位于真目标前方。

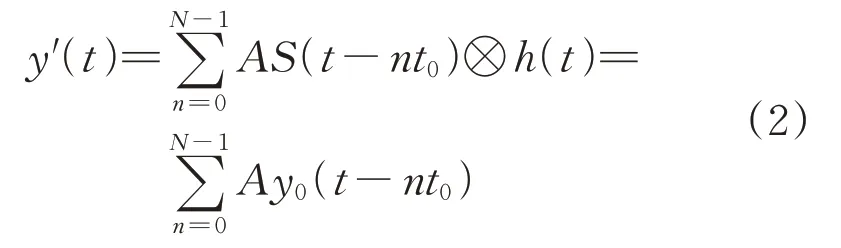

由分析可知,经过多次延时叠加的输出信号经过匹配滤波器的输出形式为

式中:N为延时叠加次数。由式(2)可以看出,当延时时间t0较小、延时叠加次数N较大时,会产生密集的假目标,真实目标回波会位于假目标回波群中。当雷达干扰系统的输出功率大于目标的回波功率时,真实目标回波会淹没在假目标回波群中,形成了密集假目标压制干扰。当延时时间t0较大、延时叠加次数较小时,就会产生多个位置的假目标雷达回波,形成了稀疏假目标欺骗干扰。

2.2 间歇采样叠加转发干扰

间歇采样转发干扰[7]近些年已经有大量的研究成果和实战应用,这种方法避开了干扰机收发天线隔离的问题,使天线之间不会相互影响。对雷达信号进行等间隔或者非等间隔的脉内采样,根据间歇采样参数信息和转发方式信息,只有叠加转发时可以在真实目标后产生若干假目标,若在叠加转发的基础上附加多普勒频移,即可在真实目标之前产生假目标。在真实目标前后产生若干假目标对真实目标有很强的掩盖作用,因此是一种实现假目标干扰的非常实用的方法。间歇采样转发干扰的方法主要有直接转发、重复转发、循环转发3种转发方式,本文采用的是在重复转发的条件下,将信号进行延时叠加,实现基于延时叠加的间歇采样转发干扰。利用DRFM可以对存储的雷达信号进行反复读取和恢复的特点,结合FPGA信号处理快速、精确的优点,在FPGA内部实现延时叠加的方法,可以生成特定数量的假目标干扰信号。这种干扰方式是在重复转发的基础上实现的,主要流程是转发多个采样信号时段叠加后的信号,雷达脉冲结束之后还会继续转发。其每一级转发的原理如图3所示,其中,T0表示采样周期。

图3 基于延时叠加的间歇采样干扰原理Fig.3 Intermittent sampling interference principle based on delay superposition

图3为间歇采样叠加转发干扰的示意图,为了方便分析该叠加算法的原理,将图3的收发过程分为两个干扰时段的叠加,分别如图3(a)、(b)所示。图3(a)为间歇采样重复转发干扰的收发示意图,图3(b)可以看成是将图3(a)的转发信号延时T0后再转发的干扰信号。在DRFM系统中,此部分是在数字处理模块中实现的。本文中采用Zedboard硬件处理平台,在内部调用存储器IP核对信号进行缓存,之后将信号从存储器中读取,通过FIFO(first in first out)核构成的延时叠加结构,即可实现对回波信号的延时叠加处理。设输入信号为ys(t),经过延时叠加后的输出为ys'(t),二者之间的关系式为

由式(3)可推出图3(a)中的干扰信号经过雷达匹配滤波后的输出信号为ys(t),将其代入到式(3)中,得到图3(c)中的干扰信号经过雷达匹配滤波后的输出信号分别为ys'(t)。此时式(3)中的τ=T0。因此,图3(c)中间歇采样叠加转发后的干扰信号输出形式如下:

式(4)表示一级延时叠加的信号输出。

若延迟叠加的次数为N,延迟转发的最小时间为T0,则间歇采样叠加转发干扰经过匹配滤波后的输出可以表示为

式(5)表明叠加次数N越大,ys'(t)中包含的回波信号的时延分量ys(t-nT0)就越多。每个时延分量可认为是一个假目标,所以N越大产生的假目标数量就越多,因此产生的干扰距离就越远。由于考虑到天线收发分时问题,叠加延时的最小时间必须为间歇采样周期的整数倍,即

由于信号进行延时叠加,干扰机会在信号的脉冲结束之后继续转发间歇信号,此时采样阶段转为侦察阶段,此阶段不会对信号进行采样存储,只对之前存储的信号进行转发,直到将存储的信号段发完为止。由式(5)可知,可以通过控制延迟时间T0和叠加次数N来使干扰机产生不同的干扰效果,当T0值较小、N值较大时,该干扰算法产生的干扰信号以真实目标为起始,在真实回波目标后产生大量的假目标信号群,假目标之间会产生混叠,压制干扰距离较远,形成密集假目标压制干扰效果。若添加一定的多普勒频移,则可在真实回波目标的前方产生假目标群,二者联合可在真实目标两侧产生假目标群,实现更远距离的压制效果。当T0值较大、N值较小时,该干扰算法产生的干扰信号为在真实回波目标后形成若干假目标[9],假目标之间有可能不会产生混叠,这由间歇采样的收发占空比决定。图4为无混叠效应的延时叠加示意图,其中延迟时间为4T0。如图4(c)所示,由于延迟时间较长,叠加后的信号没有发生混叠,假目标数量变少,但是干扰距离更远,形成假目标欺骗干扰的效果。

图4 无混叠的延时叠加示意图Fig.4 Schematic diagram of delay superposition without aliasing

2.3 延时叠加的FPGA设计

延时叠加是在FPGA内部通过编程实现的[10],其结构如图5所示。经过延时器后得到延时后的信号,原始信号与延时后的信号经过加法器进行相加,得到一级延时叠加的信号。本文选用的FPGA硬件平台为Xilinx公司提供的Zedboard系列开发平台,本文在Zedboard硬件平台上使用Verilog语言进行编程,在Vivado编程环境下调用FIFO核[11]作为延时器,设置FIFO核的深度,实现特定时间的延时。然后再调用加法器IP核,将原始信号与延时后的信号进行相加,即可实现一级延时叠加。本文采用8级不同深度的FIFO核级联的形式,实现8级延时叠加,FIFO延时叠加级联结构如图6所示。

图5 延时叠加结构Fig.5 Delay stack structure

图6 FIFO延时叠加级联结构Fig.6 FIFO delay superposition cascade structure

此级联结构的优势在于假目标数量是按照2n的关系产生的,相比于一般的延时叠加可以产生更多的假目标数目。本文调用8级延时叠加结构,最多可产生28=256个假目标,若只选择其中n(n<8)级,则可产生2n个假目标,假目标数量可以通过程序实现灵活控制。

3 干扰信号的仿真及工程实现

3.1 假目标干扰的仿真

设输入信号为载频为10 MHz、脉宽为20 μs、脉冲重复周期为200 μs的脉冲调制信号,经过若干级FIFO延时叠加,可得到密集假目标压制式干扰和稀疏假目标欺骗式干扰。

仿真程序中共添加8级FIFO结构,调用全部8级FIFO进行延时叠加,可产生256个密集假目标,形成密集假目标压制干扰,如图7所示。

图7 密集假目标压制干扰时域信号Fig.7 Suppressing jamming time domain signal with dense false targets

本文中稀疏假目标欺骗式干扰选择了最后3级FIFO进行延时叠加,可产生8个假目标,其干扰信号的时域波形如图8所示。

图8 多假目标欺骗干扰仿真时域信号Fig.8 Multi-decoy jamming time domain signal

3.2 假目标干扰的工程实现

3.2.1 硬件平台简介

Zedboard是基于Xilinx ZynqTM-7000的扩展式处理平台,如图9所示,主板上采用的是Zynq-7000系列中的XC7Z020-CLG484 FPGA,实现了双核Cortex-A9 MPcore和最新的28nm 7系列可编程逻辑紧密集成。其中,双核Cortex-A9 MPcore,主频达到667 MHz,板载512 MB内存,堪比一个便携设备的ARM平台。板级接口资源丰富,适合很多场景的应用,且成本很低,对于信号处理场景的应用具有响应速度快、程序设计灵活以及资源丰富等优势。如果后续需要对信号进行分选、分类、识别以及可视化等操作的话,内嵌双核的Cortex-A9 MPcore可满足各种算法的需求。

图9 Zedboard硬件开发平台Fig.9 Zedboard hardware development platform

3.2.2 基于硬件平台的假目标干扰工程实现

假目标干扰的中频信号可在硬件平台实现。本文采用基于Zedboard的FPGA硬件开发平台对干扰信号进行实现,利用此硬件开发平台对信号响应快速的特点,可实时对雷达信号进行干扰调制处理。在FPGA中通过调用FIFO核和加法器IP核,实现延时叠加。将信号源输出设置为载频为5 010 MHz、脉宽为20 μs、脉冲重复周期为200 μs的脉冲调制信号,经过DRFM系统下变频后可得到载频为10 MHz的信号。由于Zedboard开发平台不具备AD模块,所以在内部调用DDS模块,产生一个载频10 MHz、脉宽20 μs、脉冲重复周期200 μs的脉冲调制信号来模拟下变频后的雷达信号。信号波形如图10(a)和(b)所示,其中图10(a)为脉冲调制信号的周期波形,图10(b)为脉内信号波形。

图10 DDS产生的脉冲调制信号Fig.10 Pulse modulation signal generated by DDS

由于Zedboard开发平台不具备DA模块,所以采用Vivado自带的ILA核对干扰信号进行观察,如图11~12所示,分别为密集假目标干扰的时域信号和稀疏假目标干扰的时域信号。密集假目标压制干扰的仿真和工程实现如图7和图11所示,干扰信号在时域上表现为在一片区域内信号叠加形成的类似噪声压制的形式,信号形式基本一致。稀疏假目标欺骗干扰的仿真和工程实现如图8和图12所示,经过3级FIFO延时叠加结构,共产生了8个假目标,对敌方雷达形成欺骗干扰效果。通过对比,仿真与工程实现的信号基本一致。

图11 密集假目标压制干扰实际信号Fig.11 Dense false targets suppress jamming actual signal

图12 多假目标欺骗干扰实际信号Fig.12 Multi-false target deception jamming actual signal

4 结束语

本文提出并实现了一种基于Zedboard硬件平台的雷达假目标干扰实现方法,主要介绍了干扰生成方法、干扰算法、软件仿真以及硬件实现,在Zedboard硬件平台上实现了密集假目标压制干扰和稀疏假目标欺骗干扰的中频时域信号。相比传统的干扰方法,本方法在硬件实现上选用了Xilinx公司已经上市的Zedboard硬件处理平台,具有成本低、功能强大等优点。同时,利用FPGA器件逻辑功能强大的特点,使用延时叠加的方式实现干扰信号的生成,针对敌方雷达的假目标干扰提供了一套很好的应对方案。FPGA的Verilog语言时序精度高,可对截获信号进行实时、快速处理,并且可直接应用于DRFM系统中,灵活方便,在电子战领域中的应用具有一定的优势。