基于CPU+GPU的图像处理模块设计

钱军琪,许梦芸,樊 超

(航空工业西安航空计算技术研究所,陕西 西安 710065)

0 引言

随着数字视频时代的到来,图形图像处理作为数字化的重要组成部分越来越重要,特别是支持二维/三维高清图形图像显示技术已经成为业界的研究热点。本文针对数字视频处理技术的特点提出了一种能够支持综合显示界面绘制、二维/三维数字地图加速等功能的硬件解决方案[1-2]。

1 总体结构及硬件设计

1.1 总体结构

图像处理模块系统如图1所示,显示输出的分辨率可达1 600×1 200,视频帧不低于30帧每秒[2]。由于要同时完成界面绘制、二维/三维数字地图生产等复杂工作,因此对处理平台的性能有较高的要求,经过技术分析,选用CPU+GPU的处理构架。CPU 选用飞思卡尔公司的高性能低功耗PPC构架T系列处理器,负责系统管理调度、数据存储加载、通信管理等工作;GPU选用国内厂商景嘉微电子的JM系列图形处理器,负责图形图像绘制和加速工作。

模块的核心是中央处理器Txx和图形处理器JMxx,CPU和GPU之间通过PCIE-PCI桥芯片连接,完成指令发送和数据传递。GPU完成图形绘制后通过两路DVI接口进行视频输出,一路DVI输出综合显示界面,一路DVI输出二维/三维数字地图。数字地图原始数据存储在电子盘内,CPU通过内置SATA接口对电子盘进行访问,读取数据后送入GPU进行后续图形处理。同时模块预留了以太网、USB、VME等通信总线接口,用于和其他模块及外设通信。

1.2 CPU电路设计

Txx提供2个单线程的e5500内核,基于Power Architecture®技术构建,主频最高可达1.2 GHz,e5500内核提供256 kB的高带宽、低延迟的共享平台缓存,这样在运行独立的操作系统时,能保证很高的处理效率。CPU有1个64位的DDR3L控制器接口,有效利用了存储器带宽。处理器使用e5500内核和高速内部互联技术来平衡处理器的性能与IO系统的吞吐率。配置了高性能PCI Express接口,共提供4个PCI Express2.0控制器,采用PCI-E总线实现板级高性能设备的串行点对点互连;2个SATA接口,支持1.5 Gb/s和3.0 Gb/s传输速率。配置了2个以太网控制器,支持10 Mbps,100 Mbps,1 000 Mbps速率通信。此外,Txx还集成了2路UART接口、中断控制器、2个8通道的DMA控制器、GPIO等资源。

采用该处理器,利用其丰富的外围接口,可方便实现SATA、以太网、PCIE等接口,其内部功能如图2所示。

1.2.1 存储器电路设计

模块提供独立的存储器系统,通过CPU进行管理,包括:DDR3L SDRAM、系统FLASH、用户FLASH、NVSRAM。

图2 Txx处理器内部结构

模块中CPU处理器提供独立的DDR3L或DDR4存储器接口,模块设计为DDR3L接口。处理器集成的DDR3存储控制接口支持72位数据宽度(其中8位为数据校验位),可以直接对接DDR3-800的存储器。DDR3 SDRAM存储器采用Micron公司的MT41K256M16HA-125 AAT DDR3存储器,每片存储器容量512 MB,DDR3L SDRAM时钟频率最大可达800 MHz,设计降频到600 MHz工作。存储器地址从0开始,地址范围为:0x0~0x7fffffff。

处理器提供容量为256 MB系统FLASH,采用1片S70GL02GS11FHI010实现,按16位工作方式,通过CPU的IFC总线进行访问。系统FLASH用于CPU模块的启动,系统FLASH上驻留BIT测试程序、FLASH在板编程程序、操作系统等系统软件。

处理器提供512 kB的NVSRAM,采用8位数据宽度访问,地址空间连续,E2V公司的EV2A16AMNYU35,器件容量为256 k×16 bit,工作电源3.3 V。NVSRAM用于掉电保护,每片内有SRAM和EEPROM,掉电时利用芯片内部控制由SRAM中的数据写入EEPROM中,上电时自动从EEPROM中写入SRAM中,恢复掉电时的数据。

1.2.2 PCIE总线接口设计

处理器集成1个高速外部接口复合体(HSSI),包含8路SerDes laneA--laneH,SerDes模块包含串行器/解串器和物理编码子层PCS(Physical Coding Sublayer)的功能。高速接口复合体支持5种类型的接口。上电过程中,由配置字RCW的SRDS_PRTCL_S1位决定SerDes配置的接口协议类型,模块中SRDS_PRTCL_S1位初始化为0x06,SerDes配置为宽度为×4线的PCI-E接口协议。PCI-E接口的速率由配置字RCW的SRDS_DIV_PEX位决定,支持2.5 G和5 G两种线速。本设计中将处理器的SerDes接口配置为2路PCIE接口。提供2路标准PCIE接口,总线时钟100 MHz。

1.2.3 调试以太网接口

处理器集成了2个独立的以太网控制器(eTSEC)。每个接口都支持10M/100M/1 000 M以太网和IEEE 802.3网络协议,并且配置通用8位/16位FIFO接口。eTSECs支持MII和RGMII标准外部以太网收发器接口。

模块采用处理器的1路eTSECs接口,用于处理器的调试端口。外部连接10M/100M/1 000M以太网PHY电路,通过以太网变压器从模块底板连接器引出,用于模块的调试。

1.3 GPU电路设计

JMxx是长沙景嘉微电子股份有限公司推出的一款高性能、低功耗的图形处理芯片(GPU),具有完全自主知识产权。GPU采用全新架构设计,基于65 nm CMOS工艺实现,可广泛应用于有高可靠性要求的图形生成、显示等领域。GPU能够高效完成2D,3D的图形加速功能[3],提供了多种外设接口,在芯片上集成了1 GB的DDR3存储器,支持两路多种格式的外视频在图形上进行开窗、缩放、旋转以及叠加显示。芯片的主要功能如图3所示。

图3 GPU总体结构

JMxx的主机接口为PCI接口,CPU不直接支持PCI接口,因此在电路设计中采用桥芯片进行总线转换,将CPU的PCIE接口转为PCI接口,进而完成和GPU的通信,完成指令和数据的传送。GPU可直接将绘制的图形通过DVI显示接口输出。

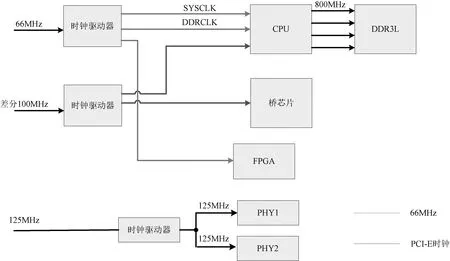

图5 时钟电路

1.4 FPGA电路设计

CPU模块采用Xilinx公司的Spartan-3 XC3S200AN-4FTG256I实现模块内部控制逻辑以及局部总线接口转换。该FPGA具有200 k系统门电路、448个CLB单元、195个IO等丰富资源,兼容TTL(LVTTL)、CMOS(LVCOMS)等多种单端电气接口,能够满足应用需求。

在FPGA内部主要实现以下功能:FLASH存储器控制逻辑,中断控制电路,复位逻辑,看门狗逻辑,离散量控制逻辑。

模块上处理器的IFC接口是一个16位总线,设计中将处理器的局部总线接口通过FPGA转换为外部/内部存储器的地址和控制信号,用于访问FLASH,FPGA内部的控制/状态寄存器等资源。

1.5 电子盘电路设计

电子盘设计指标为存储容量1 TB,其中1 TB为标称值,实际可用容量不小于900 GB;支持SATA 2.0接口协议,接口速率3 Gbps,向下兼容SATA1.0接口协议;电子盘裸盘连续读写速率不小于80 MB/s;电子盘的连接器可插拔次数不小于1 000次。

电子盘设计采用成熟主控芯片+NAND FLASH存储阵列的形式设计实现,主要功能如图4所示。主要包括:SATA控制器电路;掉电保持电路,电源控制电路、毁钥电路;时钟电路;复位电路;SATA接口电路。

图4 电子盘模块功能结构

SATA控制器采用GK8802-GBIV100,是深圳华电通讯有限公司自主研发的固态硬盘控制器芯片,支持SATA3.1接口,最高速率6 Gb/s,并且向前兼容1.5 Gb/s与3 Gb/s;支持1.8 V和3.3 V的Flash IO电压,拥有4个NAND Flash通道,每个通道8个CE,总共支持32个NAND Flash Device;支持DDR3和DDR3L DRAM,支持ECC校验纠错,能力在130 bits/kB,兼容主流厂商的SLC,MCL NAND Flash。支持S.M.A.R.T,支持最多32个NCQ命令。

此控制器支持国科独有的NANDXtraTM纠错技术,最大可提升TLC/3D TLC 3倍擦写寿命 ;支持动静结合的Wear Leveling技术,平衡NAND Flash擦写次数,延长使用寿命;支持增强型垃圾回收机制,有效降低写放大 ;支持国密SM2,SM3,SM4,内置硬件加密算法引擎,内置国际通用SHA256,AES256,内置硬件加密算法引擎。连续读写性能:最高550 MB/s和520 MB/s,随机读写性能:最高90 k和80 k IOPS(@4K) 。

1.6 模块时钟电路设计

CPU模块上配置了66 MHz,125 MHz的单端晶振和100 MHz中的差分晶振。其中,66 MHz时钟经时钟驱动器后一分三,分别作为CPU系统时钟、DDR3时钟和FPGA工作时钟;125 MHz时钟经时钟驱动器后一分二,分别作为两路以太网PHY的参考时钟;100 MHz时钟经时钟驱动器后一分二,分别作为CPU的PCIE时钟和桥芯片的PCIE时钟。时钟配置情况如图5所示。

1.7 复位电路设计

图像处理模块复位关系如图6所示。上电复位:电源5 V电压低于4.65 V时,系统处于复位状态,电压大于4.65 V后,产生大于200 ms复位;模块上电时,为保证FPGA配置过程中其他功能块处于复位状态,设计时把FPGA加载完成信号DONE连接到SM706T的手动复位输入端。当FPGA加载完成后,SM706T再产生200 ms复位信号,模块启动工作。在正常工作中,如果SM706T检测到+5 V电压低于4.65 V时,SM706T产生复位信号,模块处于复位状态;当电压恢复至4.65 V以上时,SM706T产生撤销复位信号,模块重新启动[4]。软件复位,可以通过软件写FPGA寄存器方式复位CPU,复位时间大于2 ms。

2 结语

基于CPU+GPU构架的图像处理模块具有图形处理能力强、工作稳定性高、综合功耗低等特点,非常适合需要图形图像处理工作的嵌入式应用场景。该模块在提供了多用途的图形图像处理能力的基础上,兼顾了性能、体积和功耗的平衡,同时具备较强的内部通信和对外交互联通能力。

图6 复位电路关系