一种新型信号发生器的设计

熊文

关键词:FPGA;MCU;DDS;信号发生器

1引言

信号发生器是一种常用的信号源,广泛应用于信息电子、通信系统和科学实验等领域。它是一种为电子测量和计量工作提供符合严格技术要求电信号的设备。因此,信号发生器和我们熟悉的电量测试仪器(如电压表)一样是最普通、最基本的,也是应用最为广泛的仪器之一,绝大部分电路及其电量的信号源都需要由信号发生器来提供。

直接数字频率合成(Digital Direct FrequencySynthesis,DDS)技术是一种新的数字化技术。它不需要任何的振动,也不需要锁相环,只需要将一系列的数据通过DAC来生成一个预定的模拟信号。由于采用了数字信号的高级处理原理和技术,信号的频率变换速度较快,频率分辨率高,频率稳定度高,输出信号频率和相位可以迅速地进行程序控制,从而能够便捷地进行信号的完全数字调制。本文根据信号发生器的特点及应用情况,以FPGA芯片为主要控制器,结合MCU与高速DAC模块,设计出一款使用简单方便、性能优良的新型信号发生器。

2信号发生器硬件设计

本设计采用FPGA与MCU双核心,外接DAC模块来完成DDS信号发生器的设计实现。以“FPGA+DAC”与滤波器负责完成DDS功能的实现,以“MCU+”屏幕与外围负责完成人机交互的功能。本设计采用“双子板+底板”的设计,子板将MCU与FPGA的所有引脚都引出到底板,以便扩展,同时在底板上引出多个硬件接口,可大大提升该发生器的功能扩展性。

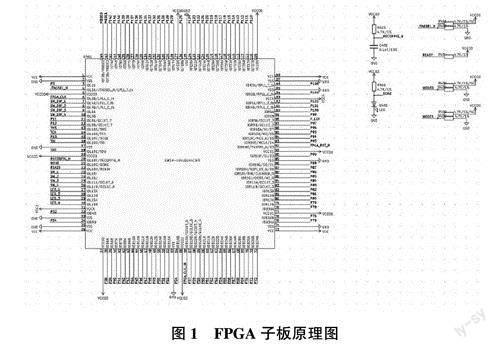

2.1FPGA子板介绍

本设计的FPGA子板采用GWIN-LV4LQ144C615芯片来构建,该芯片是高云GWIN系列产品,其具备相当丰富的逻辑能力,具备各种I/O电平标准,并内嵌了块状静态随机寄存器、数字信号处理模块、锁相环节等新技术。另外,在其内嵌入了Flash技术,是一种具备非易失性的FPGA产品,具有低功率、高稳定性、商品体积较小、封装形式多样、使用方便灵活等优点。

图1是以GWIN为核心的FPGA子板电路图,本设计在该芯片以及其他芯片的电源部分增加了去耦电容、旁路电容以及磁珠来进行抗电磁干扰优化。

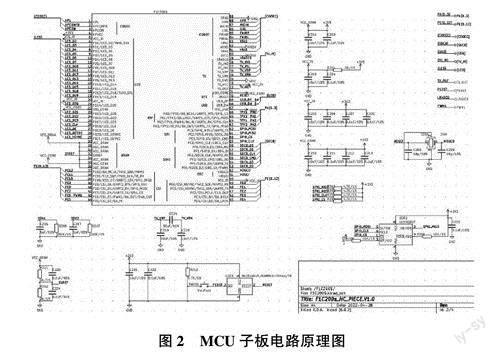

2.2MCU子板介绍

MCU子板采用F1C200S芯片作为内核,主要负责进行交互功能,可接常用的外部设备(如屏幕、Wi-Fi与红外等)。F1C200S内带有高速的通信总线接口,大大提高其运行速度与能力,以及2个外设接口、1个USB接口,还配有常用的摄像头接口、显示屏接口,音频接口等[1]。

因为F1C200S较为方便配置以及具有极为经济的价格,加之其内置的多项资源可以大大简化硬件设计难度,因此其被广泛应用。

F1C200S支持多个系统,在此选用Linux系统进行操作,能有效降低开发难度。图2是以F1C200S为核心的MCU子板电路原理图。

2.3DAC模块介绍

在本设计中,DAC模块选用3peakdac模块进行设计,搭配FPGA即可实现发生器任意波形的产生功能。该模块的特点有:(1) 16管脚直插或邮票孔封装;(2)方便快捷的搭载FPGA最小系统;(3)适用于双通道高速数据采集项目;(4)单通道10位/125Msps高速运行;(5)输出模拟信号2Vpp;(6)3.3~5V稳压供电电源。

2.4电源模块

电源是任何设备必不可少的部分,本系统分别对FPGA和MCU提供了专门的电源模块。

2.4.1FPGA电源模块

本板根据GWIN芯片的自身特性,电源模块为FPGA提供1.2 V的核心电,并提供1.2 V,1.8 V,2.5 V和3.3V四种电压作为Bank电压的可调选项,另为VCCX提供3.3V或2.5V作为可选的辅助电压。本板1.2V的核心电采用SGM2028-ADJ进行供电。SGM2028是一款低功耗、低噪声、低压差、CMOS工艺的线性稳压器,输入电压范围为2.5~5.5V。SGM2028使用静听供电的系统,一个连接在器件BP接口的低外部噪声旁路电容器,能够进一步降低噪声。

2.4.2MCU电源模块

本板采用了EA3036电源模块,这是一颗三通道的Boost DC-DC电源芯片,用来提供1.2 V,2.5 V,3.3V的电平电源。EA3036采用了20引脚的QFN 3×3封装,有效节省了PCB面积。芯片内整合了3个同时降压控制的变换器,可以同时在低负荷和高负载的工作下实现高性能控制。内部的架构也改善了整个电路设计。另外,还有独立的使能控制器,也能任意调整上电时间的顺序[2]。

3信号发生器软件设计

3.1FPGA软件部分

FPGA软件部分主要采用“Gowin+Visual StudioCode”进行编译,采用Verilog语言来进行编写。由Gowin_V1.9.8.03进行项目构建、编译与烧录。由Visual Studio Code来进行Verilog的编写,这基于其极高的扩展性,有着大量的插件来提升它的功能性[3]。

下面介绍主要的Verilog模块。

(l)PLL.v:这一步是为了使GWIN内置的PLL模块代码上调,用Gowin内置的IP核形成一个PLL.v文件。

(2) ROM.v:此模块是在FPGA内部形成一块ROM并存人正弦波的波形,以供查找表使用。

(3) Divide.v:采用if來进行分频,并通过输入不同的值来控制输出频率,以达到DDS频率控制。

(4) SPI.v:调用IP核,实现SPI功能,完成与MCU的交互功能。

3.2MCU软件部分

3.2.1BootLoader启动程序

PC在启动时,首先进入BIOS,再根据BIOS中配置信息引导后续的启动操作系统,如Windows启动。而对于嵌入式Linux启动,则没有BIOS,而是用BootLoader来进行程序的引导。在嵌入式操作系统中,BootLoader是在操作系统内核运行之前运行。可以初始化硬件设备、建立内存空间映射图,从而将系统的软硬件环境带入一个合适状态,以为最终调用操作系统内核准备好适合的环境[4]。

BootLoader启动过程可分为stagel,stage2两个阶段,其中stagel完成初始化硬件,如CPU的寄存器、内存的控制器,来为stage2的运行准备内存空间。

当Arm开发板上电以后,第一个要加载到内存并运行的程序就是BootLoader.本设计选择了U-boot作为引导程序[5]。

3.2.2Linux启动程序

FIC200S的核心licheepi nano已经完成了Linux官方源码的移植。所以可以直接采用licheepi nano文件进行使用,并烧录到TF卡中,从而使设备进行Linux的启动[6]。

3.2.3界面显示程序

本设计采用LittlevGL进行界面显示。

LittlevGL是一款功能强大的用户界面显示软件,调用简单方便。LittlevGL自带大量的控件,如工具、视窗、按钮、标志、list、图形等,还能够自定义控件。LittlevGL还支持众多特效,如透明、阴影、手动展示隐藏的滑动条、页面转换动画、图标开启结束动画、光滑的拖拽控制、分层屏幕、反锯齿效果、只耗少许内存的字体等[7]。

4系统调试及结果分析

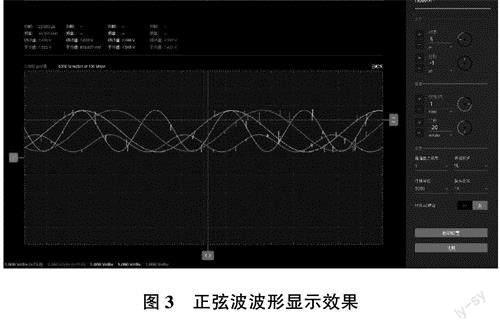

本设计采用了ADALM2000中的示波器功能来对信号器产生的波形进行显示与调节。图3显示了由该示波器所采集的正弦波波形信号,为改变频率与电压后的多次显示效果。

由图3可知,本设计实现了不同频率、幅值下的正弦波形的显示,波形失真率较低,达到了预期效果。此外,其他几种常见波形(如矩形波、三角波等)都可以得到很好的显示效果。

5结束语

本文介绍了一种基于DDS技术信号发生器的组成原理与功能,并重点介绍了该信号发生器的硬件组成部分及软件实现部分,最后对信号波形结果进行显示与调节。该信号发生器功能齐全、操作方便、扩展性强,具有一定的使用价值。