基于海思平台的分布式图像拼接系统可视化控制研究

刘朝伟

摘要:模块化调用海思Hi3559A系统,能够快速实现分布式图像拼接系统的控制可视化预览,控制所见即大屏所得,使得播放切换更加稳定可靠。文章提出以输入模式作为分析点,进行流程梳理和资源调用配置,这种系统在低带宽环境下为快速搭建可视化控制系统提供了一种解决路径。

关键词:分布式图像拼接系统;可视化控制;子码流;海思平台

中图分类号:TP317.4 文献标志码:A

0 引言

分布式图形处理系统中,分布式输入节点和分布式输出节点通过交换机互联,系统天然具备可视化控制基因,可视化控制也是所见即所得放心操作的基础。在输出可预知性大大提高的同时,可视化操作是相对传统中控模块无反馈操作的颠覆性创举。如何在不增加系统负载的情况下,做到良好的可视化控制,是分布式拼接系统中期需要在易用性上考虑和解决的问题。海思芯片族中具备主码流和子码流功能的集合均能在逻辑上实现系统的可视化控制。

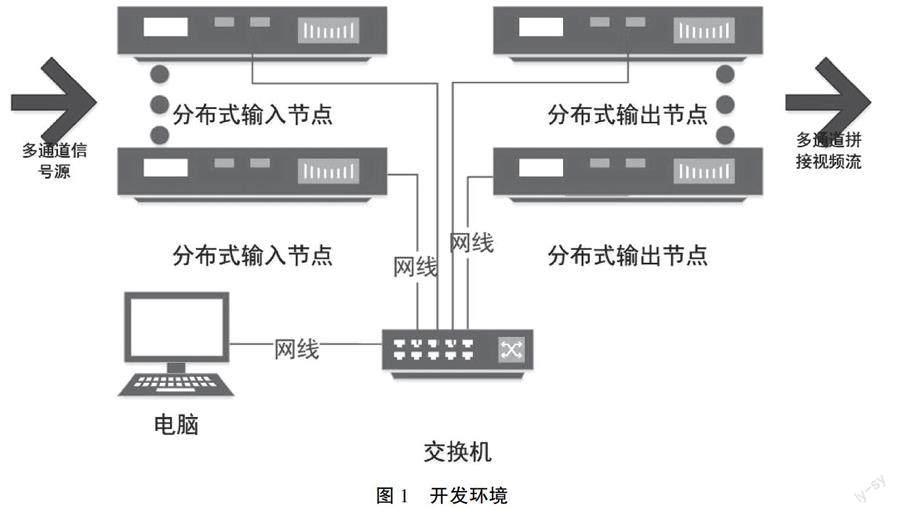

1 开发环境简介

基于海思芯片的子码流可视化控制既能节约开发和运营成本,也能最大化在简化系统上实现多种功能定位。开发环境是在初步成型的分布式网络控制环境下实现的。如图1所示为开发环境已初步成形的分布式系统,输入信号源可以兼容多种数字和模拟信号,分布式输入节点统一编码为标准格式后,通过分布式输出节点输出到电视墙或LED大屏,电脑上位机软件可以通过数据包获取控制信号。多通道信号源可以是网络摄像头,也可以是标准视频接口设备。在分布式网络中,作为控制节点的电脑,如果没有可视化输入输出界面,状态可靠性大大降低,操作随机性变得不可控制。

2 开发可行性

分布式输入节点和分布式输出节点均搭载了智能海思芯片,内置CPU调度核和VPSS处理核。处理核支持主码流1 080 P@60 Hz或者4 K@60 Hz输出(向下兼容),子码流可以控制在一定的分辨率带宽以内,稍加利用,可以实现不增加系统负载的情况下,提高系统利用率,增强系统可用性。

3 硬件构架平台

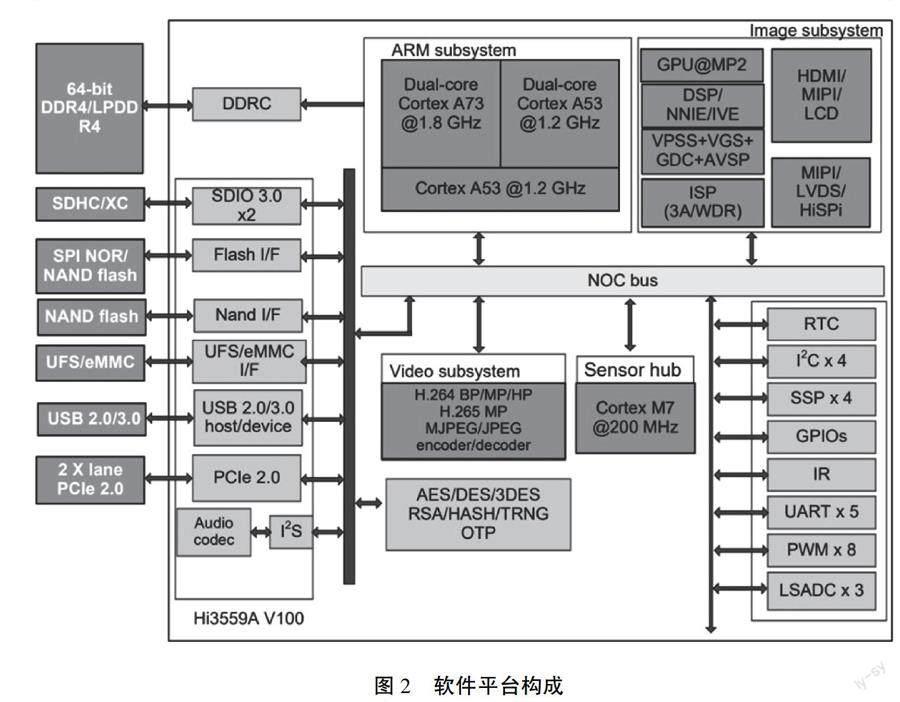

Hi3559A支持多路1 080 P视频输入,内置拼接硬件,仅需要开发调度模式选择的应用程序,同硬件交互,实现布局、处理和参数设置进行拼接和控制[1]。

如图2所示为Hi3559A提供的媒体处理软件平台MPP(Media Process Platform),可支持应用软件快速开发,提供双码流输入输出。标准视频格式在图像输入输出端口的图像子系统(IMAGE SUBSYSTEM),该图像子系统还兼顾了图像处理功能(VPSS);码流视频数据包在网络编解码端口的视频子系统(VIDEO SUBSYSTEM)的编码模块(ENCODER)和解码模块(DECODER)中。

海思媒体处理平台的主要内部处理流程如图2所示,主要用到的模块功能描述如下。

VI:捕获视频图像,可做剪切、去噪等处理,并输出多路不同分辨率的图像数据。

VO:捕获标准码流视频,可做组合、缩放等,并输出1路不同分辨率的标准视频图像。

VPSS:接收其他模块发送的图像数据,可对图像进行图像增强、锐化等处理,并同源输出多路不同分辨率的图像数据。

VENC:编码模块负责接收其他模块处理输出的数据,可叠加通过Region模块设置的OSD图像,然后输出不同协议编码的码流数据(可做视频OSD叠加),主要用于输入节点以及可视化预览。

VDEC:解码模块负责接收网络中的模块处理输出的标准数据,可叠加通过Region模块设置的OSD图像,然后輸出标准协议编码的码流数据(可做视频OSD叠加),主要用于输出节点。

实际中,设计底层硬件比如VDEC,VENC,VPSS都只能操作VB(Video Buffer)内存[2]。

4 拼接预览方案实现

在视频子系统模块(VIDEO SUBSYSTEM)中主码流通过硬件解码输出,子码流通过网络数据包回传上位机,上位机软件解码即可显示输入输出的节点,将输入节点画面直接显示,将输出节点画面根据主码流各信号源跟随的方式布局画面来组合显示。下面以VI模式的PIPE为例,子码流数据的获取具体经历了如下几个步骤。

4.1 VI模式

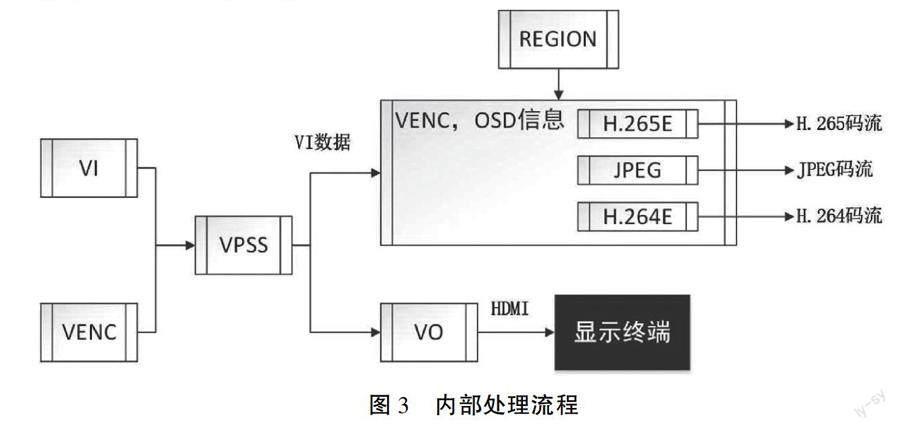

如图3所示,VO模式是主码流拼接输出,本文暂时不予考虑;VI模式可定义画质和带宽,VI模式划分了4个部分:DEV->PIPE->PHY_CHN->EXT_CHN。

输入设备DEV负责对数字化图像数据时序进行解析。PIPE绑定在DEV后方,包含了ISP的相关处理功能,主要是对图像数据进行流水线处理,输出YUV图像个通道[3]。PIPE主要从DEV接收数字化格式的图像数据,执行图像处理ISP,执行完ISP后输出YUV图像。

PHY_CHN所得到的图像就是1 920×1 080像素格式,并且不可以把该通道的数据再作为其他扩展通道的源来进行图像的放大或缩小处理,该码流即为方便VO调用的标准码流。

可以通过EXT_CHN将获取的图像任意指定为合法的像素大小,通过指定像素格式及宽高大小,进行预处理后可以作为视频编码模块(VENC)的输入。同时,把该通道作为后面所要建立的扩展通道的源,通过设置所要建立的扩展通道的属性(主要指绑定的源通道号、图像帧率、图像宽高等,见VPSS_EXT_CHN_ATTR_S结构体),再经由各扩展通道获取所需的目标分辨率,此通道码流即为控制预览所需的子码流,是本文讨论的重点。

4.2 VENC模块数据格式

VENC模块的输入源包括3类。

(1)区域管理(REGION)读取图像文件和配置文件向编码模块发送数据。

(2)视频输入(VI)模块采集的图像经视频处理子系统(VPSS)发送到编码模块。

(3)视频输入(VI)模块采集的图像直接发送到编码模块。

本方案为了快速响应主显示格式的匹配,实际采用了H.264编码,它有4种画质逐级提高的级别,分别是BP,EP,MP,HP。

4.3 码率控制

码率控制是可视化控制的最关键环节。码率就是数据传输时单位时间传送的数据位数,一般用的单位是kbps即千位每秒[4]。

以H.264 编码为例,图像的质量越好,码率越高;图像质量越差,码率越低。码率控制是针对连续的编码码流而言,而JPEG协议编码通道不包括码率控制功能。

编码流程包括了输入图像的接收、图像内容的遮挡和覆盖、图像的编码以及码流的输出等过程。

VENC模块由编码通道子模块(VENC)和编码协议子模块(H.264/H.265/JPEG/MJPEG)组成。通道支持接收YUV格式图像输入,支持格式为YUV 4∶2∶0或YUV 4∶2∶2,其中H.264/H.265只支持YUV 4∶2∶0,JPEG/MJPEG支持YUV 4∶2∶0或YUV 4∶2∶2。通道模块接收外部原始图像数据,而不关心图像数据是来自哪个外部模块。

通道接收到图像之后,比较图像尺寸和编码通道尺寸:

如果输入图像比编码通道尺寸大,VENC将按照编码通道尺寸大小,调用VGS对源图像进行缩小,然后对缩小之后的图像进行编码。

如果输入图像比编码通道尺寸小,VENC丢弃源图像。VENC不支持放大输入图像编码。

如果输入图像与编码通道尺寸相当,VENC直接接收源图像,进行编码。

REGION模块支持对图像内容的遮挡和叠加。

完成视频区域管理之后,图像被送入具体协议类型编码通道,完成视频编码,输出码流。

4.4 VB读取

VB(Video Buffer)在海思媒体处理中也是一个重要的概念,VB本质上就是一个物理地址连续的内存块,只不过在MPP层里提供了一系列初始化、申请、释放操作的接口。

公共缓冲池是在系统初始化中分配的,具体分配的接口就是HI_MPI_VB_SetConf()和HI_MPI_VB_Init()。可以通过这两个接口按照所需VB数量和VB大小建立不同的缓冲池。

公共缓存池中的VB使用者是VI/VPSS/VENC/VDA/VO,所有的视频输入通道都可以从公共视频缓存池中获取视频缓存块用于保存输入或输出的图像的主码流。

除了通过HI_MPI_VB_Init建立的公共视频缓存池,调用接口HI_MPI_VB_CreatePool创建一个视频缓存VB池作为子码流缓冲池。然后配合某模块通道的xxx_attachPool(VPSS,VENC,VDEC有该接口)绑定到某个通道上,那么就只有该通道可以使用,比如HI_MPI_VENC_AttachVbPool被VENC的0通道绑定之后,就只有VENC_CHN_0可以使用该VB获取子码流。

5 结语

经过上述方案的设计,使用交叉编译器将D1(704×576@25 Hz)的可视化视频流引导至动态库形式嵌入上位机软件平台上,供应用界面调用。在对其他系统模块也进行相应调整后,需要预览的拼接码流可以在客户端界面显示出来。

在分布式拼接器上位机接入多个子码流后,可以在客户端进行1画面、2画面、3画面、4画面等预览与同步显示输出画面缩略图显示,50通道的输入画面也能每通道独立显示。

通过调出交换机Console接口数据,在百兆网卡使用条件下,子码流的网络使用率为43%;在未使用子码流情况下,在高频切换控制操作的极端情况下,仅控制码流的网络使用率为8%。可以明显看出,使用拼接码流降低带宽环境下可在低带宽条件下实现输入和输出的可视化多画面实时预览与操控。

在低带宽环境下,此拼接预览方案对于保证客户主码流输出的大屏或视频墙显示之外,可以远程或无线客户端多画面预览的實时操控是有效的,具备实用价值。

参考文献

[1]刘浩,何岩.基于海思平台的N V R拼接预览方案的设计与实现[J].电子设计工程,2015(10):39-42.

[2]蔡熙.基于海思处理器的分布式数据采集系统桥接子系统硬件研发[D].杭州:浙江大学,2021.

[3]滕伟,安博文.基于FPGA+DSP技术的Bayer格式图像预处理[J].电子设计工程,2010(10):145-147,151.

[4]余先庆,刘根成.浅析大型数据采集系统的设计[J].微电子学与计算机,1997(5):19-20.

(编辑 沈 强)

Research on visual control of a distributed image splicing system based on Hisi platform

Liu Chaowei

(Shanghai Sansi Electronic Engineering Co., Ltd., Shanghai 201199, China)

Abstract: Modular call to Hisi Hi3559A system can quickly realize the control visual preview of the distributed image splicing system, control what you see is the large screen, and make the playback switch more stable and reliable. This study proposes to take the input mode as the analysis point for process combing and resource call configuration, and this system provides a solution path for quickly building a visual control system in a low-bandwidth environment.

Key words: distributed image splicing system; visual control; subcode flow; Hisi platform