一种可级联的多通道实时阵列信号处理系统设计

冯 武,罗 欣,孙卫杰

(中国电子科技集团公司第二十七研究所,河南郑州 450015)

0 引 言

近几年,DBF(Digital Beam Forming)体制的雷达[1-3]已经广泛应用于各个领域,同时多波束覆盖的优势使其发展前景良好。但是传统的DBF 体制雷达的架构都比较复杂,为了处理大批量回波信号,通常采用单独的机箱完成ADC(Analog-to-Digital Converter)采样、数字波束形成和信号处理等功能。这种架构虽然具有类似平台快速移植的优势,但是不适用于差别较大的平台,特别是要求集成度比较高的应用环境,而且其对应的成本比较高,调试难度也较大。

文献[4]自主研发的软件化雷达信号处理软件“RadarLab 2.0”,采用图形化界面将不同的雷达数字信号处理(Digital Signal Processor, DSP)算法和FPGA(Field Programmable Gate Array)程序进行模块化处理,并最终适配到各类标准的6U 的VPX 板卡以及VPX 机箱,实现了“软件化雷达信号处理”[5-6]思想。文献[7]自主研发的“数字单元”作为二维DBF 雷达的核心处理单元,以标准的6U 的VPX 板卡以及VPX 机箱[8],实现了48 路中频信号ADC 采样、16 个DBF 波束形成、脉冲压缩、动目标检测(Moving Targets Detection, MTD)等处理。中国电子科技集团公司第二十七研究所研制的反蜂群雷达[9-11],采用的是5 个插槽的6U 的VPX 机箱进行48 路数字波束形成[12-13]和相应的信号处理,模拟前端和后端数字处理机箱,采用光纤[14]进行数据交互。

随着雷达集成度的要求越来越高,传统的分体式架构(天线/收发组件(Transmitter and Receiver, TR)/接收机作为雷达前端,VPX 信号处理机箱[5]作为雷达后端)已经很难满足功能要求。因此,急需提出一种高度融合的设计方法。

针对集成度要求比较高的DBF 雷达需求,本文提出一种24 路阵列信号处理板,可以集中处理24 路中频信号采集、下变频、高速互传、数字波束形成、波束控制、信号处理以及高速存储,并可通过级联该阵列信号处理板实现更大规模的DBF 雷达系统设计。

1 阵列信号处理板设计

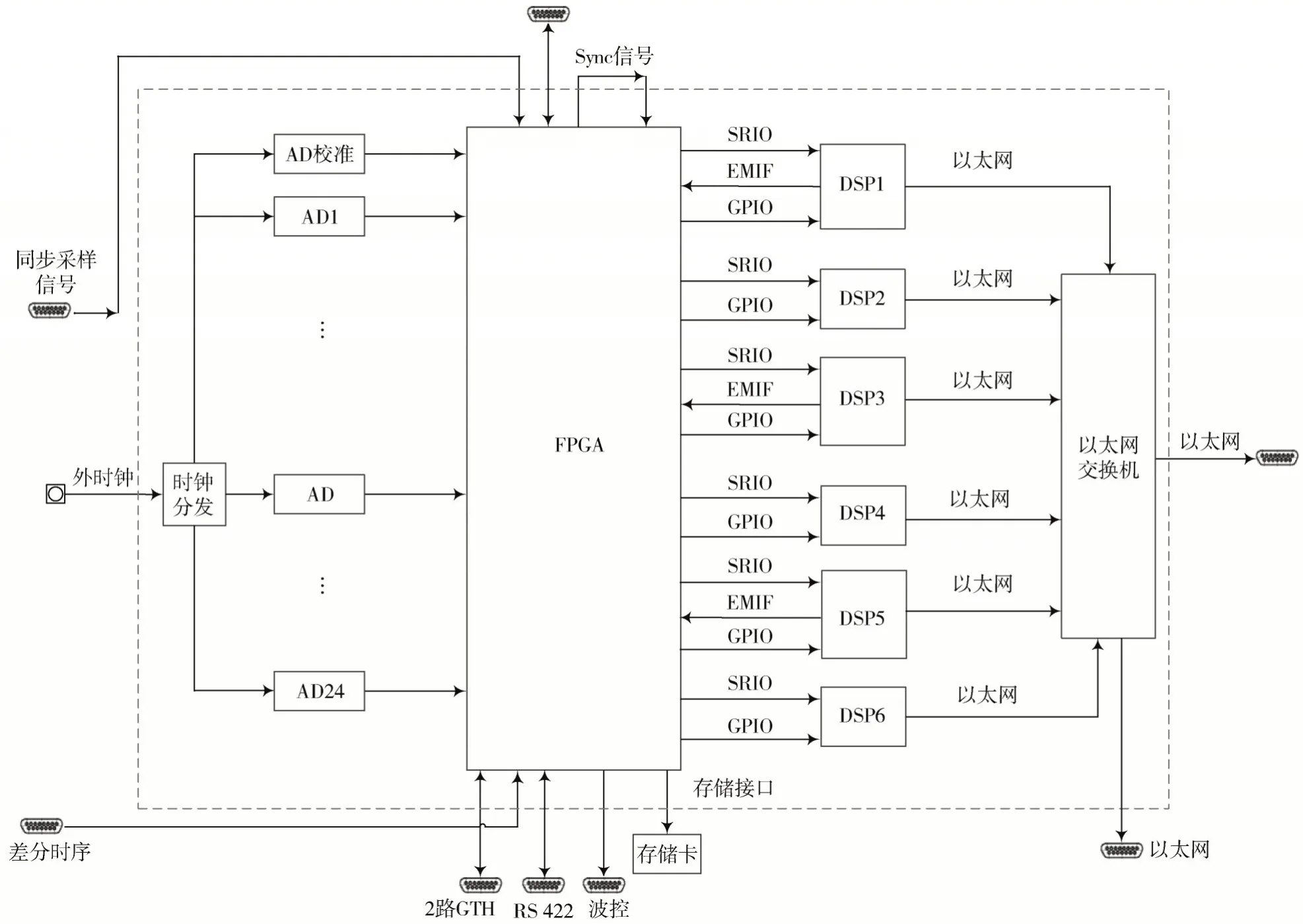

阵列信号处理板由1 片FPGA、6 片DSP、6 片AD 以及以太网交换机等芯片组成,如图1 所示。

图1 阵列信号处理板的组成框图

由图1 可以看出,6 片AD 芯片对24 路雷达中频信号进行AD 同步采样,然后同步传输到FPGA 芯片进行DDC 下变频处理以及多路数字波束形成,形成后的波束数据通过6 路串行高速总线(Serial RapidIO, SRIO)接口分别传输到6 片DSP 芯片进行脉冲压缩、动目标检测以及恒虚警等处理。最后,阵列信号处理板检测出的目标信息以及上位机下发的波形模式、频率号、波位号、检测门限等参数都是通过板载的以太网交换机进行交互。

此外,阵列信号处理板上的FPGA 通过XMC 接口的GTH(Gigabit Transceiver)总线可以与存储子卡的主控zynq 芯片进行互联,实现所需的各类数据以文件系统进行高速存储,并可以通过千兆网口进行数据回读。

该阵列信号处理板之间采用分立式高速线缆连接相应的GTH 接口,使用稳相电缆实现时钟和回波信号互联,采用同步I/O 接口实现系统的同步设计;考虑到系统的接收通道之间和发射通道之间的相位差,还需要进行系统校准设计,其中6 片AD 芯片完成接收校准的24 路信号同步采集,单路1 路AD 芯片完成发射校准的分时信号采集。

1.1 阵列信号处理板外观

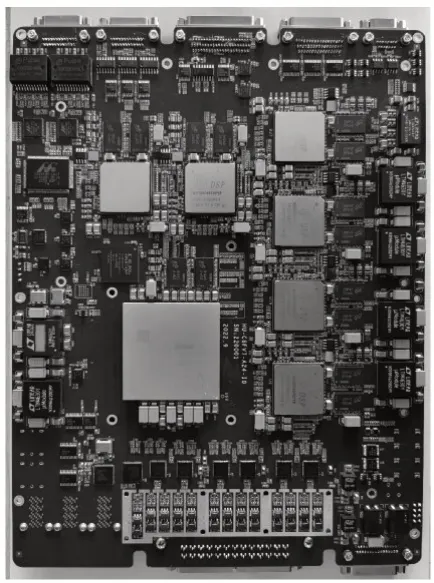

阵列信号处理板正面如图2 所示。

图2 阵列信号处理板正面

由图2 可知,FPGA 和6 片DSP 以及电源等主芯片都位于电路板的正面。

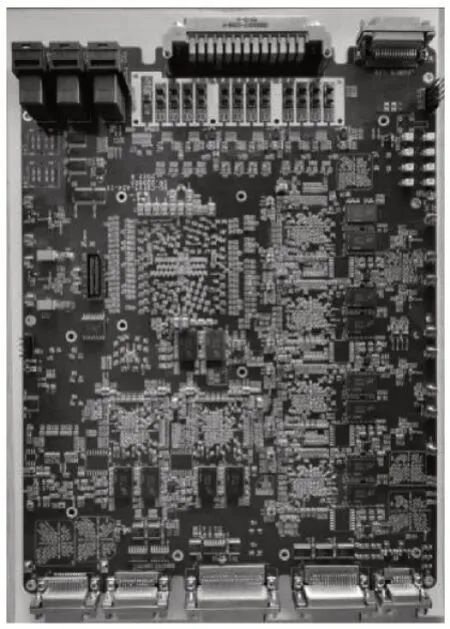

阵列信号处理板背面如图3 所示。

图3 阵列信号处理板背面

由图3 可知,电阻、电容、连接器等都位于电路板的背面。

阵列信号处理板腔体如图4 所示。

图4 阵列信号处理板腔体

由图4 可知,外部散热腔体与电路板的正面通过导热垫片进行散热处理。

1.2 AD 设计

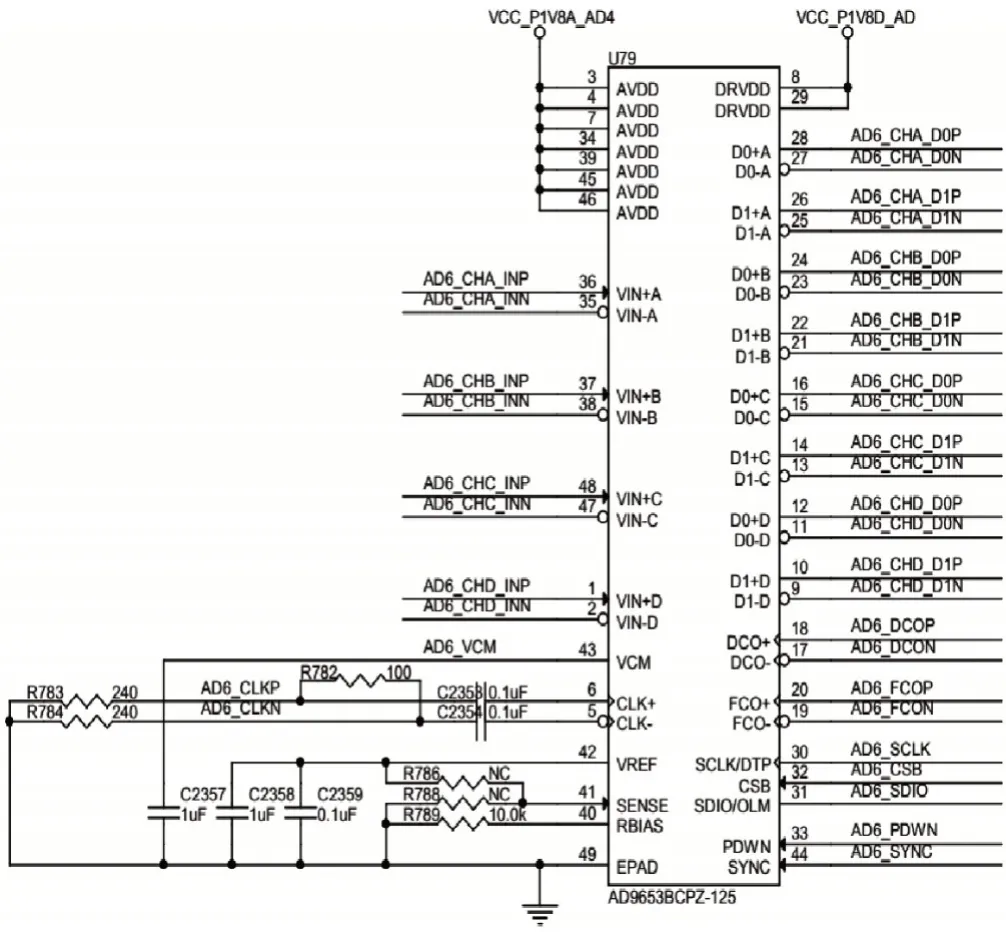

阵列信号处理板的AD部分主要由6片AD9650和1 片AD9653组成。其中,6片AD9650完成24路中频信号的采样,采样率最高为125 MHz,采样位数16 位;1 片AD9653完成发射校准的信号采样,采样率最高为105 MHz,采样位数为16 位。ADC 部分设计如图5 和图6 所示。

图5 AD9650 设计原理图

图6 AD9653 设计原理图

1.3 FPGA 设计

FPGA 采用一片Xilinx 公司的XC7V690T,实现了多路AD 接口、2 路GTH 接口、多路RS 422/485、同步I/O、波控接口(即控制TR 组件的I/O 接口)以及与DSP 通信的多路通用型输入输出(General-Purpose Input/Output,GPIO)/3 路外部内存接口(External Memory Interface,EMIF)/6 路SRIO 等接口。能够完成DDC 下变频/波束控制/DBF 数字波束形成等功能。

FPGA 部分设计如图7 所示。

1.4 DSP 设计

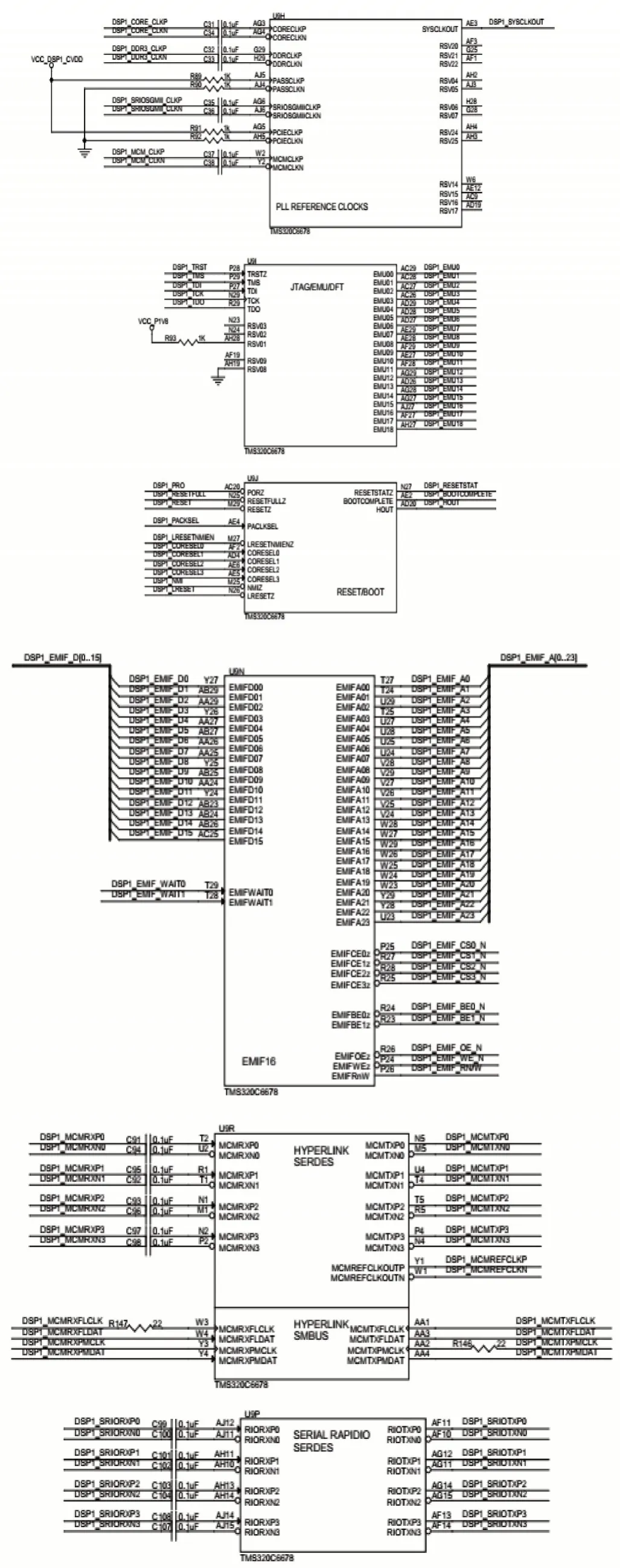

DSP 采用6 片TI 公司的TMS320C6678,是一款八核C66X 的定点/浮点DSP,支持高性能信号处理应用,每核心主频1.0 GHz/1.25 GHz,单核可高达40 GMACS 和20 GFLOPS。支持PCIe、SRIO、Hyperlink、EMIF16、以太网等多种高速接口,同时支持I2C、GPIO、SPI、异步串行通信口(Universal Asynchronous Receiver/Transmitter,UART)等常见接口,能够实现脉冲压缩、动目标检测、恒虚警等信号处理功能。

DSP 部分设计如图8 所示。

图8 DSP 设计原理图

1.5 以太网交换机设计

以太网交换机采用88E6185,实现本板的9 路以太网接口的交换功能,具体设计图如图9 所示。

图9 以太网交换机原理图

2 板间同步实现

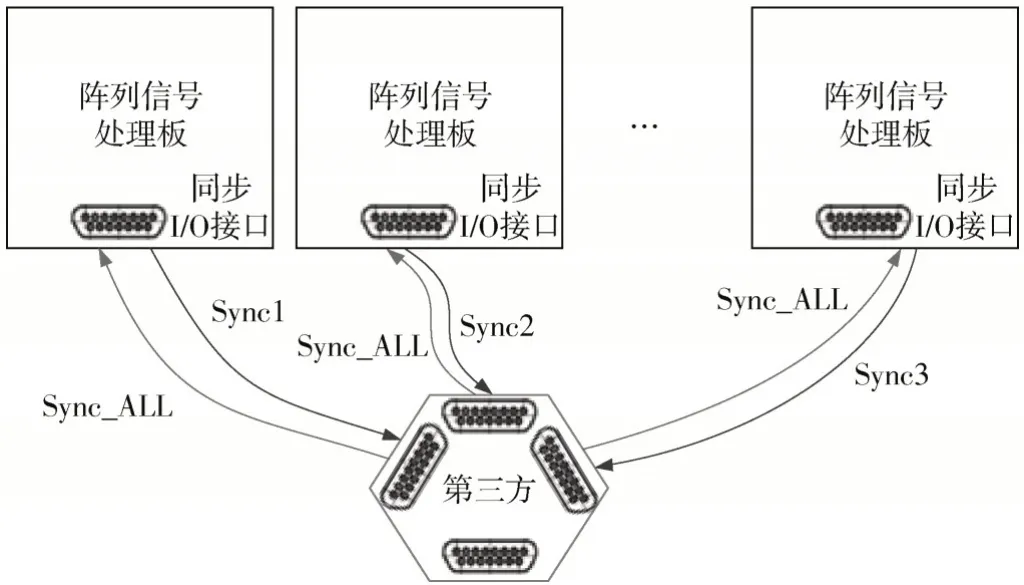

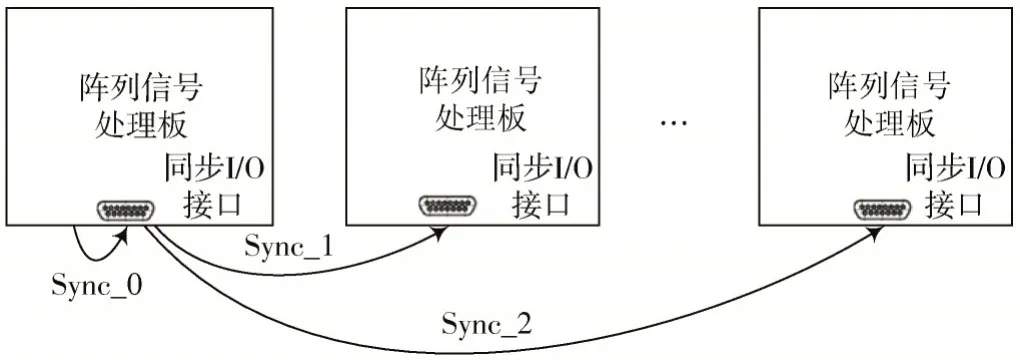

阵列信号处理板的板间同步设计主要由阵列信号处理板之间的同步I/O 接口来实现。实现方式有两种:

1)第三方输出的同步I/O 信号到达所有的阵列信号处理板的长度保持一致。

2)阵列信号处理板输出两路同步I/O 线缆,其中一路返回自身,另外一路连接到其他阵列信号处理板,这两部分线缆长度保持一致。两种实现方式示意图分别如图10 和图11 所示。

图10 系统同步采样示意图1

图11 系统同步采样示意图2

由图11 可以看出,由第一块阵列信号处理板发出同步信号sync_0、sync_1、sync_2 等,分别连接到自身电路板、第二块板、第三块板等。其中,需要注意的是,sync_0、sync_1、sync_2 的线缆长度需要保持一致,而且在电路板上的布线长度也需要保持一致。

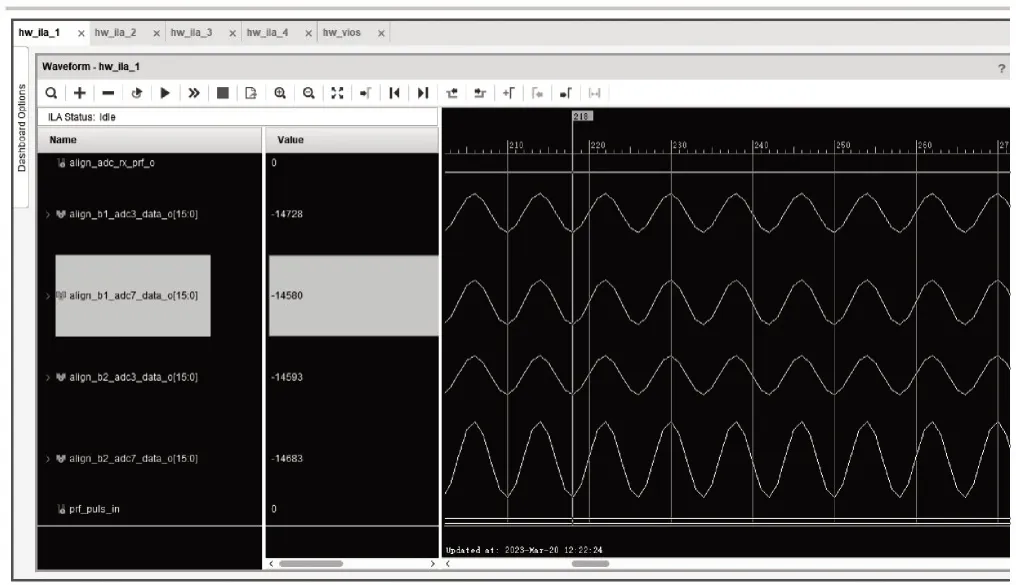

同步采样后的两个电路板AD 数据需要通过高速GTH 接口完成数据交互,以便进行后续的数字波束形成。此时,交互的数据需要进行对齐操作,使同一时刻采集数据位于采样窗的同一位置。利用周期的pri 信号和FPGA 的FIFO 实现周期性的对齐检测,对齐前和对齐后的AD 数据如图12 和图13 所示。

图12 对齐前的AD 数据

图13 对齐后的AD 数据

从图12 可以看出,主板的通道间AD 数据已经对齐,从板的通道间AD 数据也已经对齐,但是主板和从板之间通道的AD 数据之间有相位偏差。因此需要对主板和从板之间的数据进行对齐操作。

从图13 可以看出,主板和从板之间的数据经过对齐操作,全部通道之间已经没有数据错位。

3 收发校准实现

在一维DBF 雷达平台上,实现整个雷达系统的接收校准和发射校准。

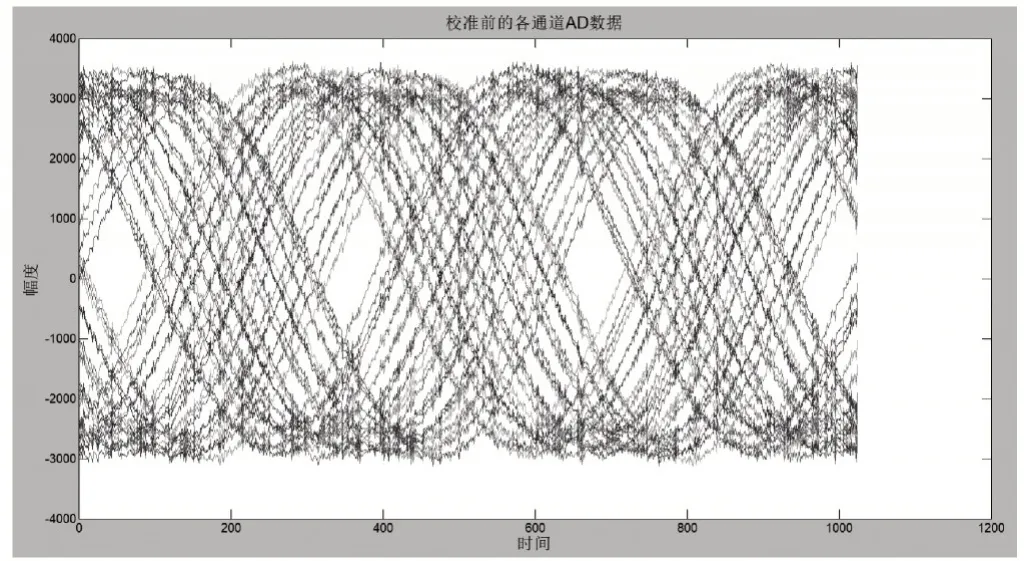

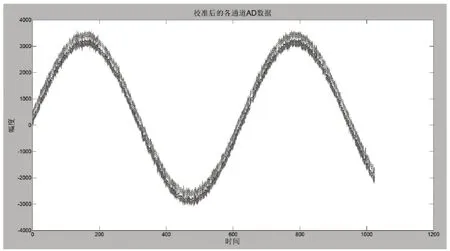

3.1 接收校准

频综发出相对基频偏移0.5 MHz 的校准信号,经过校准分发网络到达各TR 组件以及接收机,阵列信号处理板同步采集所有接收通道数据,然后计算各个通道的初始相位,并上传到上位机;上位机计算相应的校准系数,并下发到各个对应的通道进行校准;最后重新采集所有通道的ADC 数据,上传到上位机,判断是否得到有效校准。接收校准之前的原始数据和接收校准之后的数据如图14 和图15 所示。

图14 48 通道接收校准之前的原始数据

图15 48 通道接收校准之后的数据

在图14 和图15 中,纵坐标为采样信号的幅度,横坐标为采样时间轴,可以形象表示被采样信号的相位。对比图14 和图15,48 通道之间的初始接收相位差得到了有效的校准。

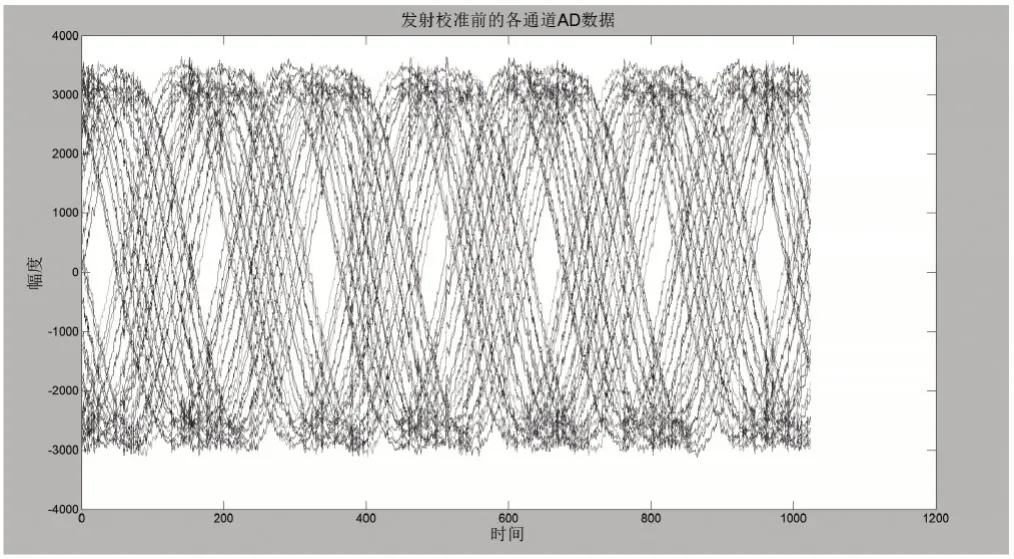

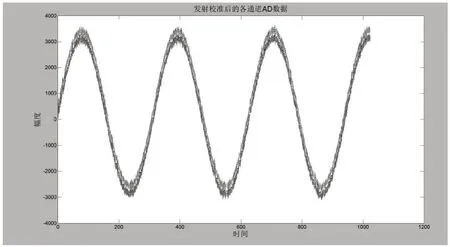

3.2 发射校准

频综发出相对基频偏移1 MHz 的校准信号。首先利用波控程序依次打开48 个TR 组件的发射通道,并通过单独的AD 芯片进行数据采集;然后计算出各个发射通道的相位;最后由上位机下发各个通道的校准系数来实现整个系统的发射校准。发射校准前和发射校准后的数据如图16 和图17 所示。

图16 48 通道发射校准之前的原始数据

图17 48 通道发射校准之后的数据

由图16 和图17 对比可知,48 通道之间的初始发射相位差得到了有效的校准。

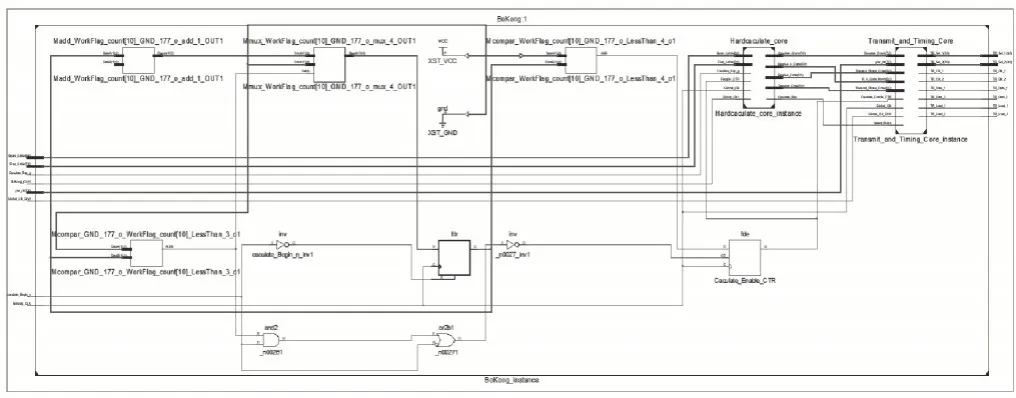

4 波束控制设计

波束控制设计主要实现雷达波束的指向控制,通过对频率和波位等指令的解算,将相应的配相码、衰减码、收发开关等参数下发到其对应的收发组件中,由FPGA芯片具体实现,其算法组成框图如图18 所示。

图18 波控算法组成框图

从图18 可以看出,波束控制主要包含两部分:配相计算单元和配相分发单元。其中:配相计算单元利用FPGA 硬件并行运行的特性完成对频率和波位的迭代配相算法,计算出相应通道的配相码;配相分发单元当接收到配相发送命令后,向收发组件发送满足通信协议的串行数据流,主要包含收发开关、发送/接收配相码、衰减码等信息。

5 级联设计

经过系统校准之后的数据经由该阵列信号处理板实现多种子阵规模的数字波束形成。下面以2 块和5 块电路板为例,即2 块电路板实现48 通道的数字波束形成,5 块电路板实现120 通道的数字波束形成。

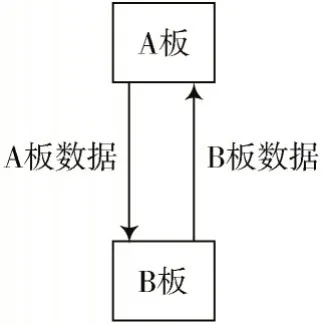

5.1 2 块电路板级联

以A/B 板表示2 块阵列信号处理板,可以实现48 个数字波束,其实际连接图、级联示意图和流程图分别如图19~图21 所示。

图19 2 块阵列信号处理板的实物级联图

图20 2 块电路板级联示意图

图21 2 块电路板形成48 个数字波束流程图

由图21 可以看出,通过级联2 块阵列信号处理板实现总共48 个数字波束。首先,A、B 阵分别将各自的AD数据通过GTH 高速接口传输到对方,使A 阵和B 阵都具备满阵数据;然后,A 板使用满阵数据和波束权重计算出前24 个数字波束,同时,B 板计算出后24 个数字波束。

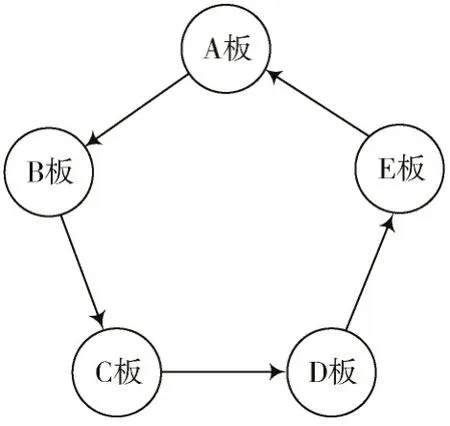

5.2 5 块电路板级联

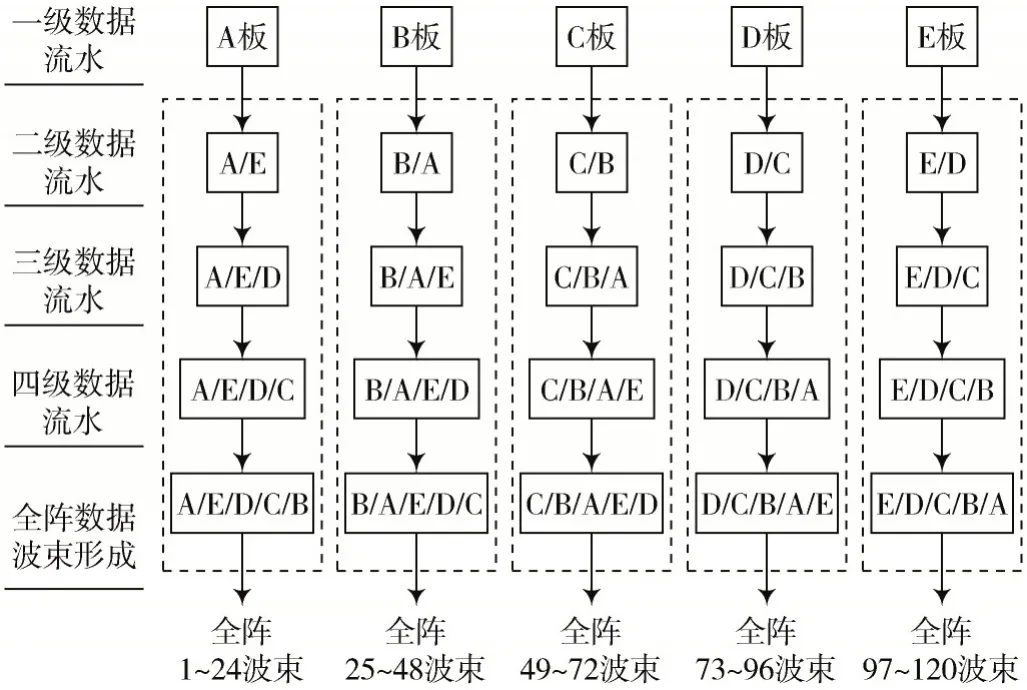

以5 块阵列信号处理板形成120 路数字波束为例,级联示意图和流程图分别如图22、图23 所示。

图22 5 块电路板级联示意图

图23 5 块电路板级联形成120 个数字波束流程图

从图22 中可以看出:A/B/C/D/E 共5 块电路板通过GTH 接口进行级联,每个电路板都有2 个GTH 接口,分别与另外两块电路板互联,最终,所有的电路板通过GTH 接口形成环形架构进行数据传输。

从图23 中可以看出:A/B/C/D/E 共5 块电路板都要经过四级数据流水获取全阵的基带数据,然后进行数字波束形成。以A 板为例,经过第一级数据流水,获得了E 板通过GTH 接口传输过来的E 板数据,此时A 板具备了本地的A 板数据和外来的E 板数据,即A/E 数据,同时,E 板接收到D 板数据,即E 板具备E/D 数据;经过第二级数据流水,A 板接收E 板传输过来的D 板数据,此时,A 板具备了A/E/D 数据;同理,经过第三级数据流水,A 板具备了A/E/D/C 数据,经过第四级数据流水,A 板具备了A/E/D/C/B 全阵数据。然后,A 板将全阵数据与其对应的权重系数进行复乘相加,形成1~24 个数字波束。同理,B/C/D/E 板形成25~120 个数字波束。

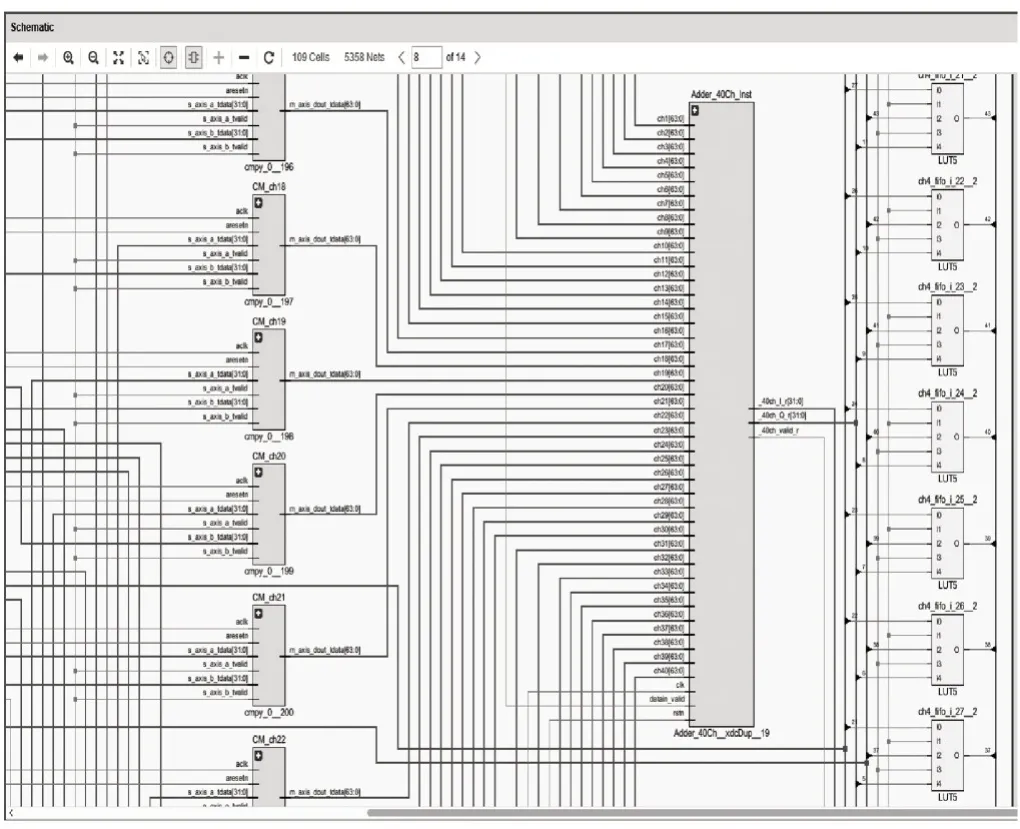

6 数字波束形成设计

每个电路板接收静态或者自适应的波束权重系数,然后将收到的全阵数据与权重系数进行复乘,最后进行加法处理形成数字波束,其算法的FPGA 架构如图24所示。

图24 数字波束形成的算法架构图

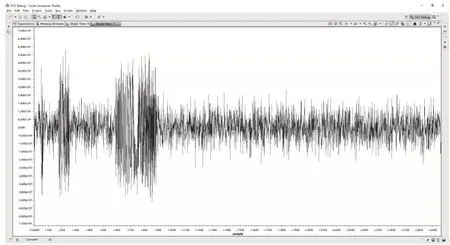

每个电路板形成后的24 个波束通过6 个SRIO 接口分别传输到本板的6 个DSP 中,在DSP 的开发环境CCS中可以观察接收到的波束数据,也可以将波束数据上传到计算机进行显示。其中,以模拟产生的三段线性调频信号为例,经过功分网络和接收机后,传输到所有的AD通道,经过采样、下变频和DBF 之后,从CCS 中观察到的第一路数字波束如图25 所示。

图25 数字波束形成的回波图

此外,阵列信号处理板还可以实现脉冲压缩、动目标检测以及恒虚警检测等功能,并将目标参数通过以太网上传到上位机进行点迹或者航迹显示。

7 结 语

本系统适用于集成度比较高的DBF 体制雷达设计,通过快速移植程序算法实现前期系统仿真验证,各类标准化接口、成熟的同步设计、校准设计和级联设计降低了系统的前期联调难度,缩短了整个系统的研制周期,并提高了系统的可靠性和通用性。

注:本文通讯作者为冯武。