基于FPGA的简易计算器的设计与实现

李强 房雅文 黄蕾 李雪 王世龙 陈初侠

关键词:简易计算器;FPGA;Verilog HDL;Quartus II

中图分类号:TP29 文献标识码:A

文章编号:1009-3044(2024)03-0046-04

0 引言

计算器作为一种简单而实用的计算工具,在日常生活中被广泛使用,如今市场上的计算器种类丰富且功能多样,但功能过多的计算器价格昂贵且大多数功能可能还用不上,所以设计一款简单而实用的计算器具有较好的现实意义[1]。本文基于Quartus II 13.1软件和Verilog HDL语言设计了一款简易计算器,主控芯片采用Altera公司Cyclone Ⅳ E系列的FPGA芯片EP4CE6E22C8[2]。所设计的简易计算器具有加减乘除四则运算功能,输入的两个操作数采用拨码开关来实现,输出结果用数码管进行显示。

1 简易计算器设计要求

简易计算器设计要求如下:

1) 能实现操作数0至15的加减乘除四则运算。

2) 具有复位功能,当复位时运算结果为0。

3) 输入数据用四位二进制表示,通过8个拨码开关来实现。

4) 输入数据和计算结果采用8个共阳极八段数码管显示。

5) 四则运算的选择通过4个独立按键来实现。

6) 具有LED点亮功能,当选择不同的运算时会有与之对应的LED灯被点亮。

7) 减法运算时,若被减数小于减数,运算结果能显示负号“-”。

8) 除法运算时,运算结果要保留一位小数,当除数为零时,显示的运算结果为“EE.E”。

2 简易计算器设计方案

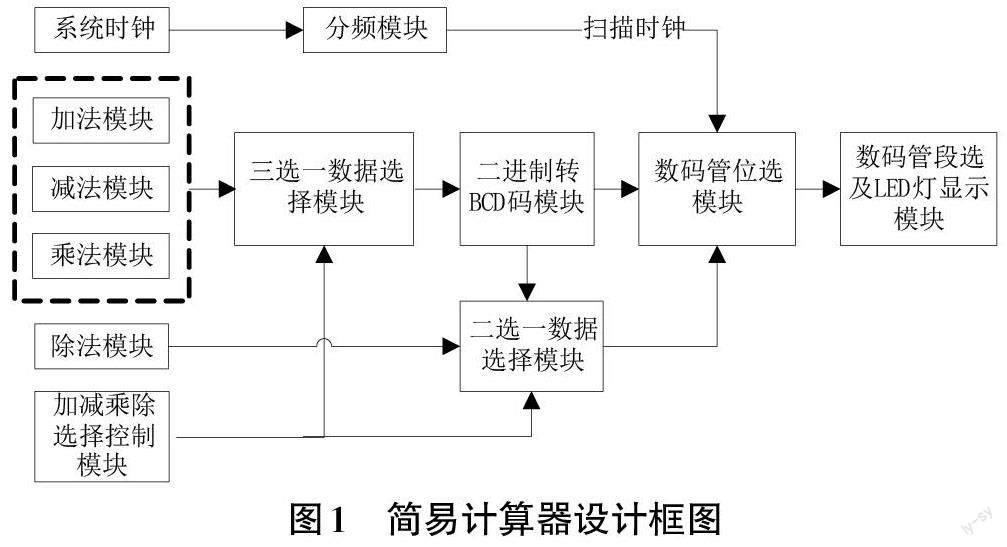

简易计算器设计框图如图1所示,根据设计要求,简易计算器电路分为六部分,分别是分频、运算、选择控制、数据选择、码制转换和显示。分频是将高频率的系统时钟50MHz转为用于数码管动态扫描的较低频率时钟10KHz;运算包括加减乘除运算四个模块,实现四则运算功能;选择控制用于选择不同的独立按键实现加减乘除四种运算操作;数据选择包括三选一和二选一数据选择模块,三选一数据选择模块实现对加法、减法、乘法運算结果的选择,二选一数据选择模块实现除法运算结果和加减乘运算结果的选择;码制转换是把加减乘运算结果的二进制数据转换为8421BCD码,便于后面数码管的显示;显示包含数码管的位选、段选和LED显示,用于展示运算结果。

3 简易计算器设计本设计

采用层次化的设计方法,即先设计底层电路再设计顶层电路。底层电路用Verilog HDL语言来实现,顶层电路通过调用底层电路用原理图方式来实现[3]。

3.1 底层电路设计

底层电路有11个模块,分别是5000分频模块、加法模块、减法模块、乘法模块、除法模块、加减乘除选择控制模块、三选一数据选择模块、二选一数据选择模块、二进制转8421BCD码模块、数码管位选模块和数码管段选及LED灯显示模块。下面对它们进行分别介绍。

3.1.1 5000分频模块

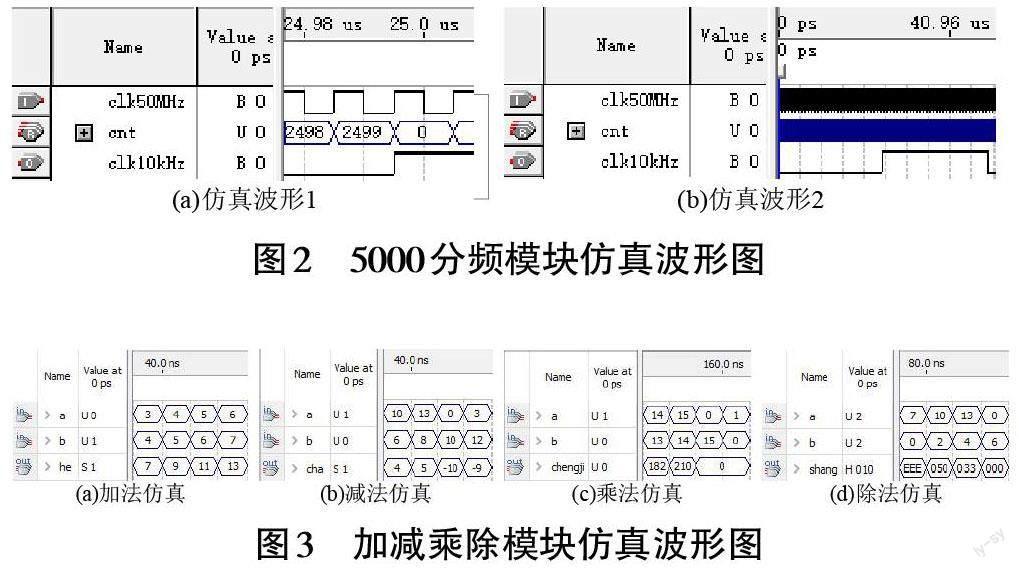

5000 分频模块是实现50MHz 系统时钟分频为10KHz时钟,用于数码管的动态扫描[4]。图2为5000 分频模块仿真波形图,从图2(a)可以看出,对于输入时钟clk50MHz,每来一个上升沿就计数一次,当计到2499时,输出时钟clk10KHz进行翻转。也就是说计数5000次,输出时钟有一半是低电平有一半是高电平,实现了1 比1 的5000 分频时钟信号,如图2(b) 所示。

3.1.2 加减乘除模块

加减乘除模块输入的2个操作数为四位二进制数据,加减乘运算输出结果用八位二进制数据表示,除法运算输出结果用12位8421BCD码显示。图3为加减乘除模块的仿真波形图,输入数据都设为无符号十进制数,输出结果加法和减法设为有符号十进制数、乘法设为无符号十进制数,除法设为十六进制数。由图3(a)(b)(c)可以看出,加法运算、减法运算、乘法运算,运算结果均正确。对于除法运算,当除数为0时,运算结果为无穷大,结果显示为EEE;当除数不为0时,运算结果保留到小数点后一位,例如13除以4,运算结果为3.3,显示值用033表示。

3.1.3 加减乘除选择控制模块

加减乘除选择控制模块通过选择不同的独立按键,使输入的两个操作数进行对应的四则运算,在无独立按键按下时,默认输出为加法运算结果。图4为加减乘除选择控制模块仿真波形图,输入信号s0、s1、s2、s3代表四个独立按键,输出信号m为加减乘除运算控制信号,当m 为“1000”时代表加法运算,为“0100”时代表减法运算,为“0010”时代表乘法运算,为“0001”时为除法运算。因为独立按键正常情况是弹起状态,所以弹起时用高电平表示,按下用低电平表示。可以看出,当s0、s1、s2、s3分别为X、1、1、1时(X 代表0或1) ,m为“1000”;当s0、s1、s2、s3分别为1、0、1、1时,m为“0100”;当s0、s1、s2、s3分别为1、1、0、1 时,m为“0010”;当s0、s1、s2、s3分别为1、1、1、0时,m 为“0001”。

3.1.4 三选一数据选择模块

三选一数据选择模块是在选择控制信号m的驱动下,对加减乘三种运算的结果进行选择输出,输入信号有加法运算结果he、减法运算结果cha、乘法运算结果chengji、选择控制信号m;输出信号为out,它的数值为he、cha、chengji中的一个。图5为三选一数据选择模块仿真波形图,可以看出,当m为“1000”时,out 的数值和he相同;当m为“0100”时,out的数值和cha 相同;当m为“0010”时,out的数值和chengji相同。

3.1.5 二选一数据选择模块

二选一数据选择模块是在控制信号m的作用下,从二进制转8421BCD码模块输出信号out_bcd和除法结果shang中选一个进行输出。输入信号有8421BCD 码out_bcd、除法运算结果shang、选择控制信号m;输出信号为运算结果jieguo。当m为“0000”或“1000”或“0100”或“0010”时,jieguo为out_bcd的数值;当m为“0001”时,jieguo为shang的数值。

3.1.6 二进制转8421BCD 码模块

二进制转8421BCD 码模块是利用二进制数转8421BCD码原理[5],将四位二进制输入信号转为八位BCD码,将八位二进制输入信号转为十二位BCD码数。输入信号有操作数a和b、加减乘运算结果out;输出信号有8421BCD 码a_bcd、b_bcd 和out_bcd。图6 为二进制转8421BCD码模块仿真波形图,可以看出,输入的a、b、out二进制数据经过转换后得到的BCD码正确。例如当b为二进制数据“1111”时,其十进制数为15,BCD码为“00010101”,与仿真结果一致;当out 为二进制数据“00110100”时,其十进制数为52,BCD 码为“000001010010”,与仿真结果一致。

3.1.7 数码管位选模块

数码管位选模块采用动态扫描的方式用八个数码管来表示输出,从左边数起前面四个数码管显示操作数a和b,第五个数码管显示符号“=”,最后三个数码管显示运算结果。输入信号有动态扫描复位信号reset,扫描时钟clk10KHZ,操作数a和b,8421BCD码a_bcd、b_bcd、out_bcd,选择控制信号m;输出信号有位选控制信号sel和输出数据dataout。

图7 为数码管位选模块仿真波形图,此时m 为“0100”,实现的是减法运算。被减数a_bcd为十进制数5(BCD码为00000101) ,减数b_bcd为十进制数3(BCD 码为00000011) ,差out_bcd 为十进制数2(BCD 码为000000000010) 。理论上数码管从左至右顯示应为“0503=002”,即5减3等于2。因为数码管显示采用的是动态扫描的方式,所以每一时刻只有一个数码管被点亮,例如当sel为“10000000”时,表示最左边的数码管点亮;sel为“01000000”时,表示从左边数起第二个数码管点亮;sel为“00100000”时,表示第三个数码管点亮等。

dataout为数码管显示的数值,可以看到,当sel为“10000000”时,dataout 显示的是第一个数码管的值0;当sel 为“01000000”时,dataout显示的是第二个数码管的值5;当sel为“00100000”时,dataout显示的是第三个数码管的值0;当sel 为“00010000”时,dataout显示的是第四个数码管的值3;当sel为“00001000”时,dataout显示的是第五个数码管的值“=”(编码用十进制数10 表示);当sel 为“00000100”时,dataout显示的是第六个数码管的值0;当sel为“00000010”时,dataout显示的是第七个数码管的值0;当sel 为“00000001”时,dataout显示的是第八个数码管的值2。这一仿真结果与理论数值一致。

3.1.8 数码管段选及LED 灯显示模块

数码管段选及LED灯显示模块中,输入数据da?tain为数码管显示的数值,为了显示除法运算的结果(除法运算结果带小数点),输入信号加入了数码管位选信号sel和运算控制信号m,输出信号有数码管段选信号seg和LED灯显示信号led。

图8为数码管段选及LED灯显示模块仿真波形图,输入数据datain 为3,数码管采用的是共阳极显示,理论上显示“3”时段选信号seg 输出编码为10110000,若显示“3.”(带小数点)时则编码为“00110000”。从仿真波形可以看出,当m为加法运算(1000) 、减法运算(0100) 和乘法运算(0010) 时,运算结果都不会有小数点,且seg输出正确;当m为减法运算(0001) 时,只有倒数第二个数码管显示会带小数点,seg输出结果与理论一致。另外,进行加减乘除运算时,led都有三个灯点亮,仿真结果与设想一致。

3.2 顶层电路设计

简易计算器顶层电路是用原理图设计方式进行设计,通过调用已生成的各底层模块元件符号,并将它们连接就可实现顶层电路,如图9所示。

4 简易计算器的硬件实现

本设计采用小梅哥AC101-EDA 开发板作为硬件验证平台,在设计好顶层电路的基础上,进行管脚锁定,编译并将生成的文件下载到FPGA开发版上进行硬件验证。硬件验证现象如图10所示,(a)、(b)、(c)、(d)分别为加减乘除运算及其显示结果,可以看出,显示的运算结果与理论数值一致,并且在进行不同的运算时相应的LED灯会被点亮,这说明所设计的电路完全实现了简易计算器的设计要求。

5 结束语

本文通过Quartus II 13.1软件和小梅哥AC101-EDA开发板设计了一款简易计算器。首先,通过对功能需求的分析,将设计分为六部分,包含11个底层电路模块;然后在Quartus II 13.1软件上通过Verilog HDL语言和原理图相结合的方式设计了底层电路和顶层电路;最后把顶层电路下载到FPGA开发板中进行了硬件测试,结果表明,所设计的简易计算器能实现设计要求的所有功能,具有一定的实用价值。

【通联编辑:朱宝贵】