实用ARM9嵌入式硬件开发平台设计

冯 杰 李述良

摘要:文章采用Samsung公司S3C2440A微处理器设计了嵌入式系统硬件开发平台,给出了硬件结构设计思路,着重分析了以太网端口和IIS音频接口,简要的说明了USB接口,UART接口,含触摸屏的LCD接口电路的设计方法,并总结了嵌入式系统测试和调试的基本方法。

关键词:嵌入式系统;ARM;硬件设计;S3C2440A

中图分类号:TP303文献标识码:A文章编号:1006-8937(2009)10-0014-02

随着计算机技术、微电子技术和网络技术的迅速发展,嵌入式系统在工农业等诸多领域得到了广泛的应用。传统的8位单片机已经暴露了本身资源有限的缺点,越来越不能适应日渐复杂的应用需求,而随着32位处理器价格的不断下降,采用更高性能的32位处理器作为嵌入式系统的核心成为更加合理的选择。ARM处理器是目前公认的业界领先的32位嵌入式RISC微处理器,已成为许多行业嵌入式解决方案的RISC标准。开发一个集嵌入式控制、高速数据采集和网络通信于一体,并提供友好的人机操作界面的硬件平台和多种总线接口,对于提高智能嵌入式系统可靠性、组网灵活性很有意义。据此文章主要以S3C2440A为例,完成了以太网接口,USB接口,UART接口,含触摸屏的LCD显示接口,IIS音频接口以及电源管理单元电路的嵌入式系统的硬件开发平台设计。

S3C2440A是Samsung公司设计的一款高性价比16/32位ARM9系列微处理器,内含一个由ARM公司设计的16/32位ARM920T RISC处理器核,采用五级流水线和哈佛体系结构,工作频率最高可达533MHz;同时还具备体积小、成本低、功耗低、资源众多等诸多特点。内部集成的常用资源主要有:外部存储控制器(SDRAM控制和片选逻辑);(最大支持4K色STN和256K色TFT屏),提供1通道LCD专用DMA;4通道DMA并有外部请求引脚;3通道UART(IrDA1.0,64字节TxFIFO和64字节RxFIFO);2通道SPI;1通道IIC-BUS接口(支持多主机);1通道IIS-BUS音频编码解码器接口;AC97解码器接口;兼容SD卡接口协议1.0版和MMC卡2.11版;2端口USB主机和1端口USB设备;4通道PWM定时器和1通道内部定时器,看门狗定时器;8通道10比特ADC和触摸屏接口;具有日历功能的RTC;相机接口(最大支持4096*4096像素);130个通用I/O口和24通道外部中断源等资源。这些资源大大的方便了应用系统的开发,同时节约开发成本,缩短开发周期,提高了系统的性价比。对于S3C2440A的特点和性能请查阅相关资料,文章不作叙述。

1嵌入式系统的硬件电路设计

1.1硬件系统结构

为降低系统开发难度,方便二次开发,系统采用核心板加底板的设计方案,核心板和底板之间通过连接器相连。这样可以在核心板不变动的情况下,更改底板的功能组成,以适用不同的功能。同时,由于核心板采用多层PCB板设计,而底板采用双层板即可,从而大大的降低了系统的成本。系统硬件结构如图1所示。

1.2核心板电路构成

微处理器:即S3C2440A,为系统的控制中心。

Flash电路:用于存放嵌入式操作系统及用户应用程序,其特点是系统掉电后数据不易丢失。

SDRAM电路:系统代码的运行场所,其特点是系统掉电后数据即丢失。

晶振电路:12MHz 的无源晶振通过芯片内部的PLL电路为S3C2440A芯片提供高达533MHz的时钟频率。

JTAG接口:采用ARM公司的提供的标准20脚JTAG仿真调试接口电路,S3C2440A芯片内部有JTAG核,因此,可以通过外部JTAG调试电缆或仿真器与开发系统连接调试和编程。

复位电路:为系统提供复位信号。为防止干扰信号引起误复位操作,常采用专用复位芯片来产生复位信号。如:MAX811等。

1.3扩展板电路

S3C2440A本身就集成了USB Host 控制器和USB Device 控制器、LCD控制器、3个独立的、可以工作在基于中断和DMA模式下的串行口,并接支持红外发送、接收功能,SD卡和MMC卡控制器、摄像头接口等。因此,上述接口电路只需要参照芯片使用手册接线即可使用。

1.3.1网络接口设计

S3C2440A本身并没有网络接口,通过扩展网络接口的模式可以为系统提供以太网接入;以太网接入是本系统的一个重要的功能模块,为系统进行下载文件、远程调试等操作提供了条件。原理图如图2所示。

本系统的以太网控制电路由以太网芯片、网络隔离变压器和RJ-45接口组成,选用的以太网芯片为DM9000。这是一款提供了通用处理器接口的以太网控制芯片。DM9000内部集成了MAC 和PHY,它能提供10/100Mbps的PHY 接口。它为处理器提供了8 位和16 位数据宽度的内部存储访问接口,并且内部包含了4K 的Dword SRAM。网络隔离变压器的作用主要有两个:?譹?訛传输数据,它把PHY 送出来的差分信号用差模耦合的线圈耦合滤波以增强信号,并且通过线圈耦合到不同电平的另外一端连接到网线;?譺?訛隔离网线连接的不同网络设备间的不同电平,以防止不同电压通过网线传输损坏设备。

1.3.2IIS音频接口设计

IIS是一种串行总线设计技术,主要针对数字音频处理技术和设备,如便携CD机、数字音频处理器等。IIS将音频数据和时钟信号分离,避免由时钟带来的抖动问题,因此,系统中不再需要消除抖动的器件。

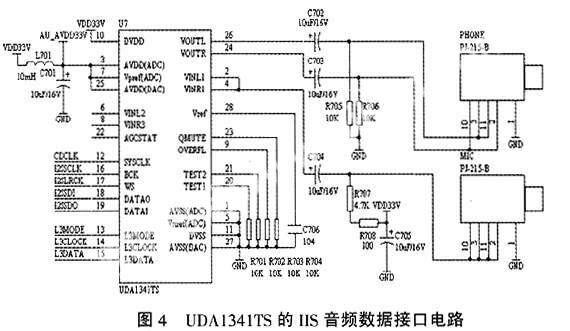

IIS总线仅处理音频数据,其它信号(如控制信号)单独传送。基于减少引脚数目和布线简单的目的,IIS总线只由3根串行线组成,即时分复用的数据通道线(continuous serial clock,SCK)、字选择线(word select,WS)和时钟线(serial data,SD)。使用IIS技术设计的系统的连接配置如图3所示。其中WS信号线指示左通道或右通道的数据将被传输,SD信号线按高有效位MSB到低有效位LSB的顺序传送字长的音频数据,MSB总在WS切换后的第一个时钟发送。如果数据长度不匹配,接收器和发送器将自动截取或填充。文章中使用的音频芯片是PHILIPS公司的UDA1341TS音频数字信号编译器。UDA1341TS可以将立体声模拟信号转换为数字信号,同样也可以将数字信号转换为模拟信号,并且可用PGA(可编程增益控制)和AGC(自动增益控制)对模拟信号进行处理。对于数字信号,该芯片提供了DSP(数字音频处理)功能。IIS音频数据接口电路如图4所示。本系统把IIS音频数据接口与PHILIPS公司的UDA1341TS音频数字信号编译器相连接,得到MICROPHONE音频输入通道和SPEADER音频输出通道。

2嵌入式系统调试和测试

2.1调试环境

PCB板制作好后,进行系统调试需要进行硬件调试和软件调试两个过程。其中,硬件调试需要使用示波器、万用表、稳压电源等工具;软件调试则使用SJF2440软件或H-Jtag软件烧写系统引导程序和测试程序。焊接PCB时应首先焊接电源模块,只有在电源模块测试正常时才能焊接其它的模块,否则在通电测试时会损坏其它模块的芯片;另外,在进行测试时还要注意避免人为造成的短路现象。

2.2硬件调试

①加电前的检查:加电调试之前要对照电路原理图和实际线路进行检查,看PCB板是否有短路、断路情况,看在元器件焊装过程中是否有错装、短路、错接、多接、少接等现象;用万用表检测焊接和接插件是否良好;各焊点之间有无短路,焊点是否存在虚焊;集成电路芯片是否焊装正确,二极管、三极管、电解电容等有极性的器件的极性是否正确;电源的极性连接是否正确、正负极间是否存在短路的情况。

②加电检测和调试:做完加电前的检查,确认无误后,电源输入端接入5V电压。观察有无异味、冒烟、器件发烫等现象。当发现有异常情况时要立即切断电源,并根据故障现象分析故障原因,然后排除。如无异常,用万用表分别测量个关键点和各集成芯片的电源端的电压值,各输入和输出端的高、低电平值及逻辑关系等是否正常。如若这些都没有问题,就通过示波器来检测各相关点的波形是否正常,然后根据波形来分析故障的原因,直至最终故障排除。

2.3软件调试

在PC机上运行SJF2440或H-Jtag软件,烧写已经编译好的系统引导程序,看系统能否正常启动,输出是否正常,烧写系统测试程序看输入输出是否正确,否则分析原因并排除故障。烧写前要确保引导程序和测试程序是正确可用的。

3结 语

本系统使用S3C2440A 进行嵌入式系统硬件平台的搭建,为系统的进一步开发做好了准备。本系统采用核心板加底板的设计方案,方便二次开发。要实现不同的功能,只需要更改底板的设计即可,降低了开发难度和开发成本,也缩短了开发周期。

参考文献:

[1] 江俊辉.基于ARM的嵌入式系统硬件设计[J].微计算机信息,2005,(21):120-122.

[2] 田泽.ARM9嵌入式开发实验与实践[M].北京:北京航空航天大学出版社,2006.