基于PCI Express接口的高速数据传输系统设计

周晓波,夏 敏,邹浩杰

(北京交通大学 电子信息工程学院,北京 100044)

高速铁路列车具有很高的运行速度,其无线通信网络需要适应高速的移动环境,支持列车最高速度500 km /h和平均速度350 km /h的运行情况。较高的运行速度会增加无线通信数据传输的误码率,并且会造成信号的衰落率较高,即信号的变化较快。因此需要快速跟踪信道参数的变化,以降低无线传输的误码率。

对信道参数的跟踪面临高速数据的采集和传输问题。目前,国内大部分的高性能数据采集卡都是基于PCI、CPCI和VME等总线,最高传输速率难以超过400 Mit/s。为解决传统数据传输的瓶颈,提出基于PCI Express接口的高速传输系统设计方案。

1 PCI Express拓扑和链路结构

经简化的PCI Express系统拓扑结构中包括:根联合体、交换器、终端和桥,如图1。每条虚线均代表两个PCI-E(PCI Express)设备之间的一条连接,这种连接称为链路。

(1)根联合体用于初始化整个PCI-E结构并配置每条链路,将中央处理器(CPU)与交换器、终端和PCI-E to PCI桥这3项功能之中的一个或多个相连接。

(2)交换器用于将数据向下游路由并传送至多个PCI-E端口,以及从每个独立端口将数据向上游路由并传送至单一的根联合体。PCI-E交换器也可以从一个下游端口灵活地向另一个下游端口路由并传送数据,不再局限于传统PCI系统所要求的严格的树形结构。

(3)终端通常驻留在应用内,用于在系统中将应用连接到PCI-E网络。终端具有请求和完成PCI-E事务处理的功能。

(4)PCI-E to PCI桥用于将PCI-E与其他PCI总线标准(如PCI/PCI-X)相连接,适用于同时采用了这些体系架构和PCI-E的系统。

图1 PCI Express系统拓扑结构

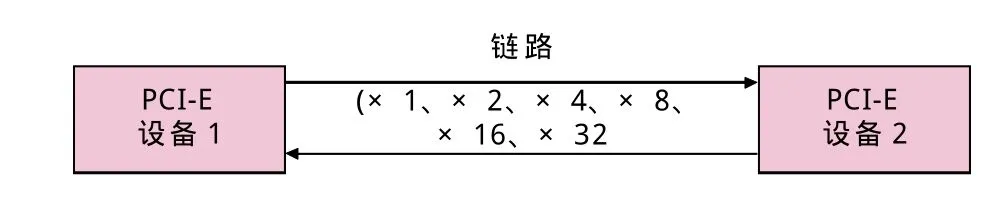

PCI Express设备之间为链路形式的互连,如图2。在每个方向上都可以有×1、×2、×4、×8、×16 或×32 个信号对, 这些信号对称为通道,每条通道在每个方向上的发送和接收速率为2.5 Gbit/ s。

图2 PCI Express链路结构

2 系统设计

2.1 系统分析

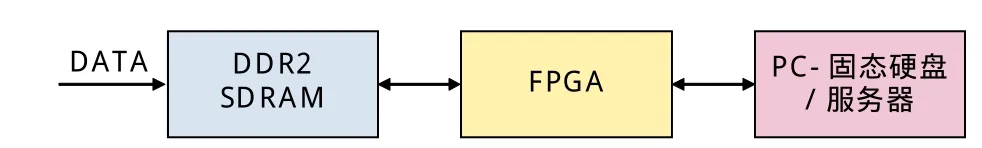

数据流向如图3,其中,第2代双倍数据率同步动态随机存取存储器(DDR2 SDRAM)对数据(DATA)进行缓存,FPGA主要完成数据的处理和传输,PC—固态硬盘/服务器,主要完成对数据的存储和后期处理。

图3 数据流向

FPGA是在复杂可编程逻辑器件(CPLD)的基础上发展起来的新型高性能可编程逻辑器件,集成度很高,可以完成极其复杂的时序与组合逻辑电路功能,适用于高速和高密度的高端数字逻辑电路设计领域。高性能的固态硬盘提供极大的存储空间或者利用服务器通过廉价冗余磁盘阵列(RAID)技术提供近乎无限的存储空间, 而且使得数据存取速率成倍提升, 又有充足的运算资源进行数据采集的后期处理。本文主要讨论采用PCI Express接口实现将采集的高速数据传输到固态硬盘的技术,以及高速数据传输系统的设计。

2.2 设计方案

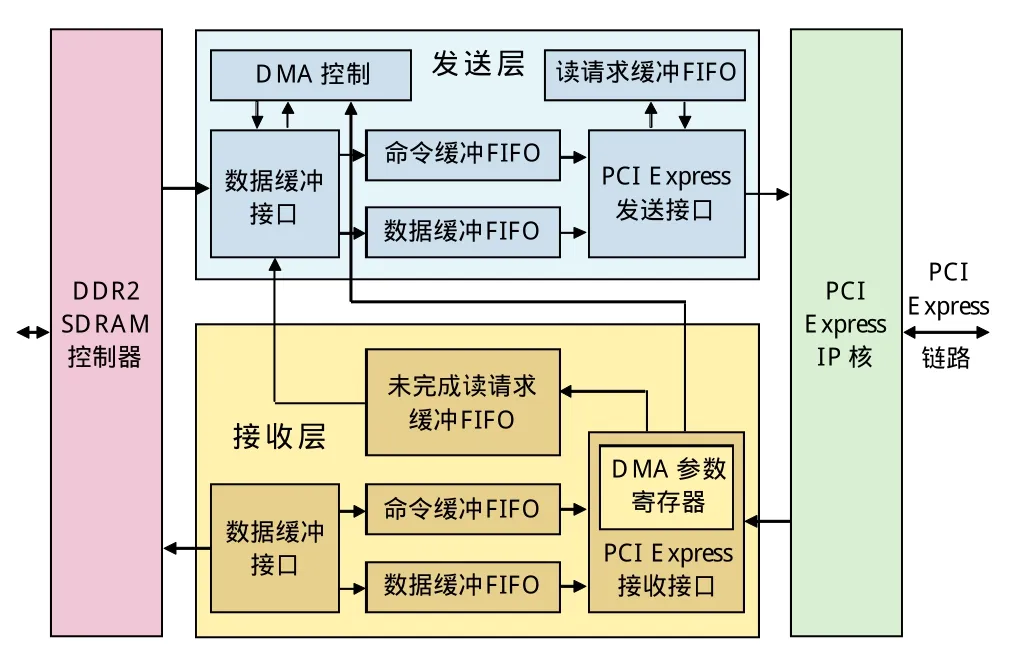

本设计方案中采用模块化设计思想。为提高设计性能,降低产品开发成本,缩短设计周期,采用IP核实现PCI Express协议和对DDR2 SDRAM的控制。

对设计方案进行如图4的模块划分。在可编程逻辑器件领域,IP(Intellectual Property)核是指将一些数字电路中常用但比较复杂的功能模块,设计成参数可修改的模块,让其他用户可以直接调用这些模块,从而简化设计,缩短开发周期。

图4 模块划分

2.3 各模块实现功能

2.3.1 DDR2 SDRAM控制器

DDR2 SDRAM控制器是通过行地址选择(RAS#)、列地址选择(CAS#)、写使能(WE#)、时钟使能(CKE)和芯片选择(CS#)一组控制信号线组合成控制命令,完成对DDR2 SDRAM的操作,如写命令、读命令和空操作、加载模式寄存器、自动刷新、预充电、选择组激活行等。

2.3.2 PCI Express模块

PCI Express采用数据包方式在系统应用层内传输数据,并用于数据接口与PCI-E设备的各层之间。应用层用于发起事务处理,而事务处理层用于将应用程序的请求转换成PCI-E事务处理包。数据链路层用于为这个包添加一个序列编号和链路循环冗余校验码(LCRC)。数据链路层还确保了双向事务处理能够正确地得到接收。最终,物理层能够通过PCI-E链路发送事务处理。

PCI Express IP核能够实现PCI Express接口协议中处理层、数据链路层和物理层的逻辑功能。

2.3.3 发送层和接送层

发送层和接送层主要完成对传输数据的缓冲和处理,实现数据的发送和接收功能。

2.3.4 数据缓冲接口模块

数据缓冲接口模块主要实现与前端接口对接,并对数据进行合并或者拆分的处理。检查在接收层中未完成读请求缓冲FIFO中是否还有未完成的读请求命令,如果有则通过DDR2 SDRAM控制器读取DDR2 SDRAM中的数据并将相应的命令和数据分别写入命令缓冲FIFO和数据缓冲FIFO;在接收层中,通过命令缓冲FIFO和数据缓冲FIFO与DDR2 SDRAM控制器进行交互,完成数据的读取和写入。

2.3.5 DMA控制模块

DMA控制模块使得外部设备可以发起对存储器或其他外部设备进行直接读和写的操作,进行数据交换,不需要经过CPU,减少中间环节,提高传输速度。本设计方案中,通过设置接收层中的DMA参数寄存器,DDR2 SDRAM可以直接对存储器进行DMA读和写操作 。

2.3.6 数据缓冲FIFO模块

数据缓冲FIFO模块主要实现对传输数据的缓冲以及DDR2 SDRAM和PCI Express IP核之间的跨时钟域,使得数据传输同步,不丢失数据。

2.3.7 命令缓冲FIFO

命令缓冲FIFO模块在接收层中将对从PCI Express IP核中接收到的数据包分解出的写请求和完成请求命令进行缓存,在发送层中对读请求命令、写请求命令、完成请求命令进行缓存。

发送层的PCI Express发送接口通过命令缓冲FIFO和数据缓冲FIFO形成数据包送入PCI Express IP核,接收层的PCI Express接收接口则对来自PCI Express IP核的数据包进行分解,并将相应的命令和数据送入未完成读请求FIFO、命令缓冲FIFO、数据缓冲FIFO或者发送层的DMA控制模块。

2.4 验证与仿真

利用Quartus II 联合ModelSim对设计的相应模块及整个方案进行仿真验证。

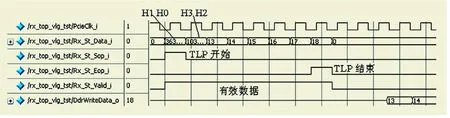

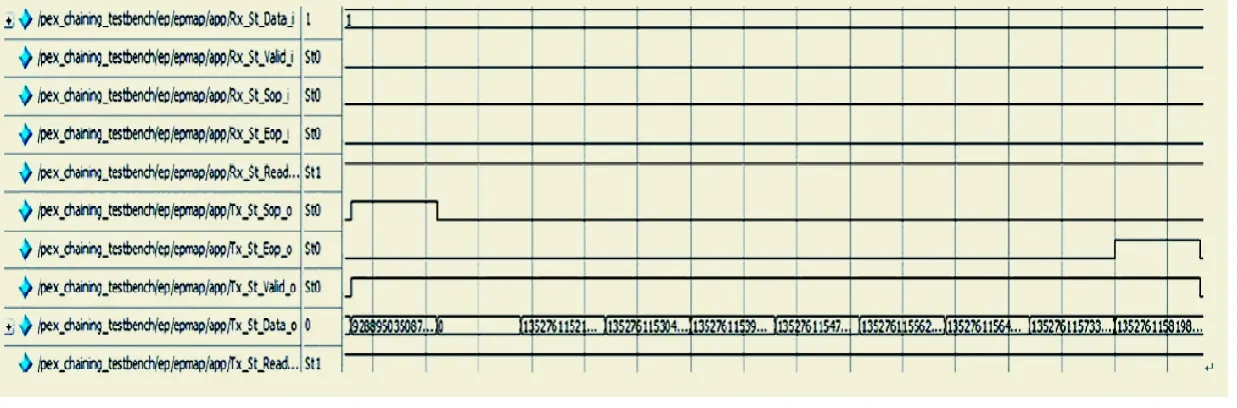

发送层和接收层数据时序如图5和图6。其中,TLP为数据包,H代表数据包的头信息。

图5 发送层时序图

图6 接收层时序图

采用PCI Express IP核实现了PCI-E设备层中的处理层、数据链路层和物理层的逻辑功能。通过PCI Express IP 核提供的接口信号,实现数据的发送和接收。应用层只将数据封装成数据包TLP或者对数据包TLP进行解析。

从图5和图6中可知,发送层和接收层的数据时序符合PCI Express1.0的协议规范中对处理层数据包TLP格式的要求。

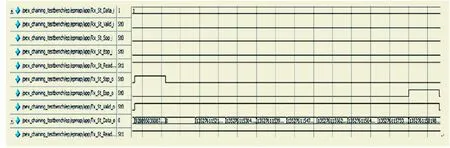

对DDR2 SDRAM控制器、发送层、接收层、PCI Express IP核整个方案进行仿真与验证,编译库和模块文件,下载设计文件,对相关寄存器进行配置、建立链路训练。在发送端和接送端截取相关数据信号的时序图,如图7和图8。

图7 发送端一帧数据

图8 接收端一帧数据

通过图7和图8可以看出,除去数据包的头信息和尾信息,发送端的一帧数据和接收端的一帧数据相同,因此表明发送和接收的数据一致,保证了数据传输的完整性。

3 结束语

第三代I/O互连总线PCI Express 是解决数据传输数据瓶颈问题的关键途径,有着广泛的应用前景。本文设计并实现了基于PCI Express 接口的高速数据传输系统,采用PCI Express1.0协议,目前可实现2.5 Gbit/ s的数据传输速率, 对方案进行改进,理论上可获得5 Gbit/ s甚至更高的

数据传输速率。本系统方案已应用于高速数据采集卡中,且运行稳定可靠。

[1]夏宇闻.Verilog数字系统设计教程[M].北京:北京航空航天大学出版社,2003.

[2]Ravi Budruk, Don Anderson, Tom Shanley.PCI Express系统体系结构标准教材[M].田玉敏,王 崧,张 波. 北京:电子工业出版社,2005.

[3]PCI-SIG. PCI ExpresR. 2.0Base Specification Revision 0.9[EB/OL]. http://www.pcisig.com/specifications/pciexpress/.

[4]Altera Corporation.PCI Express to External Memory Reference Design [EB/OL]. http://www.altera.com/support/refdesigns/ip/interface/ref-pciexpress-ddr3-sdram.html? GSA_pos=1&WT.oss_r=1&WT.oss=PCIExp ress to External Memory Reference Design.

[5]Altera Corporation. External Memory Interface Hand-book Volume 3—Section I.DDR and DDR2 SDRAM Controllerswith ALTMEMPHY IP User Guide [EB/OL]. http://www. altera.com/literature/hb/external memory/emi_ip.pdf GSA_pos=1&WT.oss_r=1&WT.oss=External Memory Interface Handbook Volume.

[6]Altera Corporation.PCI Express Compiler User Guide [EB/OL]. http://www.altera.com/literature/ug/ug_pci_express.pdf?GSA_pos=1&WT.oss_r=1&WT.oss=PCI Express Compiler User Guide.