一种面向复合导引头信号处理应用的SoC设计

高维, 郑鑫, 王凤姣

(1.海装兵器部,北京 100841;2.上海航天技术研究院,上海 201109;3.上海无线电设备研究所,上海 200090)

一种面向复合导引头信号处理应用的SoC设计

高维1, 郑鑫2, 王凤姣3

(1.海装兵器部,北京 100841;2.上海航天技术研究院,上海 201109;3.上海无线电设备研究所,上海 200090)

SoC技术应用于战术武器型号具有较大的优势,随着关键元器件自主化研制需求的增大,突破SoC应用于战术武器型号中的关键技术,研制满足军用需求的高性能SoC已迫在眉睫。文章介绍了SoC的概念与关键技术,分析、归纳了某战术型号复合导引头信号处理平台的通用需求,提出了一种采用AHB总线架构、集成32位RISC-CPU、专用算法IP核的SoC实现方案。

导引头;信号处理;设计方案

0 引言

随着战场环境的日益复杂,为了适应不同作战需求,弹载实时处理系统主要依靠大规模集成电路实现复杂处理算法和时序控制。当前弹载高速实时信息处理系统当前大多采用DSP+FPGA模式,其中FPGA完成预处理功能,DSP实现后续的信息处理,具有极大的同构性,但是DSP+FPGA等关键元器件主要通过进口实现,给自主化保障及技术创新带来了限制。一方面,进口器件的关键等级与综合成本居高不下提高了硬件成本;另一方面,国外长期的高科技封锁也限制了国内芯片研制、封装的基础能力,造成国内高性能元器件的供给面临日益严峻的形势。

SoC(System on Chip)技术是一种系统集成技术,其核心思想是将专用算法电路、核心处理器以及外围电路集成到一个芯片中,以具备更低的功耗、更高的可靠性以及更强的通用性等,更利于系统设计向小型化、通用化、低功耗、高可靠性的方向发展。

SoC技术以其固有的小型化、低功耗和平台化特点与战术武器型号小型化、低功耗和系列化发展要求相一致。同时,战术武器型号批量大的特点、处理平台通用化的趋势也降低了SoC技术的开发成本。在关键元器件尤其是大规模集成电路受制于外的现实背景下,通过应用SoC技术,实现战术武器型号关键元器件的自主保障,具有重要的战略意义。

本文从SoC技术应用角度出发,介绍了SoC技术的特点以及当前在民用领域的设计思想和取得的成果,同时结合弹载平台应用需求,提出了一种采用AHB总线架构、集成32位RISC-CPU、专用算法IP核的SoC设计方案。

1 SoC技术概述

SoC广义上是指在一个芯片内集成一个完整的系统,从而构成一个能够实现信号采集、转换、存储、处理、I/O等功能的集成系统[1]。SoC通常由主控单元、接口单元及一些功能模块组成。主控单元通常是一个处理器;模块单元主要包含集成传感器、模拟电路、数字处理电路等[2];接口单元包含IO接口、AD/DA接口、通信接口等。

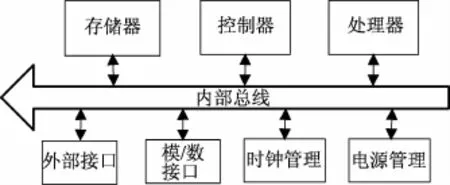

根据SoC的定义,一个典型的SoC结构主要包括处理器、存储控制器、存储器、IO接口、ADC、时钟、电源管理、部分外围电路、内部总线、总线控制器等。如图1所示。

图1 典型SoC结构

SoC一般具有如下特点:

a)具备强大的数据处理;

b)具备海量数据存储能力;

c)具有灵活的软硬件可编程能力[3];

d)采用符合AMBA2.0标准的片上总线。

具体体现如下[4]:

a)一般采用超深亚微米工具技术实现;

b)是一个经嵌入式微处理器、存储设备和I/ O接口集成到一个芯片上的复杂系统;

c)是一个软、硬件并存的系统;

d)采用可重用设计,即硬件部分采用IP核重用,软件部分采用软件构架重用;

e)由IP核、软件构建和用户自定义逻辑(UDL:User Defined Logics)模块搭建而成。

与传统的IC设计不同,SoC技术从整个系统的角度出发,把模型算法、芯片结构、各层次电路设计紧密集合起来考虑,在单个芯片上一次性完成了整个系统的功能[5]。

2 民用SoC设计思想及应用

SoC技术在当前民用市场3C产品中取得了成功的应用,这主要得益于SoC技术在功能、体积、性能以及产品研发周期上的优势。

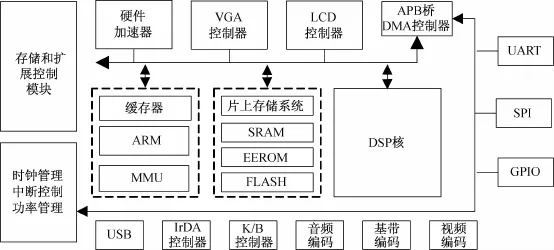

我国在民用领域主要使用的处理内核是ARM、MIPS等,主要以ARM为主,其典型架构如图2所示。基于ARM的CPU内核在功耗控制、媒体运算方面具有较大的优势,因而成为了面向民用3C市场的主流SoC系统架构。

图2 面向消费类电子市场的基于ARM处理器内核的典型SoC架构

由图2可以看出民用SoC系统主要架构包含如下部分。

(1)系统主核

分为以下三部分:

a)主核:ARM core;

b)处理器:DSP core;

c)总线结构:AHB总线及APB总线控制单元,单总线结构。

(2)I/O接口及常用外设

分为以下五部分:

a)SPI模块;

b)GPIO可复用;

c)UART控制器;

d)各类驱动I/O管理、控制时序逻辑生成集成接口;

e)高速DDR3存储器等。

民用SoC系统的部分处理器及外设接口与当前军用产品类似,可以作为军用SoC系统设计的参考,但同时还需要明确两者之间存在的差异,如硬件结构特点、操作系统选取与移植、应用软件设计、软件算法优化等方面。面向军用的专用总线协议在民用技术中积累较少,民用SoC系统的可靠性设计尚未达到军用要求等也制约军用SoC系统的开发与应用。

虽然军用SoC系统的设计与开发存在较大困难,但是其低功耗、小型化以及高可靠性等方面的优势使得SoC产品成为军用领域未来的主要产品。在军用方面,雷达导引头是SoC技术的一个重要应用领域。随着导引头系统复杂化,复合制导模式越来越多,复合导引头大多涉及两种或以上工作模式,不同模式需要具备独立的工作环境以及系统间信息融合,导致导引头系统较为庞大,使得小型化难度较大。与此同时,复合导引头采用的控制器件和信号处理器件普遍靠国外进口,给国产化带来较大阻碍。

本文根据民用SoC发展情况,借鉴其设计思想和成功应用经验,发展面向复合导引头的SoC技术,设计主要面向系统级设计与验证、IP核复用技术以及可测试性技术等,促使系统设计向小型化、通用化、低功耗、高可靠性的方向发展。

3 面向复合导引头SoC设计

面向复合导引头SoC设计是一个系统级软硬件协同工作的过程,设计关键技术主要包含系统级设计及仿真验证技术、标准IP核设计技术、可测试性技术等。

3.1 系统级设计与仿真验证技术

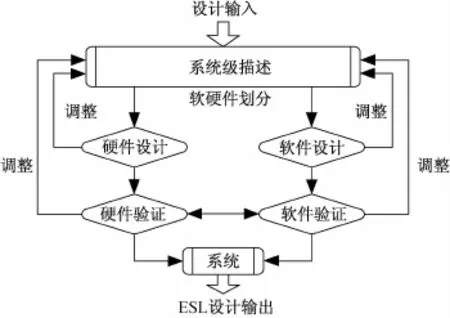

随着电子系统设计复杂度不断增加,电子系统设计趋势由早期的RTL级设计向电子系统级(ESL,Electronic System Level)设计方式演进。ESL设计包括SoC系统、FPGA系统、板上/多板级系统等。ESL设计中,系统的描述和仿真速度较高,可以保证充裕的时间来分析设计内容。ESL设计不仅能应用在设计初期与系统架构规划阶段,亦能支持整个硬件与软件协同设计的流程。系统级设计与仿真验证流程图如图3所示。

系统级设计与仿真验证设计主要包含:设计输入及系统级描述形成阶段、软硬件划分阶段、软硬件协同验证阶段、系统设计输出阶段。各阶段的主要作用:

图3 系统级设计与仿真验证流程

a)设计输入及系统级描述形成阶段主要提出一种系统的结构并用语言描述该结构,即系统级描述;

b)软硬件划分阶段根据系统级描述在高抽象层次上进行建模完成功能设计;

c)软硬件协同验证阶段根据软硬件划分结果建立系统虚拟平台,映射到硬件结构上,进行验证与性能分析;

d)系统设计输出阶段主要完成验证的软件设计与硬件设计,形成完整的系统级设计,传递给下一级的设计作为输入。

3.2 标准IP设计技术

基于IP复用的SoC技术是SoC设计的关键,标准IP核设计技术主要采用标准研制流程,根据标准的总线接口形式,开发弹载信号预处理专用算法IP核。航天应用IP设计的基本流程,如图4所示。

图4 航天应用IP设计的基本流程

图4中定义关键特性是指对IP的需求定义,弹载高速实时信息处理SoC专用IP研制涉及核心处理器IP、外设IP、存储器IP等资源,需要确保专用算法IP与外购IP之间的良好兼容性;规划和制定设计规范包含功能设计规范、验证规范、封装规范、开发计划,指导整个IP研制流程;模块设计与集成针对软核和硬核分别采用RTL级和专用设计以建立整体RTL模型,弹载信息处理专用算法IP核一般以软核、固核形式提供,并且嵌入至SoC芯片原型FPGA代码中进行功能性能的仿真、验证;弹载高速实时信息处理SoC设计通过开放IP标准接口、规范等,构建航天标准IP库,实现IP核产品化和IP核入库。

3.3 可测试性设计技术

根据芯片完成后的测试需求,针对不同的模块电路设计不同的测试单元,以便芯片流片后具备测试内部模块功能的能力。当前IC设计的趋势是基于IP复用的SoC技术,弹载高速实时信息处理SoC系统中包含了多核处理器IP、存储器IP、各类接口IP等模块。可测性设计针对SoC设计流程和系统级DFT的特点,其设计流程如图5所示。

图5 测试流程设计

此外,在数字电路测试中,用于存储器测试的存储器内建自测(BIST,Built-In-Self-Test),用于组合逻辑测试的扫描测试和用于板级连接测试的边界扫描测试等测试技术中,存储器内建自测集中于低功耗技术和在其它模块测试中的适用性;扫描测试技术侧重在满足测试要求同时减小测试时间和功耗、测试电路时序、向量压缩等;采用边界扫描测试,降低测试所需时间,此外采用各种EDA工具进行综合测试。

4 功能模型搭建

4.1 系统构架

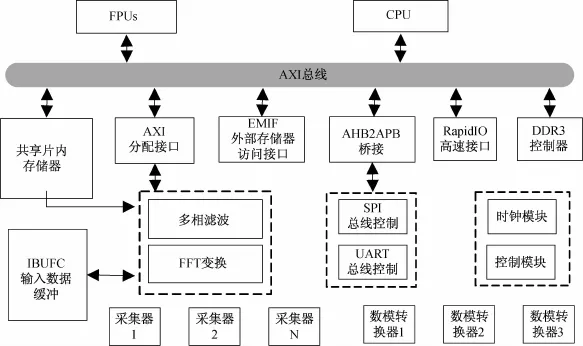

弹载高速实时信息处理SoC系统采用CPU作为主控核心,负责整个系统资源调度;以DSP作为核心数据处理器,主要实现弹载系统复杂算法;专用算法单元作为预处理加速器,用于实现由回波接收到完成预处理的全部流程;此外,还包含共享外设作为SoC的对外接口,分为慢速接口与快速接口,分别实现与慢速设备的信息交互及大规模的数据传输。弹载高速实时信息处理SoC系统总体架构如图6所示。

图6所示弹载高速实时信息处理SoC系统主核及外设接口部分配置如下:

图6 系统总体架构

(1)系统主核

可分为以下五部分:

a)MINI-ARM:系统主核,32-bit RISC CPU,兼容ARM 920程序;

b)处理器:高性能浮点FPU*4,每个2GFLOPS,65 nm工艺;

c)总线结构:AHB总线及APB总线控制单元,单总线结构;

d)共享存储空间:16*2*32kB片上Embedded SRAM;

e)控制器:DMA控制器、中断控制器等。

(2)I/O接口及常用外设

可分为以下七部分:

a)EMIF并行传输接口;

b)RapidIO快速串行接口;

c)SPI模块(含主从模式);

d)GPIO可复用;

e)UART控制器;

f)其它配合高速ADC/DAC的数据传输与各类驱动I/O管理、控制时序逻辑生成集成接口;

g)高速DDR3存储器等。

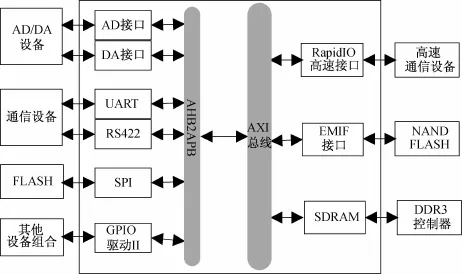

4.2 互联技术

弹载高速实时信息处理SoC系统包含丰富的接口资源,包含并行处理接口EMIF,高速串行接口RapidIO等,以及SPI、UART等慢速接口,弹载高速实时信息处理SoC系统设计总线架构下挂于AHB、APB的主要外设承担与外部系统芯片、电路通信的任务。系统所有接口及其与外设连接,如图7所示。

由图7可知,挂于AHB、APB总线的设备中AD/DA接口主要用于模拟信号采集和数字信号输出,经系统总体论证,总带宽不小于Gbps。UART接口用于低速率、小批量数据传输或多处理器间控制信息的传输;GPIO接口用于多处理器间的控制信息传输、多处理器间的任务同步等。GPIO接口包含较为丰富的资源,一部分用于驱动接收机、伺服机构等,另一部分用于其他组合的驱动。

图7 系统总体互联关系

除挂于AHB、APB总线的接口,系统还包含高速接口设备,Rapid IO接口用于海量数据搬移,为达到稳定传输,1ⅩRapidIO速率可达2.5 Gbps,4ⅩRapidIO可实现10 Gbps的数据交换;EMIF外设访问接口包含丰富并行资源,采用64根并行数据线,可实现达800 MBps的数据传输,该接口可同时用于SoC启动程序加载,接口具备复用功能;SoC可以通过SDRAM接口与片外大容量存储设备进行高速数据读写操作,可支持大1 600 Mbps的数据读写操作。

4.3 专用算法

弹载信号处理系统中典型信号处理包含回波采集、下变频预处理、脉冲压缩以及回波数据处理等,弹载高速实时信息处理SoC系统设计采用标准IP核设计技术,针对上述信号处理模块自主形成专用航天标准IP核,根据SoC总体设计,主要IP核包含以下四种:

(1)通用数字下变频IP

具备多路采样数据并行数字下变频处理能力,下变频速率不低于百兆赫兹,同时支持通过数据缓冲实现不同速率的下变频。

(2)参数可配置滤波器IP

可实现通用参数可配置低通、带通滤波器算法,滤波速率可通过数据缓冲单元调节,滤波参数写入专用存储器单元中。

(3)可变点FFT处理IP

具备FFT的点数可设置,最长支持32 K点的FFT;具备两个以上可变点数FFT算法模块;FFT数据可通过DMA或存储器共享方式发送至处理系统。

(4)其他标准IP核

根据不同导引头工作体制,包含AGC控制、信号化处理等专用IP核等。

弹载信号处理SoC系统设计从总体方案、接口互联以及标准IP设计等方面,均借鉴了当前成熟设计并在试验中取得成功应用的FPGA和DSP的设计架构,既能保证设计成功性,又保证自主研制能力。

5 结论

面向复合导引头信号处理应用的SoC系统可以实现导引头常规信号处理功能,具备当前高速接口的传输能力,保留常规低速接口的功能,并通过设计标准化IP核,保证算法设计的通用性。面向复合导引头信号处理应用的SoC设计具备可行性和工程实用性,同时对我国自主保障、技术革新具有重大的战略意义。

[1] M.Keating,P.Bricaud.Reuse Methodology Manual for System-on-a-Chip Designs,3rd Edition[M]. Kluwer Academic Publishers,2002.

[2] 彭澄廉.挑战SoC:基于NIOS的SOPC设计与实践[M].北京:清华大学出版社,2004.

[3] 王海力,边计年,吴强,等.SoC系统级设计方法与技术[J].计算机辅助设计与图形学学报,2006,18(11):1637-1644.

[4] 段承超.SoC/IP验证平台的研究与实现[D].郑州:解放军信息工程大学,2011.

[5] 马国俊.SoC技术及设计方法研究[D].自动化与仪器仪表,2012,(1):6.

[6] 白静,谢憬.基于ARM嵌入式平台的Ⅹ86译码SoC架构设计[J].现代电子技术,2009,(8):295.

The Design of SoC for the Signal Processing Implementation of Composite Seeker

GAO Wei1, ZHENG Xin2, WANG Feng-jiao3

(1.Naval Armaments Department,Beijing 100841;2.Shanghai Academy of Spaceflight Technology,Shanghai 201109;3.Shanghai Radio Equipment Research Institute,Shanghai 200090,China)

SoC technology has its own advantages in the field of tactical weapons.With the increasingly run up voice of independent research of key electric components,it is extremely exigent to breach the key technologies of SoC which are used in tactical weapons and develop high performance SoC chip which is satisfied.The conception and key technologies of SoC would be introduced,then the general requirements of some composite seeker signal processing platform would be analyzed.In the final,a design scheme of SoC implement which contains AHB bus architecture,32 bits RISC-CPU,and IP core of professional arithmetic would be put frward.

seeker;signal processing;design proposal

TJ957.52

A

1671-0576(2014)03-0021-06

2014-08-01

高 维(1971-),男,工程师,主要从事装备管理;郑 鑫(1980-),男,高工,主要从事导弹预研项目管理;王凤姣(1989 -),女,硕士,主要从事雷达信号处理技术研究。

——信号处理