基于LEON3的SoC平台构建及UART全双工通信验证

段大高,王平丽

(北京工商大学,计算机与信息工程学院,北京 100048)

基于LEON3的SoC平台构建及UART全双工通信验证

段大高,王平丽

(北京工商大学,计算机与信息工程学院,北京 100048)

LEON3是一个可配置、可移植、高性能和开源的软核处理器,在工业领域和空间应用中得到广泛研究。论文基于LEON3软核构建了一种高性能、灵活的SoC硬件平台,并设计了UART全双工通信功能。首先介绍了 LEON3开发环境硬件平台的搭建,并通过tsim-leon3模拟器,验证了LEON3 SoC的基本功能;其次研究LEON3的UART通信功能,并在LEON3 SoC硬件平台上进行了UART全双工通信实现。结果验证了基于LEON3的SoC平台的可行性,并实现了SoC的UART全双工通信功能,为SoC的开发提供一个良好的参考方案。

LEON3;UART;tsim-leon3;SoC

0 引言

随着芯片设计技术的飞速发展,SoC已成为集成电路设计界的焦点,SoC的性能要求越来越高,规模也越来越大。LEON系列微处理器是欧洲航天局(ESA)下属研究机构 Gaisler Research公司所开发和维护的,LEON3处理器是基于SPARC V8架构的32位精简指令集计算机微处理器,目的是摆脱对美国航空局的依赖,LEON3是一个可配置的、可移植的、高性能的、高可靠的软核处理器[1]。它的源码是可综合的VHDL代码,并且是开源的,任何人都可以在其网站上免费下载其硬件代码和各种开发软件工具与文档。由于LEON3具有良好的可移植性、可配置性和遵循GPL许可协议的开源性,这些特性保证系统SoC芯片的安全性,提供良好的性能和灵活的解决方案[2],也决定了在LEON3上进行嵌入式操作系统移植的特殊性,所以很适合SoC平台开发[3~5]。本文为基于LEON3的SoC平台设计提供一个良好的参考方案。

1 基于LEON3的SoC平台搭建

1.1 基于LEON3的SoC平台系统框架的设计

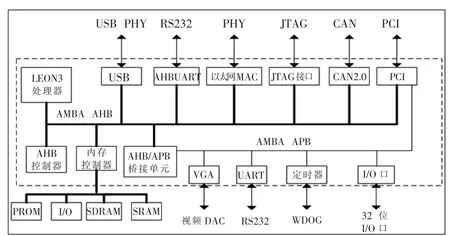

LEON3系统是基于AMBA AHB和APB总线设计的[6],系统所有模块都通过AMBA总线连接,LEON3处理器和其他高宽带设备都连接在AMBA AHB总线上,如:AHB控制器、内存控制器、JTAG接口、USB接口等,其他低速外设设备连接在 AMBA APB总线上,如:VGA、定时器、串口、I/O口等。系统框图如图1所示。

1.2 搭建LEON3研发环境

(1)软件条件。在Win7系统上安装虚拟机VMwareWorkstation 10.0,在虚拟机上安装Linux系统:Ubuntu10.10,在Linux环境下进行硬件配置。安装grmon-eval,用于下载bit文件,查看硬件地址信息等。

(2)硬件条件。本文使用开发板Xilinx公司的spartan3e xc3s1600e。它包含了丰富的,灵活的逻辑资源,包含一个xc3s1600e FPGA芯片,逻辑单元33192,IEEE 1149.1/ 1532 JTAG编程/调试端口等逻辑资源。

(3)tsim-leon3验证。TSIM是SPARC架构处理器通用软件仿真器[7],用于软件仿真ERC32和LEON处理器。它作为软件模拟的VHDL模型,调试过程中需要启动一些常见的选项进行设置,如:-freq。使用tsim-leon3对Hello World程序进行测试,进而验证LEON3研发环境成功搭建,为下一步硬件平台环境搭建建立基础。

图1 系统框图Fig.1 System block diagram

1.3 基于LEON3的硬件平台搭建

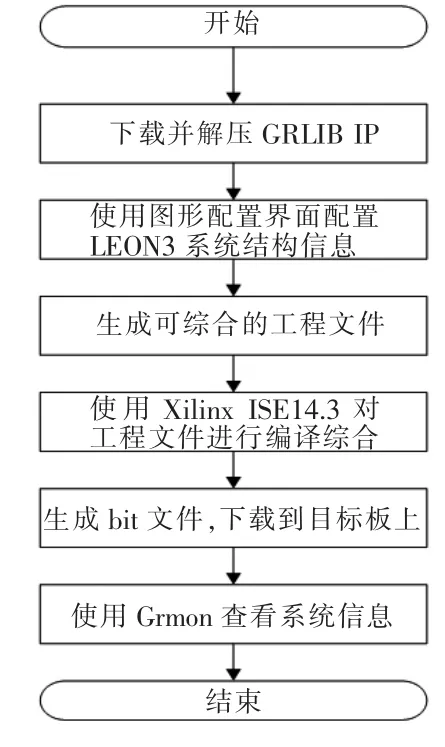

本文是使用Xilinx公司的spartan3e系列的xc3s1600e作为LEON3处理器系统的载体,在配置好硬件平台开发环境以后,接下来进行硬件平台的搭建,搭建流程如图2所示。

图2 硬件平台搭建流程Fig.2 Procedure of designing hardware platform

由于前期阶段已经下载安装了GRLIB IP库,即LEON3源代码,在Linux环境下,找到目标板的文件目录,使用make xconfig命令对各个硬件模块进行配置,利用图形配置界面配置各个模块,配置信息将保存在config.vhd中。

使用make ise命令建立工程文件,使用 Xilinx ISE14.3编译整个工程文件,生成 bit文件,最后将bit文件下载到FPGA开发板上。

打开grmon-eval,使用info sys命令[8],查看LEON3内核硬件地址信息,可以看出内核的处理器是Gaisler Research LEON3 SPARC V8 Processor,APB UART的基地址是0x80000100,从而可知LEON3硬件平台搭建成功。

2 基于LEON3的UART全双工通信验证

2.1 APB UART的结构

APB UART主要包括接收模块、发送模块、波特率产生模块和串口控制器等4个部分。APB UART为串行通信提供接口,该UART支持带8个数据位,一个可选的奇偶校验位和1个停止位的数据帧。为产生波特率,每个UART具有一个可编程的12位时钟分频器。当fifosize>1时,两个FIFO用于APB总线和UART之间的数据传输。当 fifosize=1时,两个保持寄存器用于APB总线和UART之间的数据传输。当VHDL的参数声明(flow)里设置流控制时,通过RTSN/CTSN握手信号支持硬件流控制。当VHDL参数声明(parity)里设置奇偶校验位时,支持奇偶校验。APB UART模块的工作模式包括:发送模式、接收模式、波特率生成、回环模式、FIFO调试模式、中断产生模式。通过选择不同的工作模式,对寄存器选择不同的操作和控制。

2.2 APB UART的帧格式和寄存器

UART无奇偶校验位的帧格式包括线路空闲状态(idle,高电平)、起始位(start bit,低电平)、8位数据位(data bits)和停止位(stop bit)。

通过寄存器映射到 APB地址空间来控制 IP核。APB UART的相关寄存器的地址偏移量如表1所示。

(1)UART数据寄存器:数据寄存器有32位,只有低7位有效,在发送模式下,存储的是要发送的数据,在接收模式下,存储的是接收到的数据。

表1 APBUART的寄存器Tab.1 APBUART registers

(2)UART状态寄存器:状态寄存器中的各位数据表明现在UART的状态,比较典型的位有:10:RF表示接受FIFO满;9:TF表示发送FIFO满;8:RH表示接收FIFO中至少有一半的数据;7:TH表示发送FIFO中的数据少于一半;6:FE表示检测到帧错误;5:PE表示检测到奇偶校验位错误;4:OV表示由于溢出丢失了一个或多个数据;2:TE表示发送FIFO空;1:TS表示数据移位寄存器为空;0:DR数据准备,表示可以在FIFO中获得新数据。

(3)UART控制寄存器:UART控制寄存器是一组可以对UART进行操作控制的寄存器,使其工作在不同的工作模式下,其中比较典型的位如下:7:LB置位时,UART工作在回环模式;6:FL置位时,用CTS/RTS使能流控制;5:PE置位时,奇偶校验使能;4:PS选择奇偶校验的种类,1是奇校验,0是偶校验;3:TI置位时,当发送一个数据帧时产生一个中断;2:RI置位时,当接收扫一个数据帧时产生一个中断;1:TE使能发送数据;0:RE使能接收数据。

(4)UART计数寄存器:根据UART计数寄存器的值可以计算UART的波特率。

2.3 UART全双工通信程序

(1)UART的寄存器硬件地址映射。

#define UART_BASE 0x80000100

#defineUART_RX_FIFO *(volatileunsignedint*)(UART_BASE)

#define UART_TX_FIFO*(volatile unsigned int*)(UART_BASE)

#defineUART_STATE*(volatileunsignedint*)(UART_BASE+0x04)

#define UART_CON*(volatile unsigned int*)(UART_BASE+0x08)

#defineUART_SCALE*(volatileunsignedint*)(UART_BASE+0x0c)

以上代码是对UART的相关寄存器进行物理映射,UART的基地址是0x80000100,这是APB总线的地址段,以这个地址段开头向后偏移相应的偏移地址得到相应寄存器的地址。这和寄存器中相应的地址是对应的,所以对相对应的物理地址进行读写操作,可以对应的对寄存器进行读写操作。

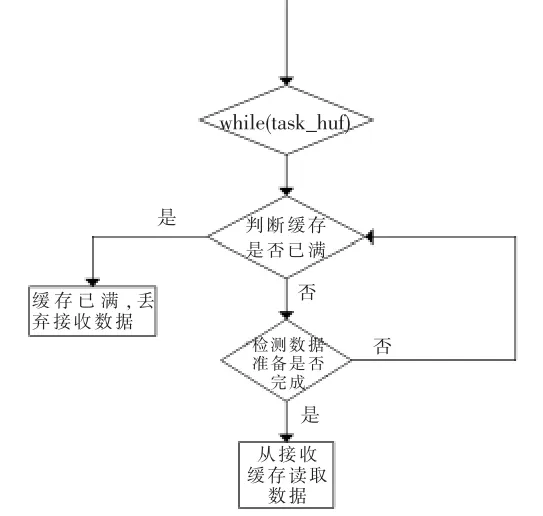

(2)程序流程图。UART接收过程中,task_buf记录有效数据量,由于FIFO深度为8字节,故接收的有效数据量不应大于8字节,接收程序流程如图3所示。

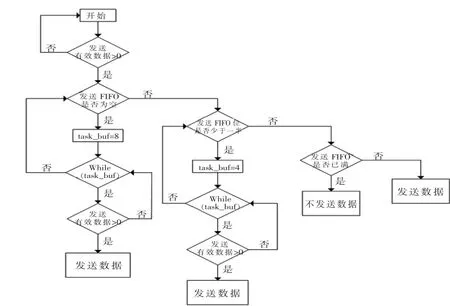

发送过程分三种情况:当发送FIFO为空时,最多发送8个字节数据;当发送FIFO少于一半时,最多发送4个字节数据;当发送FIFO满时,不发送数据。发送过程流程图如图4所示。

(3)测试结果。UART全双工通信功能验证:在Windows平台下编写串口通信程序,测试程序编写完成,使用sparc-elf-gcc编译器编译C程序生成可执行文件。再使用grmon-eval下载到目标板上,使用 run命令,运行程序,使用串口调试助手进行观测,本测试中选择的是无奇偶校验位的数据帧格式,通信双方采用相同的波特率9600bps,上位机打开一个串口调试助手,通过USB转的串口6与串口调试助手相连接,准备一系列字节用于发送数据,下位机运行时,可以通过连接串口6的调试助手看到不断的收到所发数据,测试结果如图5所示。对比发送和接收的数据,发现二者是一致的,也无错误发生,测试结果可以看出,该测试程序完成了UART全双工的通信,从而也可以验证UART的接收功能和发送功能。

图3 接收程序流程图Fig.3 The receiving program flow diagram

图4 发送过程流程图Fig.4 The transmitting program flow diagram

3 总结

本文利用LEON3软核处理器的可配置、可综合、 可移植等性质, 构建了一基于LEON3的 SoC硬件平台,并且通过UART全双工通信,验证了平台的搭建成功,同时验证了基于LEON3软核的UART全双工通信的可行性,为以后LEON3 SoC的开发提供一个良好的参考方案。

图5 测试结果Fig.5 Test results

[1]Gaisler A.LEON/GRLIB Configuration and Development Guide[Z]. Aeroflex Gaisler,2012.

[2]李林,张晓林,杨希.基于 LEON开源软核的 SoC平台构建与测试[J].单片机与嵌入式系统应用,2007,1.

[3]Zhonghua Z,Wuchen W,Ming H,et al.A SoPC design based on LEON3 SoC platform[A].Microelectronics&Electronics,2009.PrimeAsia 2009. AsiaPacificConferenceonPostgraduateResearchinIEEE[C].2009.

[4]Pei L,Jian Z.A high reliable SOC on-board computer based on LEON3[A].Computer Science and Automation Engineering(CSAE), 2012 IEEE International Conference on.IEEE[C].2012.

[5]Muñoz A,Ostua E,Bellido M J,et al.Building a SoC for industrial applications based on LEON microprocessor and a GNU/Linux distribution[A].Industrial Electronics,2008.ISIE 2008.IEEE International Symposium on.IEEE[C].2008.

[6]Gaisler A.GRLIB IP Core User's Manual,Version 1.2.2 B4123[Z]. Aeroflex Gaisler:January 2013.

[7]Gaisler A.TSIM2 Simulator User's Manual Version2.0.23[Z].Aeroflex Gaisler AB:October 2012.

[8]Gaisler A.GRMON User's Manual Version 1.1.56[Z].Aeroflex Gaisler AB:December 2012.

SoC Platform and UART Full-duplex Communication Verification Based on LEON3

DUAN Da-Gao,WANG Ping-Li

(College of Computer and Information Engineering,Beijing Technology and Business University,Beijing 100048,China)

LEON3 is a configurable,portable,high-performance and open source soft-core processor,which has been widely used in the field of industrial and space applications.In this paper,we built a high-performance,flexible SoC hardware platform based on LEON3 softcore,and designed?the function of UART full-duplex communication.Firstly,the build of the hardware platform of LEON3 development environment is introduced,and the basic function of LEON3 SoC is verified through tsim-leon3 simulator.Secondly,the communication of SoC UART is proposed and the UART full-duplex function is implemented on LEON3 SoC hardware platform.The experimental results show that the high-performance LEON3 SoC platform is achieved.A good reference solution for the development of SoC is provided.

LEON3;UART;tsim-leon3;SoC

TP39

:Adoi:10.3969/j.issn.1002-6673.2014.03.045

1002-6673(2014)03-115-03

2014-03-12

段大高 (1976-),男,博士,副教授。主要研究方向:多媒体信息处理、现代网络通信、嵌入式系统、智能数据分析等;王平丽 (1988-),女,硕士研究生。主要研究方向:嵌入式系统开发、多媒体信息处理等。