频率量转换数字量的集成电路设计技术

周 霁

(中国电子科技集团公司第四十七研究所,沈阳110032)

频率量转换数字量的集成电路设计技术

周 霁

(中国电子科技集团公司第四十七研究所,沈阳110032)

传感器在各领域有着广泛应用,为了测试传感器输出的频率值,在传感器与计算机之间需要一种可以将频率量转换为数字量的专用集成电路。介绍了输出为频率量的传感器测试基本原理,设计了基于这种传感器而研制的专用集成电路,介绍了其电路功能,电路逻辑结构,电路核心器件逻辑设计及功能验证。

频率量;数字量;专用集成电路

1 引 言

传感器广泛应用于我们生活的各个领域,传感器的信号输出有的是频率量,但终端计算机只能接收数字量,因此在传感器和计算机之间,必须有一个可以将频率量转换为数字量的专用接口电路。对于模拟量,目前采用不同精度的A/D和V/F通用接口芯片,对于频率量,目前专用的F/D芯片比较少,设计这种专用集成电路,在数据采集和控制系统方面应用较多。

2 测试原理及电路功能介绍

2.1 一般测量原理

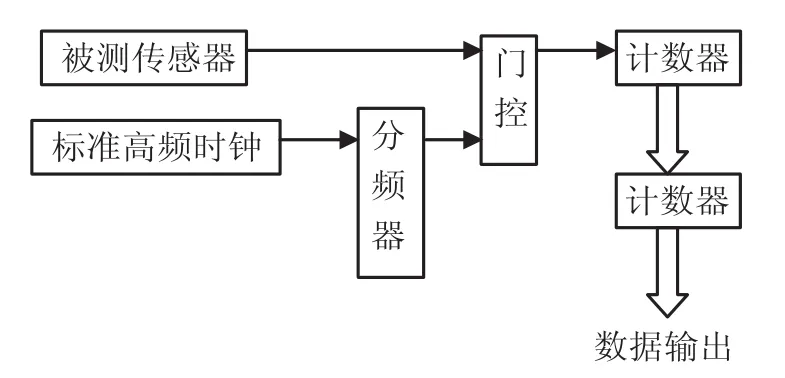

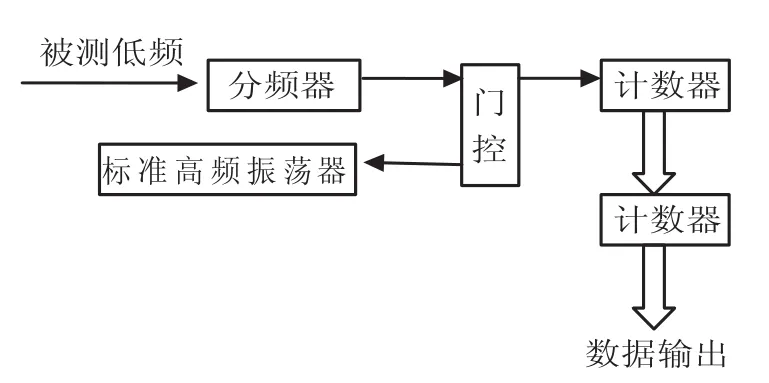

对于频率量的测量一般分为两种:一种是测频法,另一种是测周法。这两种方法适用于不同的场合和用途。为了提高测量精度,输出频率较高的传感器绝大部分采用的是测频法,而输出频率较低的传感器绝大部分采用的是测周法,测频法的一般原理图如图1所示,测周法原理图如图2所示。

图1 测频法原理图

图2 测周法原理图

2.2 电路功能

此电路根据测周法原理而设计,电路输入为低频信号,利用标准高频时钟确定采样周期,电路将频率信号利用计数器转换为数字信号通过总线输出。

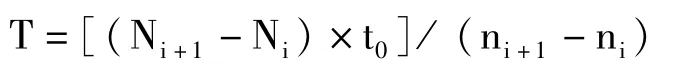

其中:

Ni:第i次采样周期高频计数器;Ni+1:第i+1次采样周期高频计数器

ni:第i次采样周期低频计数器;ni+1:第i+1次采样周期低频计数器

t0:标准高频脉冲周期值

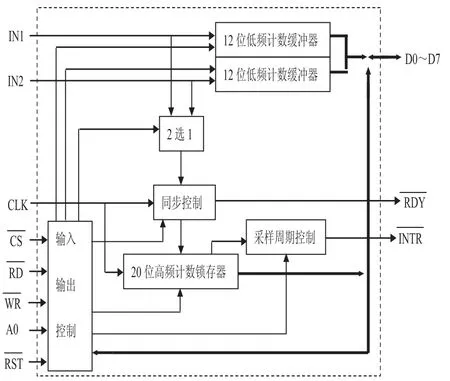

根据实际使用要求,设计电路逻辑和对应的输入输出电路的逻辑功能图如图3所示。主要由输入/输出缓冲器,输入2选1开关,输入输出控制电路,同步控制电路,两路12位低频计数缓冲器,20位高频计数锁存器及采样周期控制电路等部分组成,另外出于性能考虑,会额外加入一些输入/输出驱动电路、保护电路和三态电路等。

其中输入输出说明如下:

IN1,IN2为两路低频信号输入端,在设计时,可以扩展成多种,相应的要增加选择开关;CLK为高频时钟信号;CS片选信号:低电平有效;RD读信号控制,低电平有效;WR写信号控制,低电平有效;A0:控制字和地址码写入控制端,写信号时为高电平,读信号时为低电平;RST复位信号,可以将低频计数器清零;INTR:中断信号输出端,当时钟信号到达,高频低16位计数器记满时跳变;RDY数据准备好信号输出端,读出数据有效标志;D0~D7为双向总线,D7为最高位,D0为最低位。

图3 电路的逻辑功能图

3 电路核心器件逻辑设计

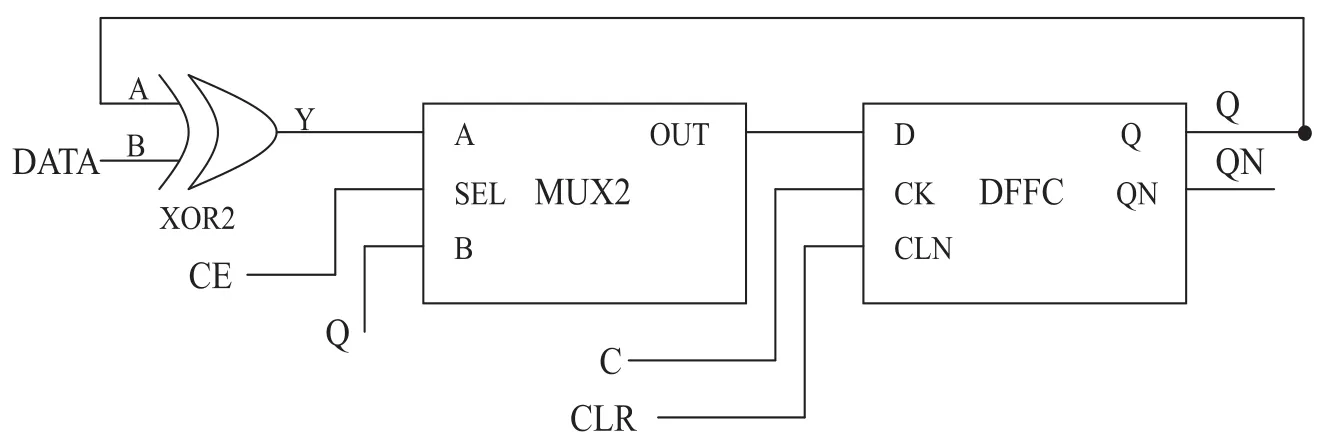

电路核心部件为分频器,分频器由单个的计数器基本计算单元组成,逻辑结构如图4所示。

图4 分频器基本计算电路

计数器基本计算单元电路结构说明:由一个异或单元XOR2,一全二选一单元MUX2,,一个触发器单元DFFC组成。在异或单元XOR2中,A,B为数据输入端,Y为数据输出端。当A=B时,Y=0;A≠B时,Y=1;在触发器单元DFFC中,D为数据输入端,CK为时钟端,CLN为清零端,Q,QN为数据输出端。当CLR=0,即CLN=0时,Q=0,QN=1;当CLR=1,即CLN=1时,每来一个C的上升沿,即CK的上升沿,Q=D,QN=!D。Q及QN随着CK时钟频率变化,CK是上升沿有效,这决定了整个计数器也是上升沿进行数据计算的。在设计计数器时,注意时钟是哪一种沿有效。这种结构是比较经典的计数器计算单元,也是各种其它计数器的基础,在电路中应用相当广泛,许多其它的计数器单元,都是在这种基本结构上发展而来的,在原理上也与这种最基本的结构相同。掌握了这种结构的原理,对于设计其它结构的计数器有很大的帮助。

计数器基本计算单元工作原理:CE为计数器使能控制端,多个基本计算单元组合在一起形成多位计数器时,这些基本计算单元的CE是连接在一起的;DATA端为数据输入端,接收的是低位数据输出,如果作为第一位使用时,可以直接接电源,使DATA=1。多个基本计算单元组合在一起形成多位计数器时,需要低位基本计算单元的输出结果Q,QN通过一个二选一结构后,向高位的基本计算单元DATA端输出,就形成了低位数据与高位数据连接电路。T=[(Ni+1-Ni)×t0]/(ni+1-ni)公式表明,只要两次同时对高低频率数进行采样,并求出其增量,就可以求出低频的周期值,以实现对传感器输出频率的测量。

4 功能验证

电路逻辑形成后,需要通过仿真对电路功能进行验证。不但要使逻辑电路内的所有节点都发生翻转,更重要的是使逻辑电路的功能全覆盖。使用的仿真工具为verilog_xl。在实际仿真过程中,由于单个逻辑器件输入到输出为理想无时间延迟状态,虽然预先对触发器进行了置位,但触发器进行分频时,输出仍会出现不定态,导致电路最后的输出Q也是不定态。例如用更基本单元倒向器,对管传输门搭建DFFC触发器,在仿真时在输出端会产生不定态。不定态的原因是因为理想器件没有延时造成的。

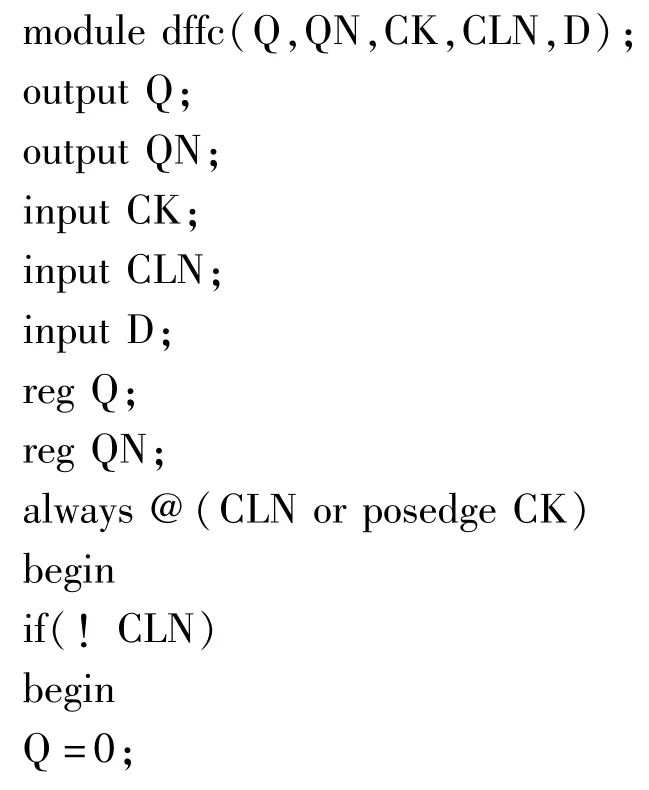

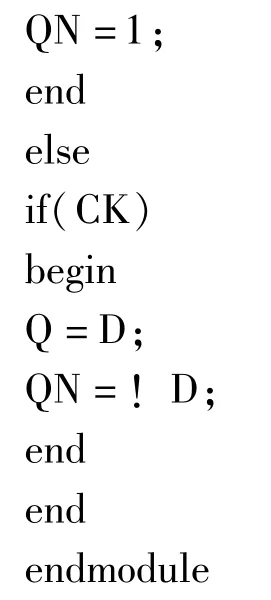

解决方法:在触发器内部的寄存器环型反馈结构中加上对地电容,这样会使高低电平转换时电平有一个维持时间,从而消除不定态。另外可以在触发器内部的寄存器环型反馈结构中加上一个延迟器件,使反馈环结构中输出到输入有一个时间上的延迟,就可以消除不定态。或对触发器功能进行verilog语言描述,从而避免仿真过程中不定态的产生。以dffc触发器结构为例,对其进行verilog语言描述如下:

这种功能描述覆盖了这种触发器电路输入可能出现的所有情况。在设计这种电路的过程中,要注意时钟有效沿的类型。对于电路的逻辑验证,在电路内部转换较为复杂的有进位的运算状态下,注意将电路的功能验证完全。

5 结束语

此类电路是为输出频率信号的传感器(谐振筒压力传感器、超声波风速传感器等)的测试和系统控制而设计,主要用于测试这类传感器的输出频率值,可以广泛应用于航空仪器、仪表数据采集和控制系统等领域。电路可以同时完成两路频率信号的数字转换,分辩率最低为十万分之一,最高为百万分之一,采样时间为ms级。(一般对应2μmCMOS工艺),在使用时应按使用要求进行控制程序的编程,来实现相应的电路功能。使用时,应对电源滤波,一般应先加电源后,再加入输入信号。

[1]王永军,李景华.数字逻辑与数字系统[M].北京:电子工业出版社,2005.

[2]R.Jacob Baker,Harry W.Li,David E Boyce.CMOS电路设计、布局与仿真[M].北京:机械工业出版社,2006.

[3]张明.Verilog HDL实用教程[M].成都:电子科技大学出版社,1999.

Integrate Circuit Design Technology of Frequency Transferred to Date

ZHOU Ji

(The 47th Research Institute of China Electronics Technology Group Corporation,Shenyang 110032,China)

Sensors are widely used in many fields.In order to test the output frequency of the sensor,between the sensor and the computer,the specific integrated circuit is necessary for transferring the frequency to data.This paper introduces the test principle of the sensor,designs the specific integrated circuit,and expatiates its function,logic structure,key components and function test.

Frequency;Data;Application Specific Integrated Circuit

10.3969/j.issn.1002-2279.2014.01.004

TN4

:A

:1002-2279(2014)01-0012-03

周霁(1982-),女,辽宁省沈阳市人,学士,工程师,主研方向:集成电路设计及验证。

2013-02-21