FT1500处理器中仿真驱动的DDR3封装设计*

黎铁军,孙 岩,邹 京,张秀峰

(国防科学技术大学计算机学院,湖南 长沙 410073)

1 引言

随着集成电路技术的发展,多核多线程持续为通用微处理器带来更高性能,但访存带宽和延迟性能提高缓慢,这导致了存储墙问题。DDR3作为典型并行总线结构被广泛应用于内存总线设计中,以提高访存带宽和降低访存延迟,但并行总线的电源完整性和信号完整性问题突出[1,2],而且随着传输速率的不断提高,这些问题成为限制传输速率进一步提高的瓶颈。

FT1500是一款面向高性能计算的通用微处理器,该处理器采用16核64线程结构,设计主频1.5GHz,峰值性能120GFlops,通过四个72位DDR3存储控制器访问片外存储器,DDR3设计速率1 333Mbps。本文重点研究FT1500芯片高速DDR3封装设计,解决高频情况下的电源完整性和信号完整性问题。

针对DDR3的封装设计问题,本文提出了仿真驱动的封装设计方法,在设计之初通过前仿真制定准确的设计规则和目标,在设计过程中通过仿真驱动设计优化,在设计完成后用后仿真验证设计。实测结果表明,FT1500芯片的DDR3接口可以稳定工作在1 400Mbps,达到了设计目标。

2 仿真驱动的封装设计

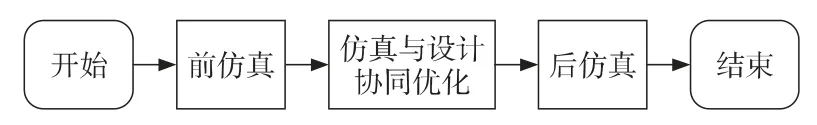

本文提出的仿真驱动的封装设计流程如图1所示。

仿真驱动的封装设计流程包含三个主要步骤:

前仿真:确定I/O及关键电源网络的目标电感与目标电阻,确定高速信号的走线宽度与线间距,验证仿真模型的准确性。

Figure 1 Full flow of package and PCB simulation图1 完整的封装与PCB仿真流程

设计与仿真协调优化:在封装与PCB设计中并行地进行PI仿真,提前找出设计存在的问题,指导设计者进行优化,PI与封装设计联合仿真包含数次迭代设计与仿真,直到达到设计目标。

后仿真:在设计投出生产前的一次完整的SI/PI仿真,确保设计能达到最终的目标。

3 封装的前仿真

3.1 DDR3信号目标阻抗确认

首先通过仿真对走线阻抗进行求解。求解时要根据走线的具体情况选择正确的传输线模型,对于表层走线还需要考虑表层绿油的影响。对于DDR3数据地址等单线阻抗要求为42.5Ω,由仿真求得对应内层走线的宽度应当为30μm,而表层走线宽度应当为60μm。表层比内层缺少一层参考平面,同等线宽下表层单线阻抗过高,为了方便阻抗控制,应当尽量避免在表层走高速信号线。

3.2 DDR3I/O仿真模型验证

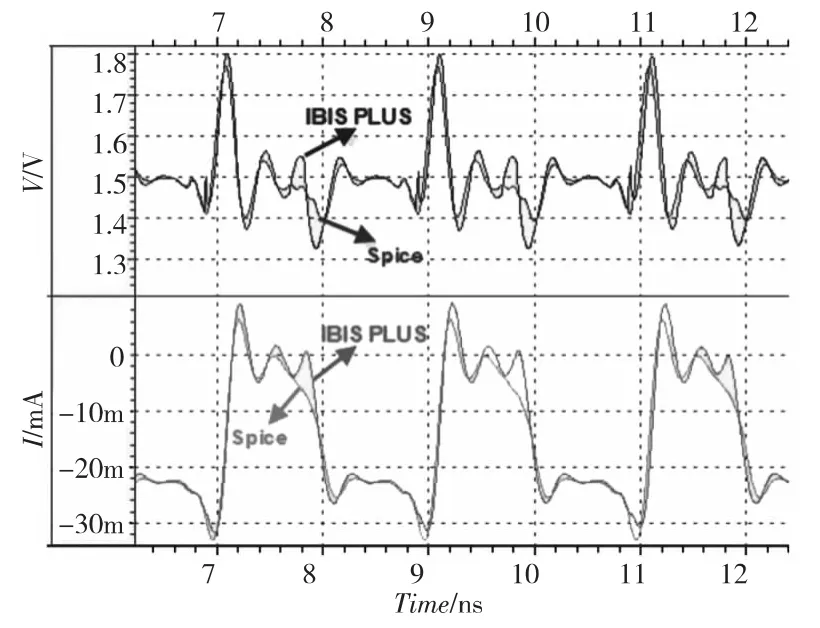

由于SPICE模型的仿真速度慢,需要将DDR I/O的SPICE网表转换成IBIS Plus模型[3]。在使用IBIS Plus模型进行仿真之前需要综合评估一下该模型的仿真精度。

首先验证IBIS Plus模型电源建模的准确性,将DDR3I/O的SPICE模型和IBIS Plus模型加入到SPICE测试网表中,I/O的输出阻抗设为40Ω,在I/O的电源上增加一个RLC子电路作为I/O电源的寄生参数,I/O的输出接一个40Ω的电阻。为两种模型加入相同的激励,仿真得到两种模型电源管脚的电压和电流波形如图2所示。由图2可以看出,IBIS Plus模型的电压电流波形与SPICE模型基本吻合,说明IBIS Plus模型电源建模比较精确。

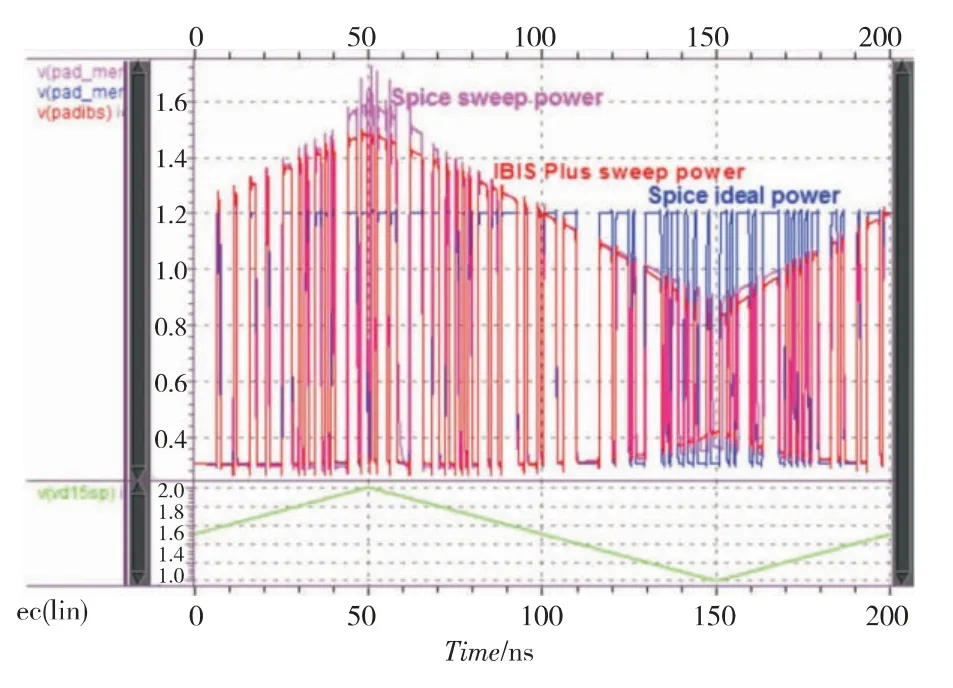

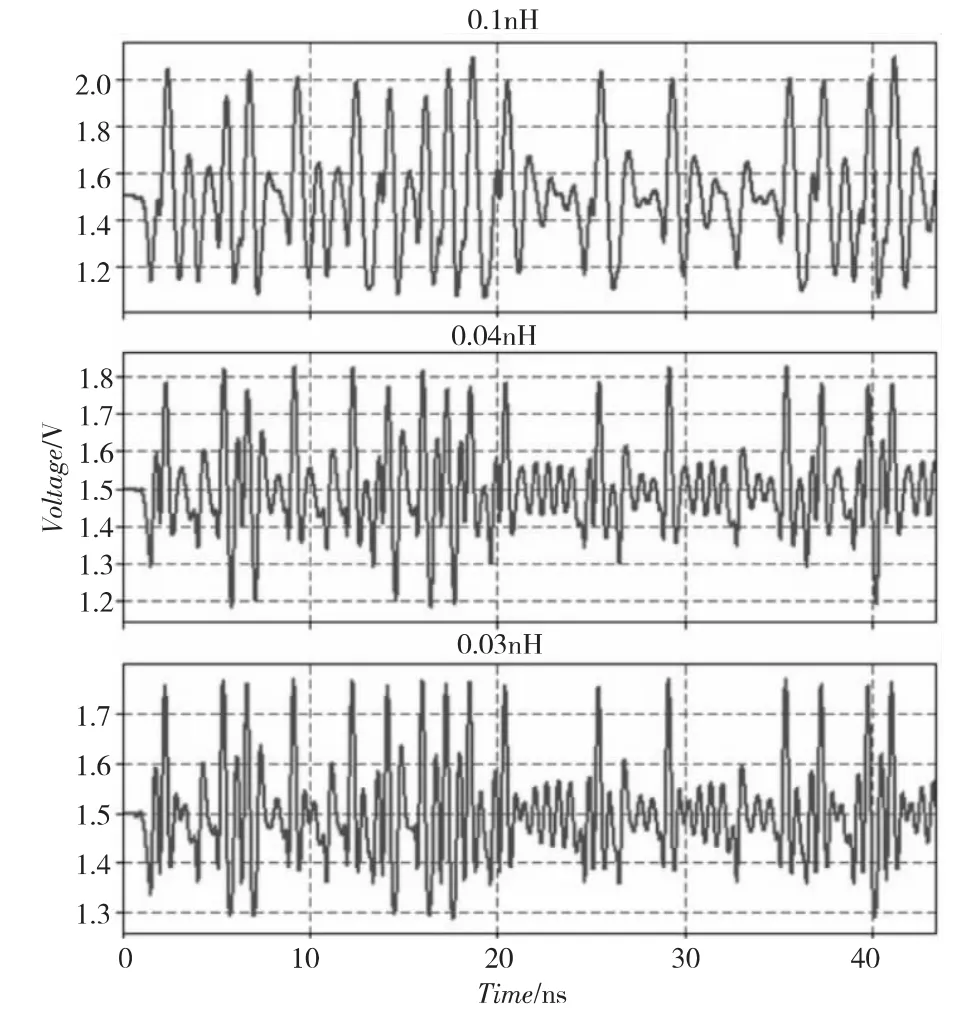

实际I/O电源电压可能会受SSN的影响不停波动,需要分析两种模型在不同电源电压下的输出情况。同理还是编写一个SPICE测试网表将两种模型I/O加入,两种I/O的电源都从1.0V线性变化到2.0V,为了方便对比,另加入一个正常供电的SPICE模型的I/O,三个I/O都加入相同的激励,仿真结果如图3所示。

Figure 2 Simulation results of IBIS plus power modeling图2 IBIS Plus电源建模仿真结果

由图3可以看出,在I/O正常工作电压1.5V附近,IBIS Plus模型的输出与SPICE模型输出幅度相位基本一致。当电源电压高于1.8V或者低于1.2V时,IBIS Plus模型输出与SPICE模型的输出误差较大。假设DDR3工作在1.5V左右,因此本文仿真均使用IBIS Plus模型。

Figure 3 Simulation results of IBIS plus output图3 IBIS Plus输出仿真结果

3.3 DDR3I/O电源目标电感确认

由图3可知,当I/O Buffer的电源电压大于1.8V或者小于1.2V时,I/O Buffer的输出延时会发生较大的变化,延时的变化会对信号的时序造成严重的影响。为了保证I/O Buffer正常工作,必须保证I/O Buffer的电源电压在正常范围1.2V~1.8V内波动,本文利用这一条件确定DDR3I/O的目标电感[4]。

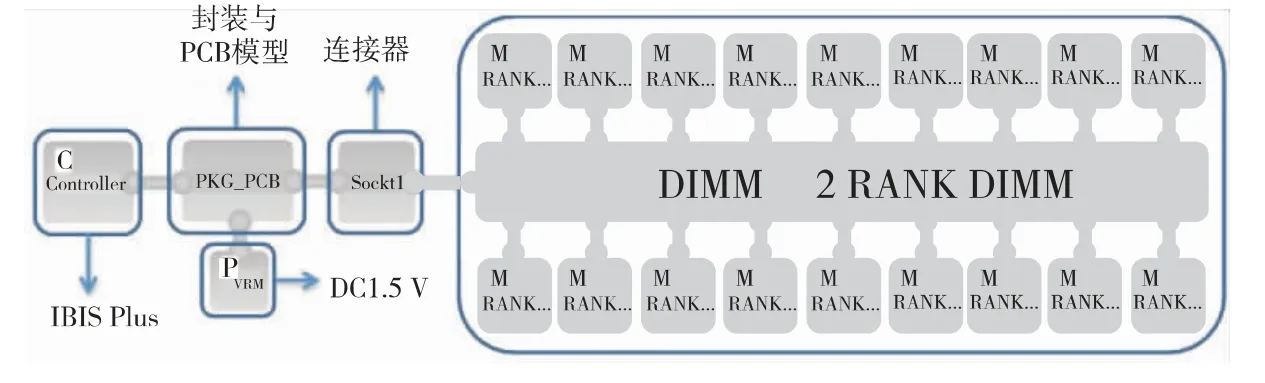

图4是目标电感的仿真拓扑:Controller为两个通道的I/O Buffer,PCB为等效的PDN与信号网络,PDN网络采用一个集总电感LPDN代替,Memory为内存颗粒的I/O模型,VRM提供1.5 V的理想直流电源。

Figure 4 Simulation topology of target inductance图4 目标电感仿真拓扑

所有的I/O Buffer采用相同的激励同时翻转,改变LPDN的大小,仿真得到I/O Buffer电源的纹波如图5所示。从图5中可以看出,LPDN的值越大,SSN造成的电源纹波也越大。当I/O Buffer的电源在1.2V~1.8V内波动时,对应的LPDN值即可作为DDR3I/O电源的目标电感的最大值。

Figure 5 Simulation results of target inductance图5 目标电感仿真结果

3.4 DDR3I/O电源目标阻抗确认

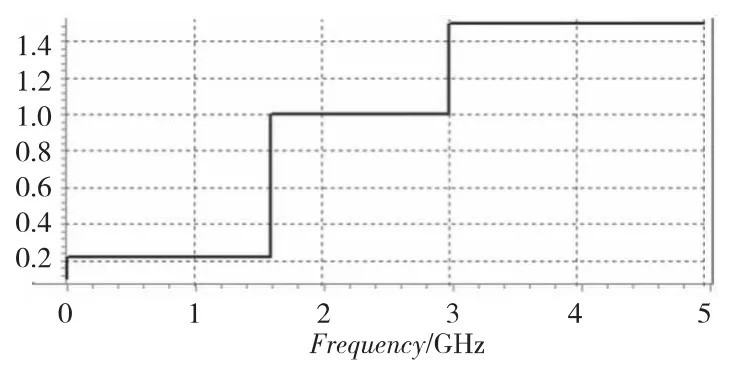

DDR3I/O Buffer的工作电流在直流至很高频率上都有分布,电流在各个频段上也不是均匀分布的,在确定I/O电源的目标阻抗时需要根据各个频段电流的大小计算不同频段的目标阻抗[5]。

本文通过仿真得到的电流波形进行傅里叶变换,得到电流的频谱图。该频谱图按峰值的一致性划分为三个频段:0Hz~1.6GHz,1.6GHz~3GHz和3GHz~5GHz。根据目标阻抗的计算公式得出的目标阻抗如图6所示。

4 设计与仿真协同优化

4.1 电源直流仿真

封装基板电源的直流仿真内容包括:

Figure 6 Target impedance of DDR3I/O power图6 DDR3I/O电源目标阻抗

(1)电流密度:确保电源地平面的面积和布局合理,电流密度不会太大而烧毁基板;

(2)过孔电流:确保电源地平面的过孔数量足够,过孔电流不会太大;

(3)直流压降:评估PDN的压降是否满足要求。

直流仿真与封装设计是一个不断迭代优化的过程,首先封装设计需要完成一个初步的包含电源地平面过孔的版本进行直流仿真,如果直流仿真达到要求则进行下一步的工作,反之则更改设计再次进行仿真,直到达到要求。

4.2 电源电感仿真

SSN与PDN电感成正比,为了减小电源噪声,必须减小PDN网络的寄生电感,将电源地的电感仿真与封装设计联合进行仿真优化。

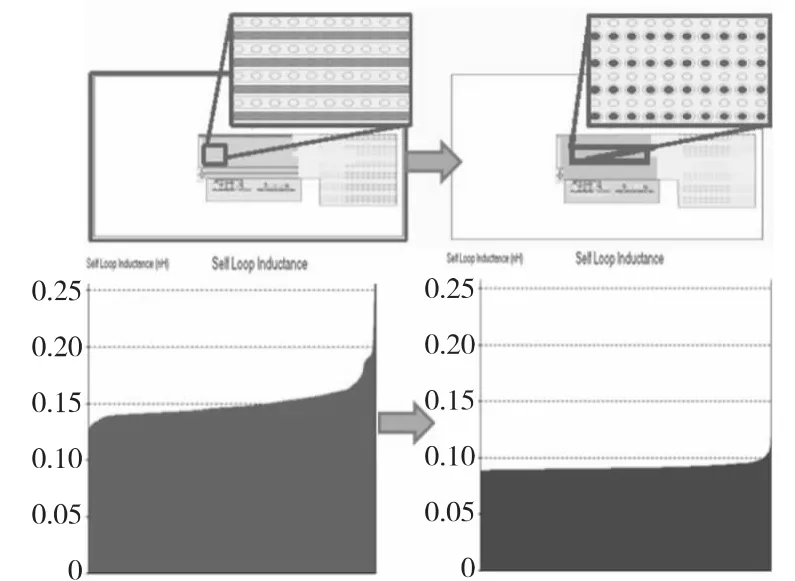

在封装基板电源电感仿真中的主要仿真内容包括:芯片引脚的自电感、芯片引脚的总电感和PDN的总电感。

(1)芯片引脚的自电感:是忽略其它芯片引脚的影响、仿真单独一个芯片引脚的电感,自电感可以用于评估单个芯片引脚的连接是否合理;

(2)芯片引脚的总电感:包含芯片引脚的自电感及与其它芯片引脚之间的互感;

(3)PDN总电感:是所有PDN芯片引脚上总电感的集总值。

如图7所示是一次电源电感仿真与封装设计联合优化过程。设计的初始版本,芯片引脚间距过小,所有的芯片引脚只能采用走线连接起来,经过仿真缝隙发现芯片引脚的自回路电感较大。根据仿真结果建议增大芯片引脚间距,将所有的地芯片引脚采用平面接连,再次仿真发现芯片引脚的自回路电感有了明显的减小。

5 封装的后仿真

5.1 电容优化

Figure 7 Inductance simulation of package substrate图7 封装基板电感仿真

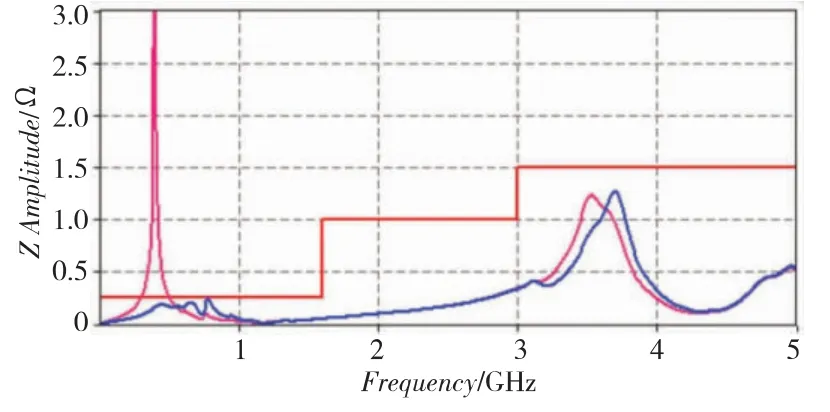

电容优化的目的就是选择合适的去耦电容,尽量减小PDN的阻抗。传统的电容优化方法一般有两种:一种利用EDA工具自动进行电容优化[6],这种方法简单易操作,但是不够灵活,不能针对谐振点进行优先优化;另一种方法是在参数提取工具中为每个电容赋上模型,然后提取电源的阻抗,这种方法灵活但是操作复杂,优化一次需要几个小时,非常耗费时间。

本文提出了一种全新的电容优化方法:首先提取PDN网络的S参数,提取时在芯片引脚和电容管脚上都加上端口,电容开路;然后将提取的PDN的S参数赋给封装与PCB,再将电容连接到相应的电容端口上,为电容选择合适的模型;最后从芯片端提取PDN的阻抗。

这种方法优化一次仅需要几秒钟时间,而且相当灵活,最终优化的结果如图8所示。从图8可以看出,优化之后DDR I/O的PDN阻抗谐振点有了明显的降低,并且到了目标阻抗之下。

Figure 8 Capacitance optimization results图8 电容优化结果

Figure 9 Simulation topology of DDR3图9 DDR3仿真拓扑

5.2 时序仿真

DDR3信号的仿真拓扑如图9所示。

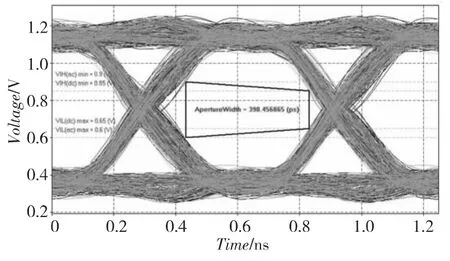

仿真时采用一个DDR3通道带一根双Rank内存条的结构,仿真速率为1 600Mbps,最终的仿真眼图结果如图10所示。由图10可以看出,DDR3的信号质量较好,经过计算各方面时序满足要求。

Figure 10 Eyediagram of DDR3signal simulation图10 DDR3信号仿真眼图

6 实验验证

FT1500封装设计采用的塑封材料为GX-13,封装厚度为1.35mm,使用10层基板,4-2-4的叠层结构。该芯片内核频率1.8GHz,DDR3数据传输率1 400Mbps,运行Stream测试程序,能够稳定运行24小时。

Figure 11 FT1500package implementation图11 FT1500封装实现

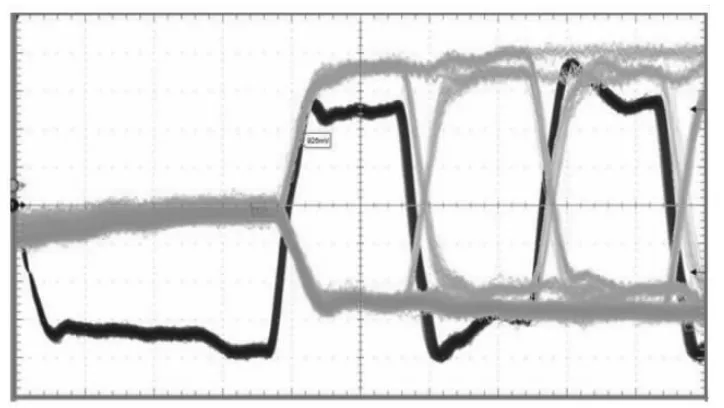

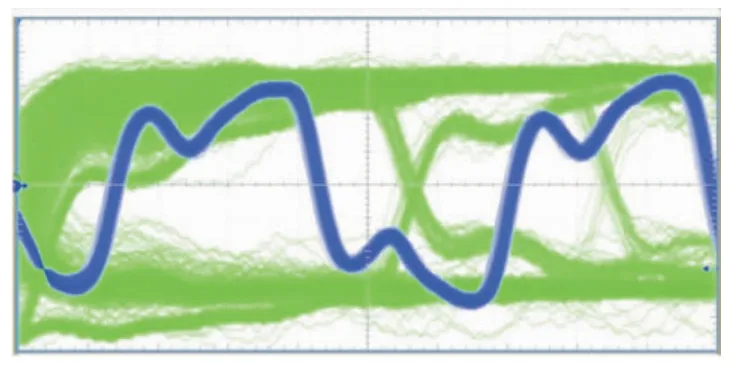

我们采用Tektronix公司的DSA72004示波器对FT1500芯片DDR3的数据信号以及命令控制信号进行幅值信号完整性的测试。该示波器四个通道高达20GHz的模拟带宽,示波器内采样信号的上升时间达到9ps,能够满足DDR3信号采样频率要求。

图12和图13分别给出了FT1500芯片1 400Mbps DDR3信号的写信号眼图和读信号测试眼图:写测试点选取PCB中CPU的底层信号线过孔处;读测试点选取内存条的SDRAM端信号线过孔处。测试信号选择同组内的DQS信号和DQ信号,其中DQS采用差分探头,DQ采用单端探头。从测试眼图可以看出,DQS信号和DQ信号的时序关系满足DDR3规范[7]的要求。

Figure 12 Eyediagram of DDR3write operation test图12 DDR3写操作测试眼图

Figure 13 Eye-diagram of DDR3read operation test图13 DDR3读操作测试眼图

7 结束语

本文面向核高基重大专项高性能微处理器FT1500的DDR3封装设计,提出了仿真驱动的封装设计方法,通过仿真方法建立设计规范、指导设计优化、验证设计结果,完成了四通道72bits DDR3接口的封装设计。对FT1500芯片的实测表明,DDR3接口可以稳定工作在1 400Mbps,信号的电源性和信号完整性满足DDR3规范要求。

[1] Eric B.Signal and power integrity—simplified[M].2nd Edition.NJ:Prentice Hall,2009.

[2] Burns D,Westerhoff T,Boyd J.Counting the piconseconds:Integrating timing,signal and power integrity analysis[C]∥Proc of DesignCon’08,2008:1.

[3] Choi M J,Pandit V.SI/PI co-analysis and linearity indicator[C]∥Proc of IBIS Summit Meeting,2010:1.

[4] Memory made easy DDR2/3analysis[Z].Pennsylvania: Ansoft Corporation,2010.

[5] Swaminuthan M,Engin A E.Power integrity modeling and design for semiconductors and systems[M].Li Yu-shan,Zhang Mu-shui,translation.Beijing:Publishing House of Electronics Industry,2009.(in Chinese)

[6] Herrick C.Acurate and efficient SSN modeling[Z].Pennsylvania:Ansoft Corporation,2008.

[7] JEDEC Standards.DDR3SDRAM specification:USA,JESD79-3E[P].2010-07-01.

附中文参考文献:

[5] Swaminuthan M,Engin A E.芯片及系统的电源完整性建模与设计[M].李玉山,张木水,等译.北京:电子工业出版社,2009.