基于LVDS总线和8 b/10 b编码技术的高速远距离传输设计

郭虎锋,陈香香,李 楠

(许继电气股份有限公司,许昌 461000)

随着信息技术的高速发展,对信息传输速度的要求也越来越高,在长距离的情况下像RS-232、RS-422、RS-485等串行数据接口传输标准,在传输速度、噪声、EMIEMC、功耗、成本等方面都难以实现要求。LVDS是一种低摆幅的差分信号技术,它使得信号能在差分PCB线对或平衡电缆上以几百Mb/s的速率传输,其低压幅和低电流驱动输出实现了低噪声和低功耗[1-2]。但是LVDS只能满足短距离高速数据传输,为此在设计中用到了驱动器和自适应均衡器,为保证数据传输中的直流平衡,在数据传输过程中采用8 b/10 b编码技术,这样LVDS信号就可以在2 km的光纤上理想传输。光纤传输系统具有容量大、传输距离远、抗干扰性强等优势,在通信传输方面有着不可替代的地位,有着很广阔的应用前景。

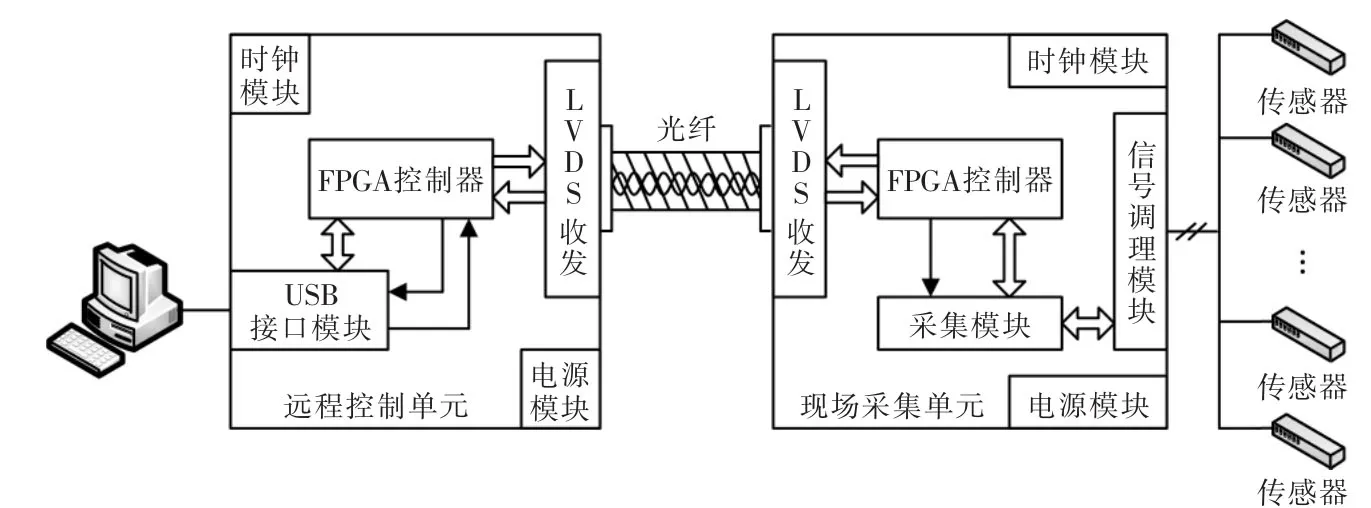

1 系统总体设计方案

针对现场环境较复杂,不易近距离进行控制与监测的情况,设计方案主要是实现现场采集单元与远程实时监测控制单元之间的高速长距离数据传输。系统框图如图1所示,现场采集单元使用FPGA为主控制器,负责控制采集模块对现场信号量进行采集和调理,在内部对采集数据进行预处理编帧后使用8 b/10 b编码技术编码输出,最后由LVDS模块驱动发送。远程控制单元使用LVDS模块进行数据的接收和均衡调节,之后由FPGA控制器对接收数据进行解码和处理,最后送到上位机进行解析。其中传输光纤长度为2 km。

图1 系统框图Fig.1 System block diagram

2 LVDS总线长线传输模块设计

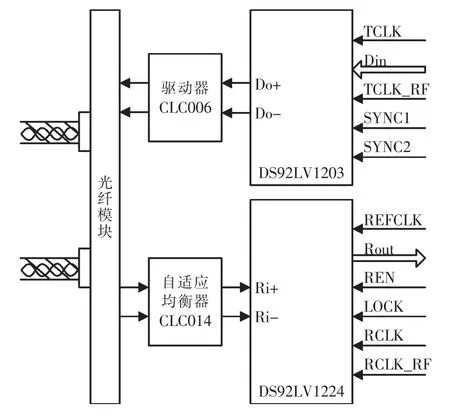

图2 LVDS模块框图Fig.2 LVDS module block diagram

LVDS模块硬件连接框图如图2所示,为一端接口模块框图,进行通讯的两端具有对称结构。DS92LV1203和DS92LV1224是2种LVDS芯片,DS92LV1203是可将10位并行CMOS或TTL数据转换为具有内嵌时钟的高速串行差分数据流的串行器;DS92LV1224则是接收该差分数据流并将它们转换为并行数据的解串器,串行器和解串器在应用中一般配套使用[3]。CLC006和CLC014分别是高速驱动器和自适应均衡器,LVDS信号在发送端需要高速驱动器来驱动,再经过长线远距离传输后信号会出现衰减现象,因此在长距离的接受终端应由自适应均衡器来接受并调节、均衡。

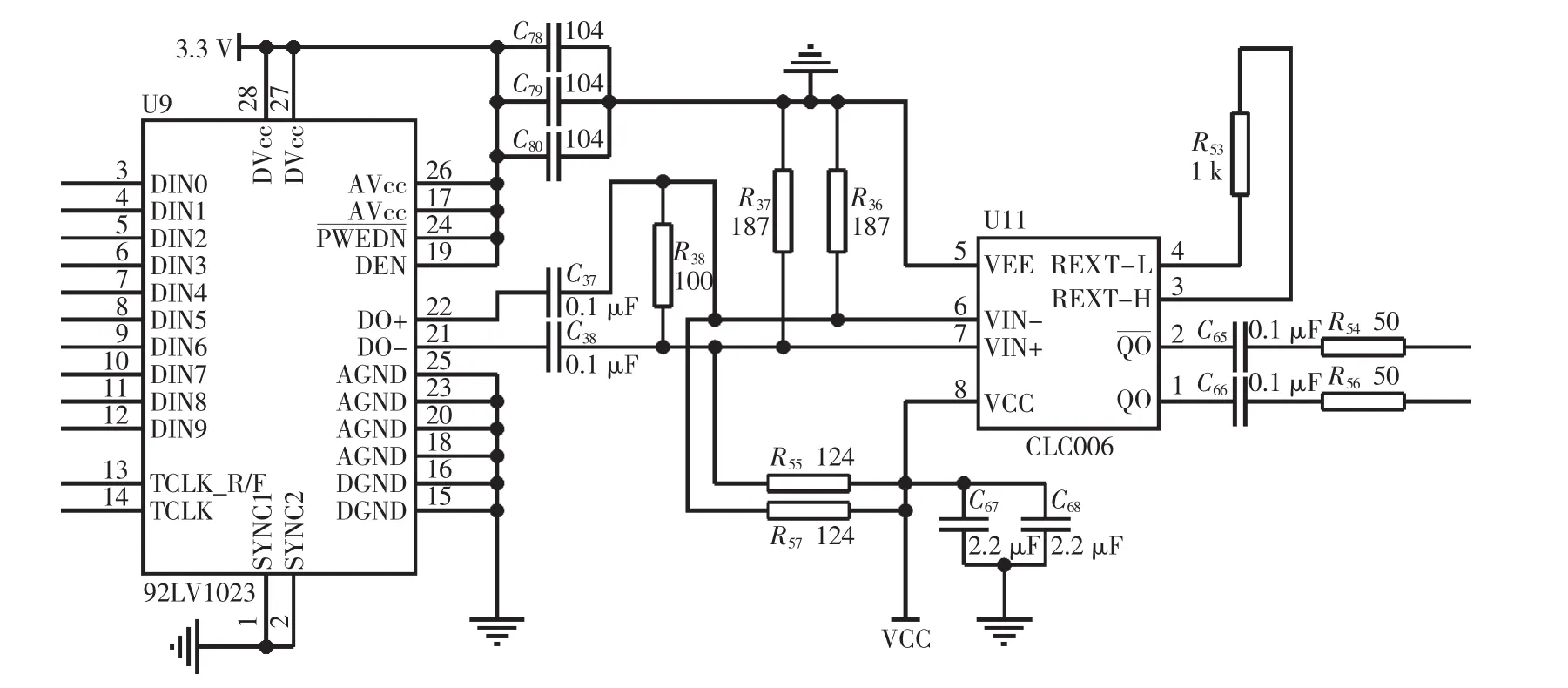

设计中采用的是集收发于一体的光纤模块,在发送端,串行器DS92LV1023将外部并行数据串化成串行数据,此时该串行器输出的差分压差是100 mV左右,这种小压差只能传输不到10 m的距离,但加上CLC006这款电缆驱动芯片后,其输出压差可达到2 V,这样就可以驱动地面光纤2 km以上的距离。信号经LVDS芯片后转换为LVDS信号,而光纤模块要传输的是LVPECL电平,在设计中采用电阻网络来实现2种电平之间的耦合转换。发送端部分电路图如图3所示。电阻R55、R57、R36、R37就是 为 实 现 LVDS电平和LVPECL电平的耦合而设计的电阻网络,R38为100 Ω是差分信号的阻抗匹配电阻。DS92LV1023芯片的TCLK时钟输入为40 Hz~60 Hz,管脚接入FPGA,由FPGA内部给出驱动时钟。TCLK_R/F管脚是控制DS92LV1023芯片在TCLK的上升沿还是下降沿取数,FPGA内部程序中给TCLK_R/F赋值 ‘1’,在TCLK的上升沿取数。PWRDN直接接到3.3 V电平上,使DS92LV1023芯片一直处于主动工作状态。对R53阻值的调节可以实现CLC006驱动能力的调节。

接收端部分电路如图4所示,光纤传输过来的信号经CLC014自适应均衡器均衡接受后送至DS92LV1224解串器进行串并转换。DS92LV1224的RCLK接入FPGA的IO口,时钟由FPGA输入。PWRDN和REN管脚直接接到3.3 V电平上,解串器处在主动工作状态。

3 8 b/10 b编码技术

图3 LVDS接口发送端硬件电路图Fig.3 LVDS sender hardware circuit diagram

图4 LVDS接口接收端硬件电路图Fig.4 LVDS receiver hardware circuit diagram

在高速串行数据传输中,当数据流中有多个连续的逻辑‘1’或逻辑‘0’时,信号的转换就会因为电压位阶段关系而造成信号错误,而直流平衡可以有效克服此问题。8 b/10 b编码特性之一便是可以保证数据传输的直流平衡,采用8 b/10 b编码方式,可以使发送数据流中的逻辑‘1’和逻辑‘0’数量基本持平,连续的逻辑‘1’或逻辑‘0’不会超过 5位,即每5个连续的逻辑‘1’或逻辑‘0’后必须插入1位‘0’或‘1’,从而保证传输信号的直流平衡。这样使用8 b/10 b编码技术后,10 b中的逻辑 ‘1’和逻辑‘0’的位数只可能出现以下3种情况:

(1)5 个逻辑‘1’和 5 个逻辑‘0’;

(2)6 个逻辑‘1’和 4 个逻辑‘0’;

(3)4 个逻辑‘1’和 6 个逻辑‘0’。

这3种情况对应的Disparity分别为0、+2、-2[4]。

3.1 编码原理

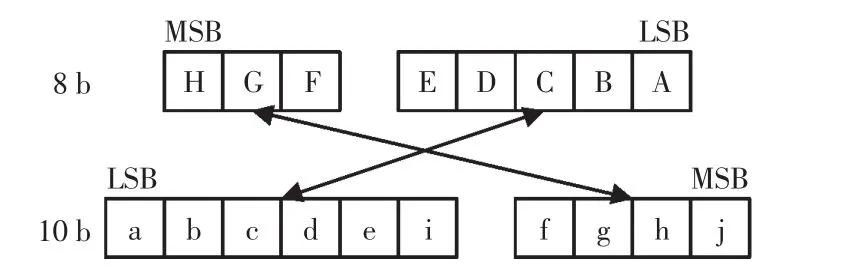

8 b/10 b编码方法是按照一定的编码规则把8 bit的数据编码成10 bit的数据。8 bit的数据对应268个有效编码列表,包括256个数据编码和12个控制字编码。其中控制字编码主要用于建立位同步、链路诊断、标示数据帧的开始与结束。一般首先把8 bit的数据分成2部分:低5位(EDCBA)和高3位(HGF),分别按照编码规则进行5 b/6 b编码和3 b/4 b编码,之后合并输出编码后的10 bit的数据(jhgfiedcba)[5]。编码原理如图 5所示。

图5 8 b/10 b编码原理图Fig.5 8 b/10 b encoding principle diagram

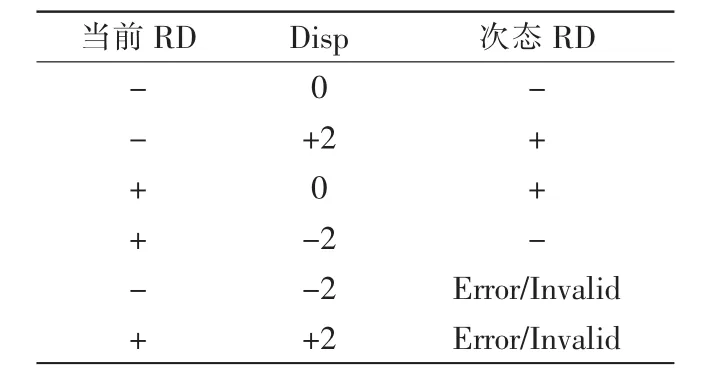

介绍编码规则之前,先引入RD(running dis-parity)参数的概念,RD表示数据的不平衡度,即表示数据中逻辑‘1’和逻辑‘0’的不平衡度,如果逻辑‘1’的个数大于逻辑‘0’的个数,则用 RD-表示;如果逻辑‘0’的个数大于逻辑‘1’的个数,则用RD+表示;如果逻辑‘0’的个数和逻辑‘1’的个数相等,则可用RD+或RD-表示。编码过程中,通过对RD的极性判断来选择对应码表中的码组。

编码规则是这样的,系统复位后默认RD初始极性为 “-”,根据当前的RD极性来从码表的2个10 b中选择一个做为当前8 b的编码,即先有RD极性,后对8 b进行编码,再根据此10 b编码决定下一个RD的极性,决定RD次态极性的规则如下:如果编码后的10 b码组中‘1’的个数与‘0’的个数相等,则次态极性保持不变;如果‘1’的个数与‘0’的个数不等,则次态的极性为当前极性的反转。无论是普通数据码组、特殊数据码组还是K控制码组都符合以上的编码规则。表1是RD转换规则。

表1 RD转换规则表Tab.1 RD transformation rules table

图6 8 b/10 b编码实现流图Fig.6 8 b/10 b encoding implementation flow chart

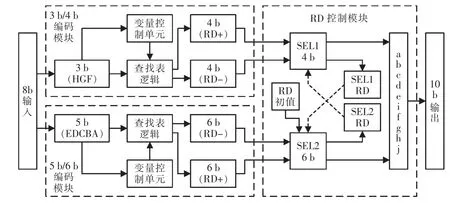

编码过程实现流图如图6所示,编码过程经由5 b/6 b编码模块、3 b/4 b编码模块和RD控制模块完成。在5 b/6 b编码模块和3 b/4 b编码模块中,由变量控制单元和查找表逻辑实现输入源码到码组的映射,大部分源码对应2种极性的码组。在RD控制模块中,初始RD为上电RD初值(上电或复位情况下,一般为RD-)或为上一次10 b编码后生成的RD,根据此RD极性来选择对应的6 b码组,同时决定次态RD;然后根据5 b/6 b编码生成的RD极性来判断选择对应的4 b码组,并生成次态RD,最后的RD作为下一个10 b编码的初始RD。最终把编码后的6 b与4 b进行组合,输出10 b数据。

在FPGA内部可以选择自己编写逻辑使用查找表的方法实现或者使用内部现有的IP核(encode_8 b/10 b)实现。

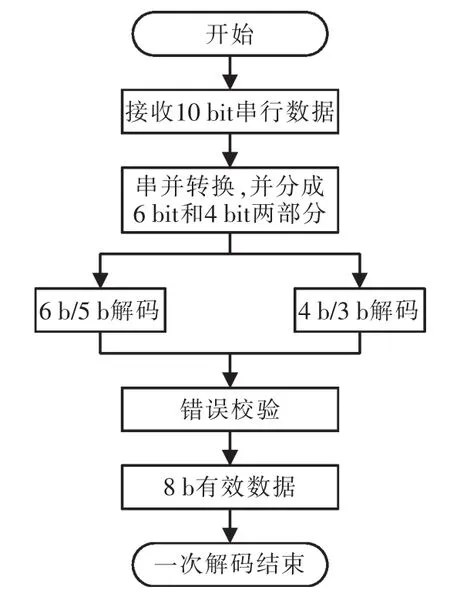

3.2 解码原理

8 b/10 b的解码过程相对编码过程较简单,是编码的逆过程,分别采用6 b/5 b和4 b/3 b来实现解码,此转换映射是多对一的关系。在5 b/6 b和3 b/4 b解码之后需要对数据进行检验,判断是否产生误码,如果为有效数据则进行8 b输出。解码流程图如图7所示。

图7 8 b/10 b解码流程图Fig.7 8 b/10 b decoding flow chart

在FPGA内部可以选择自己编写逻辑使用查找表的方法实现或者使用内部现有的IP核(decode_8 b/10 b)实现。

4 实验结果

经过实践考核,证实了此设计是可行的。在测试当中,现场采集端信号源模拟产生了00~FF的递增数据,传输速度为400 Mb/s,经过2 km长线传输,数据衰减现象较弱,数据正确无误码。如图8为上位机收到的数据拆分解包后绘出的图形。

5 结语

本文实现了一种基于LVDS总线和8 b/10 b编码技术的远距离传输设计,传输中采用光纤为传输介质,完成了以400 Mb/s的数据传输码率在2 km以上远距离的理想传输。终端采用USB接口,使得设计更加通用、方便。此设计已经成功地投入实际应用当中,传输性能可靠、稳定。

[1]姚永兴,焦新泉,马培娇.高可靠性远程数据传输系统设计[J].计算机测量与控制,2011,19(8):170-173.

[2]李霄光.基于LVDS高速串行总线通信技术的研究[D].西安:西安电子科技大学,2012.

[3]李斌,张会新,刘文怡.基于LVDS的高速图像数据存储器的设计与实现[J].电视技术,2014,38(8):48-52.

[4]A X Widmer,P A Franaszek.A DC-Balanced,partitioned-block,8b/10b transmission code[J].IBM Journal of Research and Development,1983,27(5):440-451.

[5]刘泳锐,张彦军,刘龙飞,等.8b/10b编码实现LVDS交流耦合传输中的直流平衡[J].科学技术与工程,2012,12(35):247-250.