小型数字集成电路测试仪的设计和实现

张 玲,李同瀚,梅军进

(湖北理工学院计算机学院,湖北黄石435003)

在数字设备开发过程中,由于数字集成芯片本身错误而导致的设备运行不稳定、调试不通的情况屡屡出现,而这种错误非常难以测试,不得不花费大量的时间和精力进行诊断,大大增加了开发成本。对小型数字集成电路进行测试不仅可以发现错误,而且可以定位错误,减少了开发成本[1]。测试即对集成电路施加测试向量,并比较测试响应的过程[2-4]。利用单片芯片作为控制芯片不仅结构简单、易于实现,而且功耗低、性价比高[5]。本设计以89C51芯片为 MCU芯片,以集成串并转换芯片及并串转换芯片为测试引脚扩展芯片,设计了小型数字集成电路测试仪。本方案具有以下几个方面的优点:结构简单,易于实现;方便对集成芯片进行测试,结果准确;所用芯片费用较低,性价比较高。

1 引脚扩展芯片的选择

对于数字芯片测试系统来说,处理器芯片的引脚个数有限,难以实现对具有多个引脚的数字集成芯片的测试。为了实现对引脚的控制,本设计利用串并转换芯片74HC595实现单个信号到多个信号的转换,以完成测试向量的串行施加;利用并串转换芯片74HC165实现多个信号到单个信号的转换,以完成测试响应的串行检测。

74HC595广泛应用于远程传输、显示器信号扩展等涉及串并数据转换的领域。它具有一个串行输入的8位移位寄存器、一个8位缓冲寄存器及一个具有三态输出的移位寄存器。

74HC165的功能是实现并行数据转串行数据,它主要应用在芯片端口扩展上。它具有一个8位寄存器和一个8位移位寄存器。

2 系统硬件结构设计

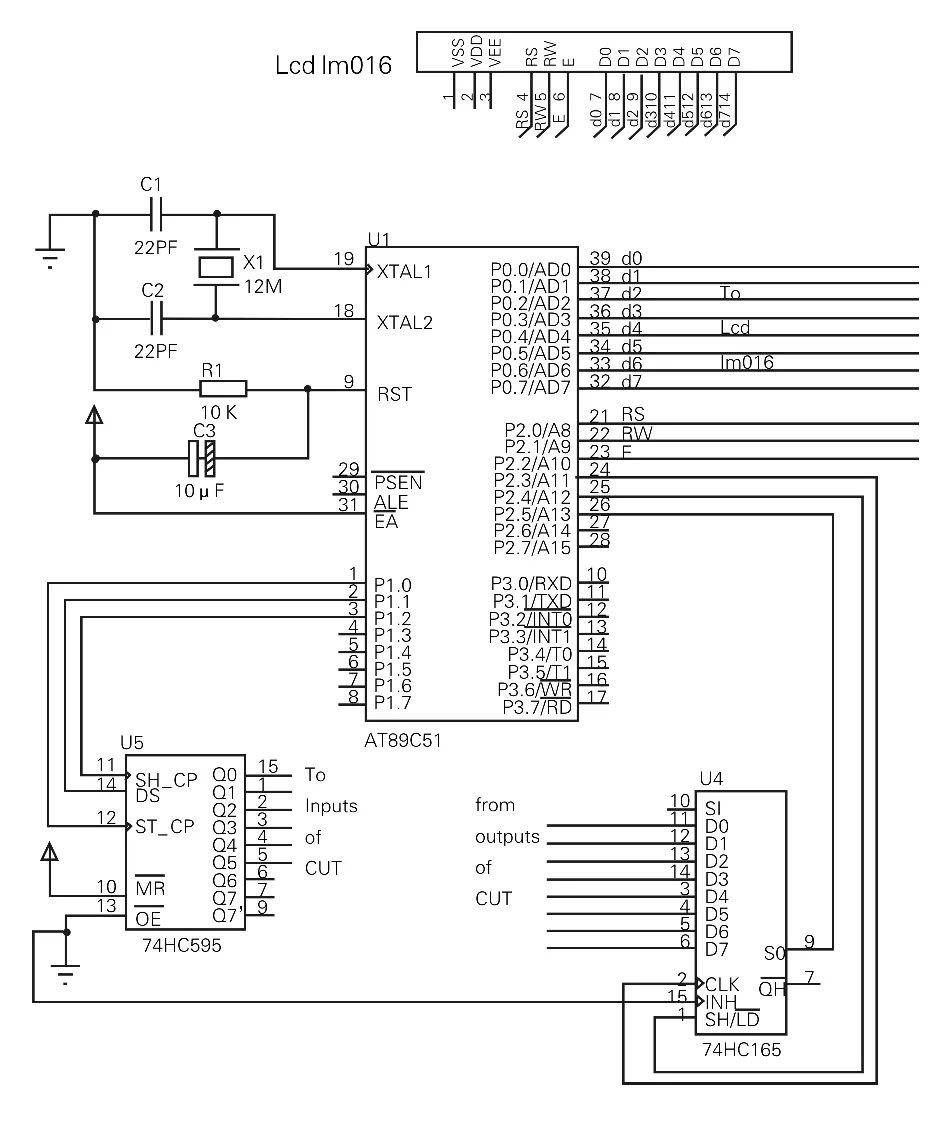

为了实现对具有多引脚的数字集成芯片进行测试,可以增加相应的引脚扩展芯片。以输入为n(n<=8)、输出为m(m<=8)的芯片的测试为例来说明测试仪的操作及控制,当测试芯片的输入、输出引脚少于8位时,不够的位用零扩展。本测试系统的硬件接线示意图如图1所示。为了通过串并转换芯片74HC595实现具有多位数据的测试向量的串行移入,MCU通过 P1口控制74HC595的转换,其中P1.0控制串行数据时钟输入端ST-CP;P1.1对接DS,从而在串行时钟ST_CP的控制下,测试向量从数据端DS施加到测试芯片的引脚上;P1.2控制并行数据的输出端时钟信号SH-CP,即74HC595的11脚,以实现8位并行数据的移出;其数据输出端Q0~Q7将转换后的并行测试数据,即测试向量施加到被测试电路(CUT,Circuit Under Testing);其10脚清缓冲脚直接接电源,表示不对缓冲进行清零;其13脚直接接地,始终使能该芯片。

74HC165芯片将包含多位测试位的测试响应转换成串行数据,以便由MCU检测。本设计主要用MCU芯片的P2口来控制该芯片的工作时序,P2.3接该芯片的2脚,即时钟信号CP(图1中用CLK表示);P2.5接该芯片的串行数据的输出端9脚,以在信号CP控制下实现测试响应的串行移出端Q7(图1中用SO表示);其P2.4控制该芯片的1脚,即异步并行读入信号(图1中用SH/LD表示),控制并行数据读入芯片74HC165寄存器中;D0~D7接受来自CUT的测试响应(from the outputs of CUT),通过74HC165实现测试响应的串行测试,从而实现对电路的测试。

为了显示电路的正确与否,本设计将相关结果显示在液晶显示器上。选择LM 016液晶显示器作为显示设备。如图1所示,P0口和P2口控制LM 016的时序,其中读写控制信号RS和RW分别由P2.0和P2.1控制,使能信号E由P2.2控制,显示的数据由P0传送。

图1 本测试系统的硬件接线示意图

3 系统软件设计

本软件设计主要分为2个部分,第1部分是2个芯片驱动程序的编写,它们分别为串并转换芯片74HC595和并串转换芯片74HC165的驱动程序;第2部分为MCU处理测试向量和测试响应算法的编写,主要包括测试向量真值表转换、所测测试响应和实际测试响应的比对算法的实现、芯片好坏的判定。

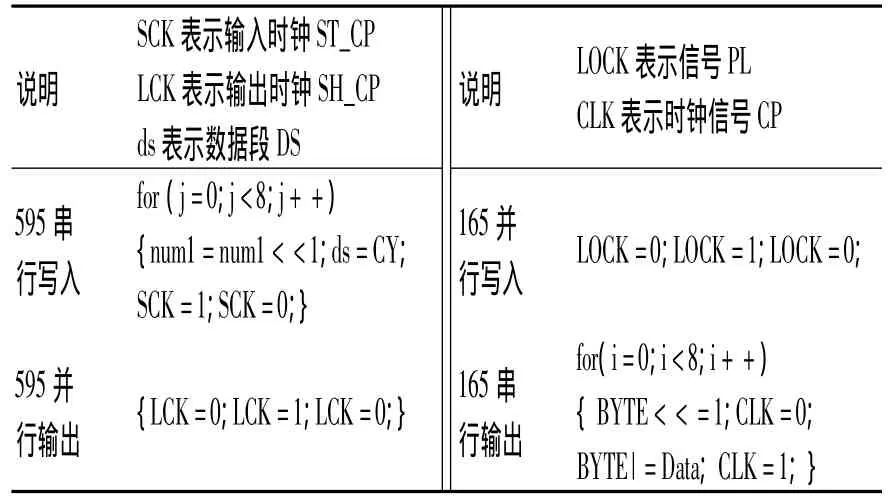

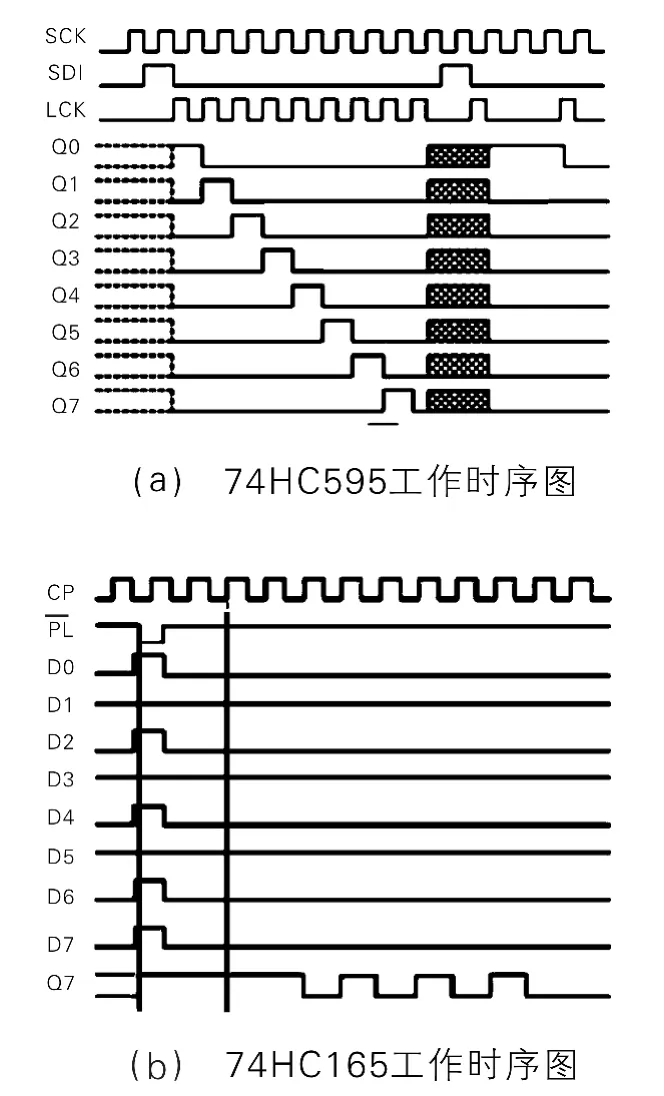

图2(a)给出了串并转换芯片74HC595的1位数据工作时序图,8位数据写入工作方式完全相同,此时序图为驱动程序编写的依据,由此时序图及对应图1所示的MCU与该芯片的连接图可知,其10脚清缓冲脚直接接电源,不对缓冲进行清零;其13脚直接接地,始终使能该芯片。其基本时序的运行如下,首先在输入时钟 ST_CP的上升沿的控制下,8位串行数据从DS送入,8个周期后,该8位数据被送入到74HC595的缓冲区;然后在输出时钟SH_CP的控制下,将8位并行数据从输出端Q0~Q7送出。并行数据的输出在时钟信号SH_CP的控制下,一个时钟上升沿便可完成输出。图2(b)给出了并串转换芯片74HC165的1位数据工作时序图,其基本时序运行为:设置PL为低电平,将并行数据读入芯片缓冲;在时钟CP的控制下,将数据串行移出。它们的关键控制代码如表1所示。

表1 驱动关键时序控制代码的实现

图2 主要芯片的工作时序图

本测试仪针对组合数字集成芯片进行测试,主要测试其功能,确保使用过程中的正确性。因此,MCU测试过程的实现主要包括2个部分,第1是功能测试向量的定义和施加,第2是测试响应的采集和比对。第1个过程主要通过表定义实现,组合电路的功能测试向量规模较小,很容易用表定义实现,测试向量的施加主要用循环实现;第2个过程中,测试响应仍由列表实现,CUT的测试响应由时钟控制采集后,按顺序取响应列表的正确值进行比对。

为了验证该系统的性能,本设计对常用组合逻辑 芯 片 74LS00、74LS02、74LS04、74LS86、74LS138、74LS153等大量芯片进行了测试,本系统均能准确地测出电路是否存在故障。

4 结束语

基于MCU控制的小型组合数字集成电路测试系统利用引脚扩展芯片实现对组合集成电路的测试,测试过程的测试向量和测试响应的存储以列表形式存储,测试向量的施加和测试响应的比对由MCU完成。测试结果表明,该测试仪测试速度快、测试结果准确,且系统稳定可靠。

[1] 黄考利,连光耀,高凤岐,等.基于USB2.0接口的数字电路测试仪的设计与实现[J].仪表技术,2006(4):43-45.

[2] 王元元.关于数字电路的故障测试方法研究[J].数字技术与应用,2013(2):87.

[3] 郭希维,苏群星,谷宏强.数字电路测试中的关键技术研究[J].科学技术与工程,2006,6 (18):2903-2905.

[4] 王继业.数字电路在线故障检测方法研究[D].哈尔滨:哈尔滨工业大学,2012.

[5] 张玲,梅军进.基于Atmega48和CC1100模块的无线通信功能的实现[J].黄石理工学院学报,2008,24(5):5-8.