基于FPGA的1553B总线同步头获取技术

王晓岭,李彤

(装甲兵工程学院,北京100072)

基于FPGA的1553B总线同步头获取技术

王晓岭,李彤

(装甲兵工程学院,北京100072)

准确获取同步头是MIL-STD-1553B总线数据帧解码的第一步,通过对1553B总线字同步头形态进行分析,列举了同步头的所有可能形态,基于1553B总线协议,明确了同步头获取和采样的原理和过程;1553B总线数据通过专门的总线接口接收,输入到可编程逻辑器件FPGA中,使用Verilog HDL硬件描述语言,对波形进行预处理以消除毛刺,并对同步头进行采样处理,最后使用ISE实现了结果仿真;该同步头获取方法为其后的信息解码创造了良好条件,丰富和完善了对1553B总线监测系统的研究。

1553B总线;同步头;FPGA

同步头获取是1553B总线及其他类型总线数据接收过程中十分关键的一个模块,只有正确解析出同步头,判断同步头类型,才能顺利完成信息的接收和译码。然而在以往的论文中,对于同步头采样的探讨不够深入透彻,或者只考虑了理想波形缺乏对实际波形状况的分析。这样在具体应用时难免产生错误。为此本文从1553B总线数据的接收,同步头形态分析,波形预处理以及同步头采样,结果仿真等一系列过程对同步头获取技术进行了全面的研究。

1 1553B总线接口

1553B总线数据通过专门的接口从总线上获取。1553B总线上传输的是模拟信号,需要通过由隔离变压器、数据收发器组成的接口电路转换成CMOS/TTL信号,才能输入到FPGA中进行处理。其接口电路如图1所示。其中隔离变压器采用的是HOLT公司生产的PM-DB2725型,其作用是实现从5V到3.3V的电压转换,避免收发器与总线直接相连发生故障。数据收发器采用的是HOLT公司生产的HI-1573型收发器,其作用是将隔离变压器传来的总线信号转化为FPGA可以识别的CMOS/TTL电平信号,或者将FPGA输出的CMOS/TTL电平信号,转化为可以驱动隔离变压器的双电平曼彻斯特码信号。FPGA可采用Xilinx公司生产的Spartan3系列产品。

图1 1553B总线接口图

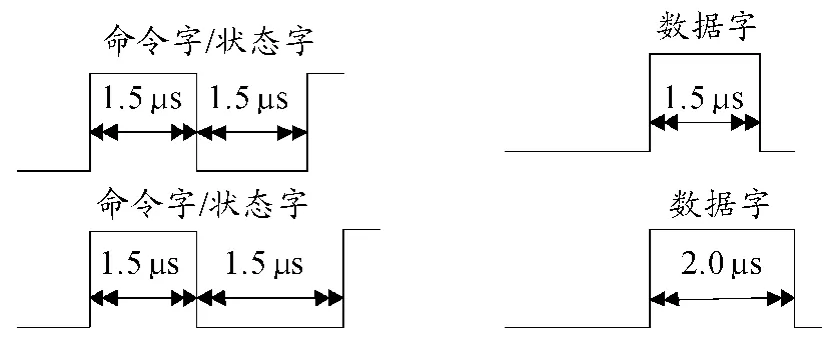

2 1553B总线同步头形态

1553B总线采用的是曼彻斯特Ⅱ型码对总线信息进行编码。在总线上传输的消息字包括3种类型:命令字、状态字、数据字。每种字的字长为20位,前3位为同步头,是无效的曼彻斯特编码,有效信息位是16位,最后一位是奇偶校验位。根据1553B协议格式,要完成16位有效数据的曼彻斯特解码,首先需要获取同步头。命令字和状态字的同步头电平先高(逻辑1)后低(逻辑0),而数据字则与之相反。因为1553B总线传输速率为1 Mbit/s,所以1位数据的宽度为1 μs,则同步头应该由两个宽度为1.5 μs的信息位表示。再结合数据位第一位可能为0也可能为1,总线上同步头的形态应包括图2所示4种情况。

图2 1553B总线同步头形态图

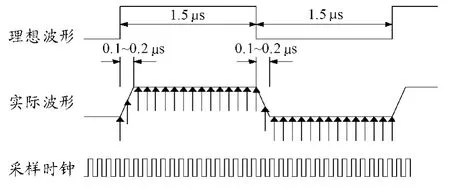

3 同步头预处理与采样

实际总线波形中,无论是从低电平到高电平的上升沿,还是从高电平到低电平的下降沿,都需要一定的建立时间,因此波形并不是理想波形,见图3。此外,总线中还存在干扰导致波形抖动,影响波形质量。因此在对同步头波形采样点逻辑值进行判断时,尤其是在上升沿和下降沿处,会出现判决错误的情况。

为了解决这个问题,一方面需要对波形进行预处理尽可能消除毛刺,方法是在有毛刺的输出端加D触发器。采用D触发器是因为D触发器的D输入端对毛刺不敏感,只要毛刺不在时钟上升沿时出现在D输入端,就不会对输出产生影响;另一方面需要在采样过程中对采样数留有余量。

采样的过程是每当时钟的下降沿时,将此时的数据存入移位寄存器中。因此系统时钟clk的频率选取十分关键。倘若选取的系统时钟频率过低,如2 MHz,则理论上高电平和低电平各有3个采样值,误差会非常大;若系统时钟频率过高,如50 MHz,则采样点太多浪费系统资源。综合考虑,选取10 MHz的时钟。这样理论上可以连续采样到15个高电平(逻辑1)和15个低电平(逻辑0)。实际的上升沿建立过程约为0.1~0.2 μs,即在上升沿宽度内可能存在1到2个采样值会出现判断错误。因此,当采样到13个以上的高电平,可以认为高电平检测结束,接着采样到14个以上的低电平,可以认为检测到了命令字/状态字,产生同步头类型信号rx_csw及同步头有效信号sync_en作为下一步解码的使能信号。同理可以进行数据字同步头的获取。

图3 同步头采样示意图

设计中采用状态机实现对同步头数据流的不间断判断。整个同步头获取逻辑如图4所示。主要包括数据缓冲器、比较器、同步头前半部分计数器和后半部分计数器,以及同步头有效信号控制器。由于状态机检测的不间断性,为了同步头有效信号只能保持一个采样周期,为此设计中还要加入信号保持、控制逻辑以保证同步头有效信号全局有效。

图4 同步头获取逻辑图

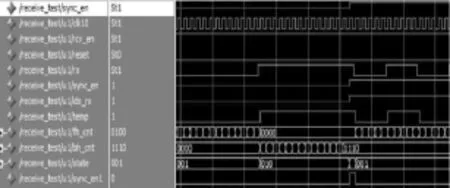

4 仿真结果

图5为同步头获取逻辑的仿真图。由图中可以看出,当后半部分计数器计数为14时,产生了同步头有效信号sync_ en1,但是在clk10的上升沿到来时,信号撤消了。sync_en才是经过相应的控制逻辑得到的全局同步头有效信号,此信号可以保持规定的一帧时间,以保证信号接收完毕。

图5 同步头获取仿真图

5 结束语

本文对1553B总线数据同步头的实际状态进行了研究,利用FPGA对同步头进行采样,设计了切实可用的同步头获取逻辑,完善了总线数据解码的过程。另外本设计具有一定的通用性,其设计思想可运用到MIC总线、CAN总线等其他类型总线数据同步头的检测。

[1]王磊.基于FPGA+LabVIEW的1553B总线监测系统的设计[D].成都:成都理工大学,2013.

[2]武鹏.高速1553B总线接口的设计及实现[D].西安:西安电子科技大学,2011.

[3]牛茜,靳鸿.基于有限状态机的1553B总线解码器设计[J].电子测试,2010(12):74-78.

[4]石红梅,姬劳,谢栓勤.用FPGA实现1553B总线接口中的曼码编解码器[J].单片机与嵌入式系统应用,2004(4):42-46.

[5]邢秀琴,姚竹亭.基于1553B总线的通信接口及其应用[J].中北大学学报:自然科学版,2007,28(1):91-94.

[6]牛茜.基于FPGA的1553B总线监测系统的设计[D].太原:中北大学,2011.

[7]常成,姬进军,李彤.通用车载总线测试系统的设计与实现[J].四川兵工学报,2014(8):108-110.

[8]王占领,张登福,李云杰.基于ARM和FPGA的1553B总线设备检测系统的设计[J].计算机工程与科学,2014,36(6):1005-1010.

[9]Zhijian L,Zhijian L.Research and design of 1553B protocol Bus Control Unit[J].International Convention on Information&Communication Technology,Electronics&Microelectronics,2010.

[10]Yousaf J,Irshad M,Mehmood I.Implementation of 1553B bus protocol on FPGA board using digital phase lock loop[J].International Conference on Emerging Technologies,2012(11):1-6.

(责任编辑杨继森)

Research on Synchronization Head for 1553B Bus Technology Based on FPGA

WANG Xiao-ling,LI Tong

(Academy of Armored Forces Engineering,Beijing 100072,China)

Accurately acquiring the synchronization head of MIL-STD-1553B bus is the first step in the data frame decoding.Through analyzing 1553B bus word synchronization head shape,the synchronization head of all possible forms were enumerated.Based on 1553B bus protocol,the process and the principle of sampling were clear.1553B bus data was received through specialized bus interface and input into the programmable logic device FPGA,using Verilog HDL hardware description language,the waveform preprocessing to remove burrs and the synchronization head sample processing.Finally we used the ISE to realize the simulation results.This method has created favorable conditions for the following information decoding and enriches the study of 1553B bus monitor system.

1553B bus;synchronization head;FPGA

王晓岭,李彤.基于FPGA的1553B总线同步头获取技术[J].四川兵工学报,2015(11):122-124.

format:WANG Xiao-ling,LI Tong.Research on Synchronization Head for 1553B Bus Technology Based on FPGA[J].Journal of Sichuan Ordnance,2015(11):122-124.

TN919.6

A

1006-0707(2015)11-0122-03

10.11809/scbgxb2015.11.032

2015-04-25

王晓岭(1990—),男,硕士研究生,主要从事战术通信技术研究。