基于双派克变换的单相数字锁相环设计

李伟锋, 王 哲

(中原工学院, 郑州 450007)

基于双派克变换的单相数字锁相环设计

李伟锋, 王哲

(中原工学院, 郑州 450007)

摘要:针对单相并网变流器的同步问题,为了消除传统正交虚拟信号生成中的延迟环节,结合坐标变换,提出了一种基于双派克变换的无正交虚拟信号的同步单相锁相环设计方法。将单相信号作为派克变换的一相输入,另一相为零,通过两个派克变换,最终获得单相信号的频率和相位,并验证了算法的正确性。分析了基于双派克变换的数字锁相环系统结构;解决了数字系统初值优化的问题;设计了相应的压控振荡器和滤波器及双派克变换的程序结构,实现了系统的数字化设计。仿真和实验结果表明,所设计的基于双派克变换的数字锁相环可准确快速地实现锁相功能。

关键词:双派克变换;锁相环;初值优化;数字化设计

目前,锁相环(Phase-locked loop,PLL)技术被广泛地应用于电力系统和通信系统,以获得输入信号的相位[1-3]。较之传统的反馈滤波法[4]、离散傅里叶法[5]、希尔伯特变换法[6]等,锁相环实现简单,易于数字化处理。在电力电子设备中,变流器锁相系统的准确性,不仅对系统并网有直接影响,同时也影响整个控制系统的性能[7-11]。

单相锁相环设计通过采样得到单相电压信号,再经过延迟1/4周期得到其正交虚拟信号,从而构建两相静止坐标系,通过派克变换得到旋转坐标系中的d、q分量,控制无功分量为零,经过压控振荡器(VCO)即可得到相位信息[12-14]。但是,其缺点在于正交虚拟信号生成过程中引入的延迟环节。它使数字系统必须等待一段时间才能实现锁相运算,对控制系统的性能带来了负面影响[15-19]。

本文针对锁相环中信号的同步问题,提出了基于双派克变换的数字锁相环设计方法,无需引入延迟环节,可实现信号同步,快速获得输入信号相位信息,达到锁相效果。

1带有虚拟延迟的数字锁相技术

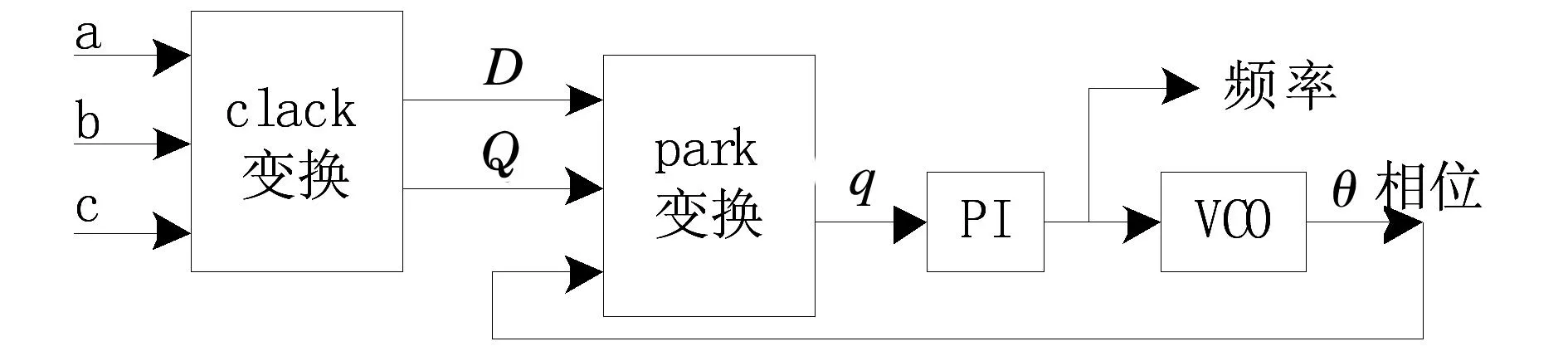

对于三相系统而言,通过克拉克变化即可得到两相静止坐标系中的D、Q分量,再经过派克变换得到两相旋转坐标系中的d、q分量,通过控制无功分量即q为0,闭环系统调制,得到所需的相位信息[20]。其原理如图1所示。

图1 三相系统锁相原理结构图

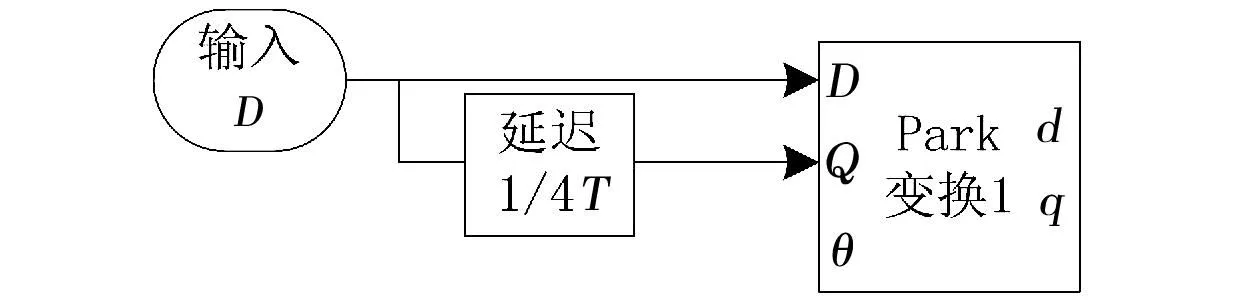

在单相系统中,由于只有a、b、c中的一相,因此将单相信号作为图中两项静止坐标系D、Q中的一相,作为派克变换的输入,另一相通过延迟的方法得到。例如将单相信号作为D相输入,则另一个正交量Q则需要将单相信号延迟1/4周期得到,从而完成派克变换(见图2、图3)。延迟环节不利于后端信号的处理,同时过大的延迟等待会增加控制器的负荷,严重影响了控制系统的性能。

图2 使用延迟的单相派克变换

图3 延迟后的D、Q信号波形

2采用双派克变换的同步锁相技术

将单相信号作为派克变换的D相输入,Q相输入为0,则在两相静止坐标系中D轴的数值按照一定的频率呈现正弦或者余弦规律变化。假设输入信号为:

(1)

经过派克变换得:

(2)

当系统稳定,相位锁定成功时,θ=wt,则式(2)可变换为:

(3)

可见,式(3)中包含了直流分量和交流分量,同时两个分量间具有一定的相互关系。

若利用低通滤波器,滤除式(3)中的二倍频交流分量,则式(3)变为如下形式:

(4)

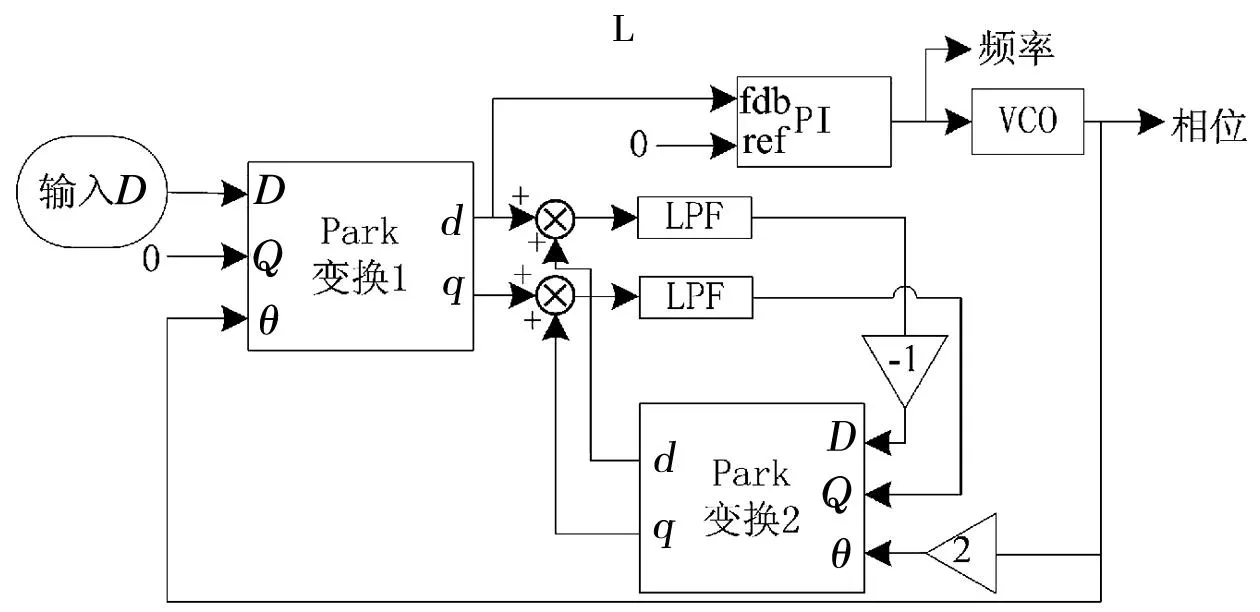

此时,若将φ值取反,并再次进行派克变换(本次派克变换中θ=2wt),则式(4)变为:

(5)

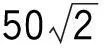

基于上述理论的双派克锁相环结构如图4所示。派克变换1和派克变换2是两个相同的派克变换过程。LPF为低通滤波器,用来滤除二倍频的交流分量;VCO为压控振荡器。

图4 基于双派克变换的锁相环结构图

3数字锁相环系统设计及仿真验证

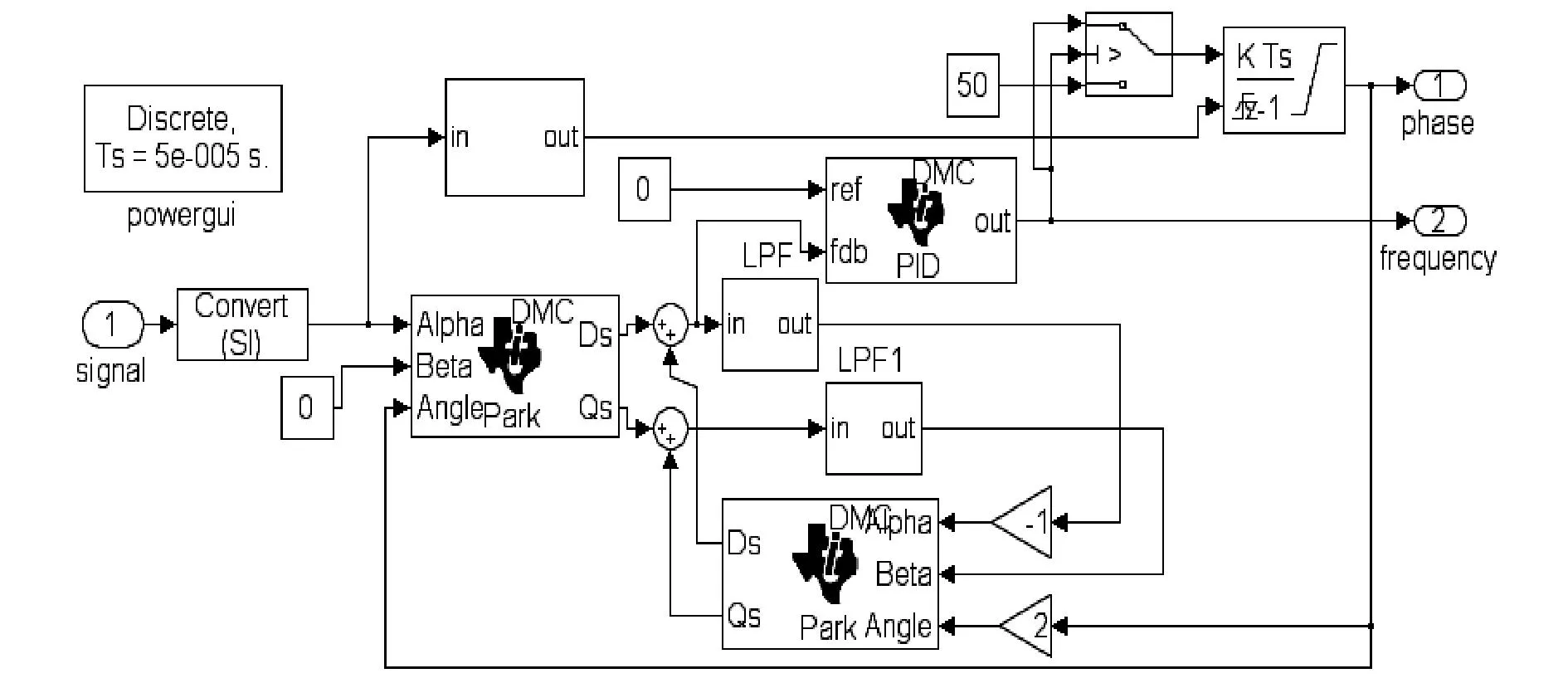

数字锁相环系统主要基于DSP2812控制芯片,采用MATLAB/simulink模块构建。数字系统的搭建由于其固有的离散性,各个位置的信号产生不具有同步性,因此成为设计的难点。根据图2,在进行派克变换1运算时,相位参数θ在离散系统起步,即t=0时并没有得到具体的θ值,系统无法完成派克变换1的运算,继而影响了整个新系统的起步;离散系统中VCO的设计,如何获得在离散情况下单周期的定积分,也成为系统正确运行的决定因素。

3.1初值优化问题

针对数字系统的离散特性,在零时刻,派克变换1运算只得到了α、β的输入,θ值由于系统运算的延迟并未得到。此时,不妨给出一个固定的θ值,在系统成功起步时,计算出输入信号相位信息之后再换成自身的相位信号。在图5所示的设计中,加入一个选择判断模块,在PI输出趋于稳定前,使用一个固定的虚拟值。当PI调节趋于稳定时,系统换成本身的相位信号运行,确保了系统的PI调节能够快速达到理想状态。

3.2数字压控振荡器的设计

压控振荡器的传递函数可等效为1/s,即积分环节[21]。因此,数字压控振荡器就是一个定积分函数。积分时间为输入信号的一个周期。数字压控振荡器采用在输入信号每个周期上对频率积分的过程来实现。

图5 双派克变换的数字系统程序结构图

3.3数字低通滤波器设计

图6 双派克变换中数字滤波器结构图

3.4仿真验证

在图5所示的系统中,输入幅值为1的正弦信号,分别测试50 Hz、60 Hz情况下的锁相结果。其仿真结果分别如图7、图8所示。

图7 输入信号50 Hz时的锁相效果

图8 输入信号60 Hz时的锁相效果

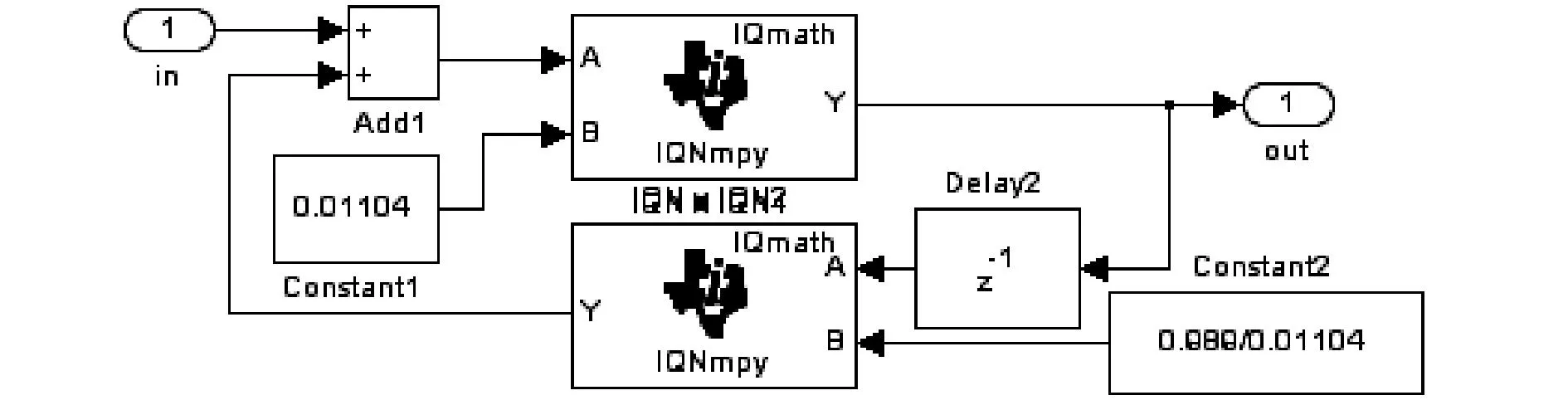

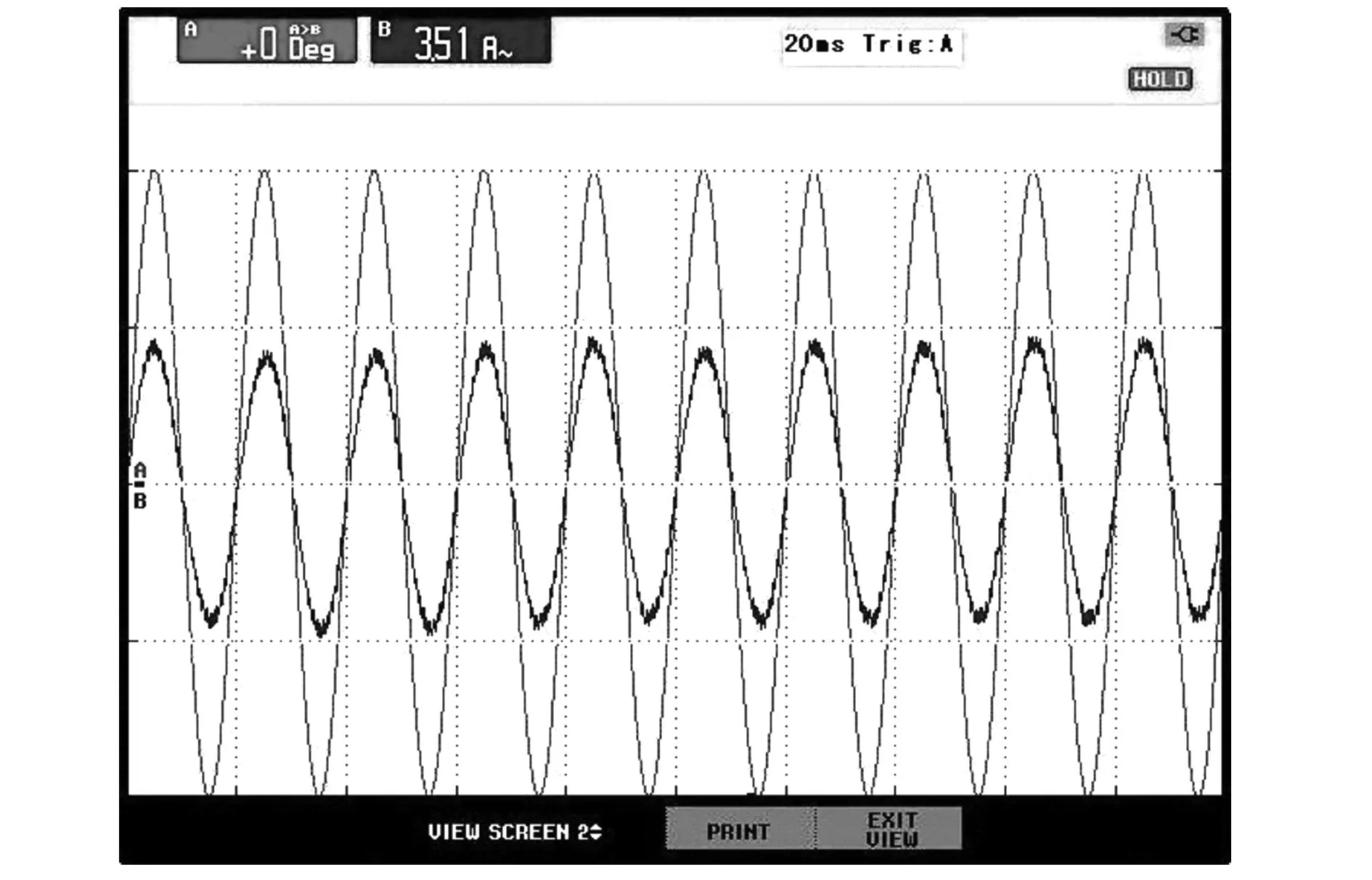

4实验

采用simulink实时仿真控制工具箱,搭建单相电流环锁相程序,基于DSP2812控制芯片,搭建硬件实验平台,在单环实验中验证锁相环程序的实用性。其控制程序如图9所示。

图9 基于双派克变换锁相环的单环系统控制程序图

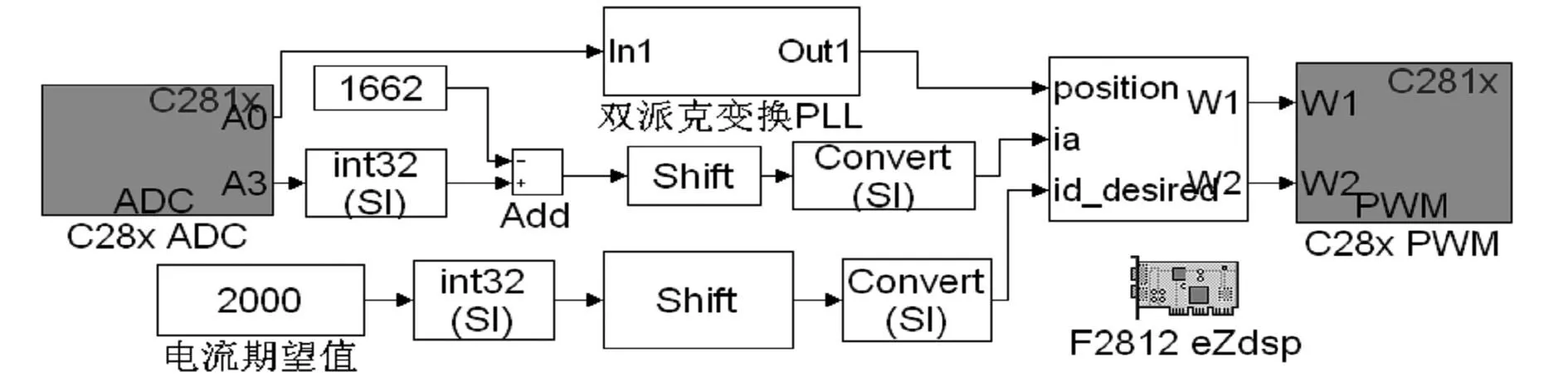

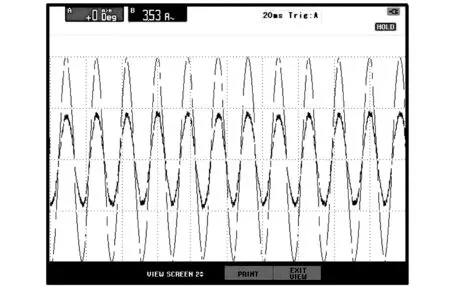

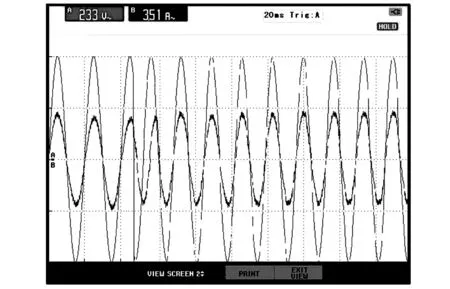

对于频率分别为50 Hz、60 Hz的电网电压,实验得到不同的锁相结果,如图10、图11所示。

图10 电网频率为50 Hz时单环系统锁相效果

图11 电网频率为60 Hz时单环系统锁相效果

为了测试电网频率改变时的锁相效果,在某一刻电网频率由50 Hz变为60 Hz的情况下,电流锁相效果如图12所示。

图12 电网频率由50 Hz变化到60 Hz时单环系统锁相效果

实验结果表明,基于双派克变换的单相电流环锁相效果良好,能够将内环电流锁定到电网相位,得到与电网相位相同的电流波形。同时,它在电网相位变换的情况下也能够较快实现跟踪锁相效果。

5语结

基于双派克变换的数字锁相环能够实现正交输入信号的同步,快速达到锁相的目的,对于数字系统锁相功能的实现提供了新的方法。仿真和实验同样验证了基于双派克变换的数字锁相环的实用性,对工业实践具有指导意义。

参考文献:

[1]Floy M Gardner.锁相环技术[M].北京:人民邮电出版社,2007:179-193.

[2]李明,王跃,方雄,等.无正交虚拟信号生成的单相DQ锁相环研究 [J].中国电机工程学报,2011,31(13):27-32.

[3]陶兴华,李永东,孙敏,等.一种基于同步旋转坐标变换的单相锁相环新算法 [J].电工技术学报,2012,27(6):147-152.

[4]Giuseppe Fedele, Ciro Pocardi. Apower Electrical Signal Tracking Strategy Based on the Modulating Functions Method[J]. IEEE Transactions on Industry Electronics, 2009, 56(10): 4079-4086.

[5]Dela O A. A New Digital Filter for Phasor Computation, Part I: Theory[J]. IEEE Transactions on Power Systems, 1998, 13(3): 1026-1031.

[6]Rodriguez P. Decoupled Double Synchronous Reference Frame PLL for Power Converters Control[J]. IEEE Transactions on Power Electronics, 2007, 22(1): 584-592.

[7]金曼,苏建徽. 光伏并网逆变器中的单相数字锁相环研究 [J]. 电力电子技术,2011,45(6): 6-8.

[8]田桂珍,王生铁,林百娟. 基于d-q变换的改进型锁相环设计 [J]. 内蒙古工业大学学报,2009,28(1): 64-68.

[9]袁江伟,吕征宇. 一种新型的单相并网系统锁相环 [J]. 电力电子技术,2011, 45(7): 81-100.

[10]Moreno V M, Marco L. A Comparative Analysis of Real-time Algorithms for Power Signal Decomposition in Multiple Synchronous Reference Frames[J]. IEEE Transactions on Power Electronics, 2007, 22(4): 1280-1289.

[11]Kaura V, Blasko V. Operation of a Phase Locked Loop System Under Distorted Utility Conditions[J]. IEEE Transactions on Industry Applications, 1997, 33(1): 58-63.

[12]Santos Filho R M, Seixas P F, Cortizo P C, et al. Comparison of Three Signal-phase PLL Algorithms for UPS Applications[J]. IEEE Transactions on Industrial Electronics, 2008, 55(8): 2923-2932.

[13]Salamah A M, Finney S J, Williams B W. Three-phase Phase-lock Loop for Distorted Utilties[J]. IET Electer. Power Appl., 2007, 1(6): 937-945.

[14]Choi J W, Kim Y K, Kim H G. Digital PLL Control for Signal-phase Photovoltaic System[J]. Electric Power Applications, IEE Proceeding, 2006, 153(1):40-46.

[15]Gyugyi L. Static Synchronous Series Compensator: a Solid-state Approach to the Series Compensation of Transmission Lines[J]. IEEE Transactions on Power Delivery, 1997, 12(1): 406-417.

[16]Divan D, Johal H. Distributed FACTS-A New Concept for Realizing Grid Power Low Control[J]. IEEE Transactions on Power Electronics, 2007,22(4):2253-2260.

[17]Padua M S. Comparative Analysis of Synchronization Algorithms Based on PLL, RDFT and Kalman Filter[C]//International Symposium Industrial Electronics. Recife:IEEE, 2007:1928-1934.

[18]Ciobotaru M, Teodorescu R, Blaabjerg F. A New Single-phase PLL Structure Based on Second Order Generalized Integrator[C]//Power Electronics Specialists Conference. Jeju, Korea:IEEE, 2006:1-6.

[19]Makoto Saitou, Tosihisa Shimizu. Generalized Theory of Instantaneous Active and Reactive Powers in Single-phase Circuits Based on Hilbert Transform[C]//Power Electronics Specialists Conference. Cairns:IEEE, 2002: 1419-1423.

[20]李亚斌,彭咏龙,李和明.自采样比例积分控制全数字锁相环的性能分析和实现 [J].中国电机工程学报,2007,25(18):64-69.

[21]Chung Se-Kyo. A Phase Tracking System for Three Phase Utility Interface Inverters[J]. IEEE Transactions on Power Electronics, 2000, 15(1): 431-438.

(责任编辑:王长通)

Design of Single-phase Digital Phase-locked Loop

Based on Double Park Transformation

LI Wei-feng, WANG Zhe

(Zhongyuan University of Technology, Zhengzhou 451191, China)

Abstract:According to the synchronization problem of single-phase grid connected converter, in order to eliminate the traditional orthogonal virtual signal generation used delay link, combined with the coordinate transformation, this paper puts forward a design of single-phase phase locked loop based on double Park transform that has no orthogonal virtual signal and be synchronized . The single-phase signal will be one of the Park transformation input, another input is zero. Finally the single-phase signal’s frequency and phase will be obtained after two Park transformations. The algorithm is verified from the point of view of mathematics; the digital phase locked based on double park transformation system structure is raised; the initial value problem of optimized digital system is solved; the corresponding voltage controlled oscillators and filters are designed; and the program structure of double park transformation is also designed, the design of digital system is realized. The simulation and experimental results show that, the design of digital phase locked loop based on double Park transformation can quickly and accurately achieve phase lock function.

Key words:double Park transformation; phase locked loop; initial value optimization; digital design

文章编号:1671-6906(2015)01-0031-04

作者简介:李雪丽(1983-),女,河南正阳人,硕士,主要研究方向为机电测控技术。

收稿日期:2014-07-26

中图分类号:TM 46

文献标志码:ADOI:10.3969/j.issn.1671-6906.2015.01.007