3D SRAM中TSV开路测试算法研究与实现*

赵振宇,邓 全,李 鹏,蒋剑锋,曲连华,唐皓月

(国防科技大学 计算机学院, 湖南 长沙 410073)

3D SRAM中TSV开路测试算法研究与实现*

赵振宇,邓 全,李 鹏,蒋剑锋,曲连华,唐皓月

(国防科技大学 计算机学院, 湖南 长沙 410073)

基于三维集成电路技术实现的三维静态随机存储器,其电路中使用了大量的过硅通孔。目前过硅通孔制造工艺尚未成熟,使得过硅通孔容易出现开路或短路故障,从而给三维静态随机存储器的测试带来新的挑战。现有的过硅通孔专用测试方式虽然能够探测出过硅通孔的故障,但需要特定的测试电路来实现,这就增加了额外的面积开销,同时加大了电路设计的复杂度。因此,提出一种使用测试算法来探测过硅通孔开路故障的方法。在不增加额外面积开销的情况下,通过内建自测试电路解决三维静态随机存储器中过硅通孔的开路故障检测问题。结果显示,该过硅通孔测试算法功能正确,能够准确探测到过硅通孔的开路故障,并快速定位过硅通孔的开路位置。

三维集成电路;过硅通孔;开路故障;测试;算法

基于三维集成电路(Three Dimensional-Integrated Circuit, 3D-IC)技术的三维静态随机存储器(Three-Dimensional Static Random Access Memory, 3D SRAM)采用多层器件结构组成,通过内在的垂直互连介质过硅通孔(Through Silicon Via, TSV)完成不同层器件之间的通信[1]。3D SRAM拥有2D SRAM所不具有的很多优势,例如可以缩短管芯(die)与管芯(die)之间的互连线长度,提高输入/输出(Input/Output, IO)带宽,从而减小互连线延迟,提升性能,并降低功耗[2]。3D SRAM还可以进行异质集成,以此缩小设计面积和制造成本。

3D SRAM中有超过数以万计的TSV,由于TSV的制造工艺尚不成熟,铜柱内约有42%的概率产生气泡或空隙[3],从而导致TSV产生开路故障;又由于TSV之间寄生耦合电容的影响,TSV存在开路故障时,浮空导线与相邻导线之间的寄生耦合电容对浮空端的电压影响很大。在TSV尺寸继续减小的情况下,TSV之间的间距也越来越小,这种耦合效应也越明显,不仅影响自身,而且还可能影响周围的电路,最终导致SRAM失效。相关研究表明,规模为104个TSV的芯片中出现TSV失效的概率为63.214%[4],严重影响3D芯片的良品率。因此,如何有效地对TSV进行测试是3D-IC中急需解决的问题。近年来学术界和工业界对片上TSV测试结构的研究从未中断过。

文献[5]提出了一种用于TSV故障诊断的内建自测试(Built-In Self Test, BIST)结构,并将TSV建模为2D矩阵的形式。尽管这种测试结构拥有面积开销小的优势,但一次只能测试TSV矩阵中的一行,当TSV数量较多时,将耗费很长的测试时间。而另一种BIST结构[6]使用基于KAF(Kth-Aggressor-Fault)可编程模型产生有效测试序列,用于探测TSV之间的串扰故障,这种结构可以提供更精准的TSV测试结果。然而,由于每个TSV都需要单独的发送器和接收器,这将需要很大的面积开销。输出阈值分析测试结构[7]通过使用环形振荡器来探测TSV的故障。这种结构能有效处理由TSV故障引起的信号延时问题,并且具有面积开销小的优势,但能探测的TSV故障类型有限。

针对3D SRAM中字线和位线TSV的全开路故障,提出了一种有效的片上TSV测试方法。将TSV测试机制与Memory BIST结构相结合,使用测试算法来探测TSV开路故障。由于共用Memory BIST,本文所提测试方法可以有效缩短测试时间和面积开销。结果显示,该TSV测试算法功能正确,能够准确探测到TSV的开路故障,并快速定位TSV的开路位置。

1 TSV开路故障行为

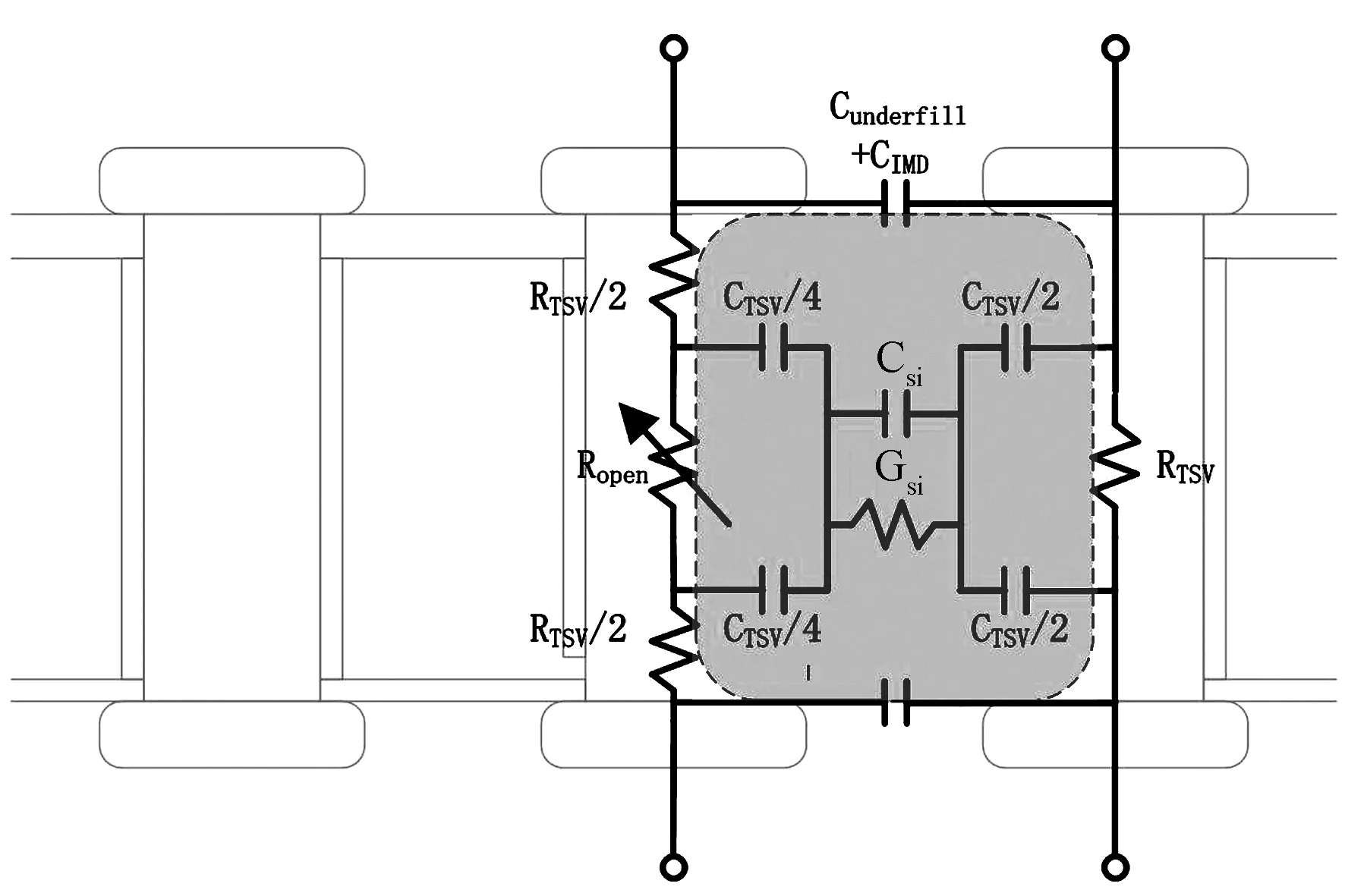

1.1 TSV开路故障耦合模型

目前,对TSV的耦合电学建模研究已经相当深入,相比传统的使用固定故障、桥接故障来分析TSV的故障,MAF(Maximum Aggressor Fault)故障模型[8]则被广泛地应用于探测TSV的耦合故障。文献[9]结合TSV的生产工艺建立了TSV的串扰Spice电路模型。文献[10]全面考虑了TSV的寄生分量建立了TSV耦合电学模型。为了更好地实现对3D SRAM中字线TSV和位线TSV的全开路故障进行模拟以及分析TSV开路故障对存储器的影响,从TSV之间的耦合效应入手,基于TSV开路故障电学模型和TSV耦合电学模型,建立了TSV开路故障耦合效应电学模型,如图1所示。该模型既考虑了TSV的开路故障,同时又考虑了TSV之间的耦合效应,模型中的参数均可由文献[11]中的公式计算得到。

图1 TSV开路故障耦合效应电学模型Fig.1 TSV open defect coupling model

1.2 TSV故障定位

3D堆叠存储器可以通过多种方式来实现,一种有效的方式是用TSV做垂直总线,将多个SRAM层连起来,接到处理器上[12];另外一种方式是将存储阵列分很多小块,并在垂直方向上进行堆叠,用TSV代替原有互连线充当字线和位线,并通过TSV连接到底层的外围电路[13];本文依据第二种堆叠方式建立了图2所示的3D SRAM电路模型。

图2 3D SRAM电路模型Fig.2 3D SRAM model

分析电路结构可知,TSV的开路故障既可以发生在字线上,也可以发生在位线上,且均位于TSV互连线上。根据电路结构对称性特点以及TSV开路故障的随机性,可以将TSV开路故障的植入位置定位在四个地方(Df1~Df4)。由于存储单元以阵列形式布放,字线和位线分别位于不同的边,TSV也是按顺序布放,相对位置都是对称的,所以这四处开路故障位置足以表征整个3D SRAM中的所有TSV开路故障情况。

1.3 TSV开路故障模拟

将TSV开路故障逐一注入图2故障位置中,采用图1所示TSV开路故障耦合效应电学模型,并用Hspice进行模拟。模拟环境设置为:65 nm工艺,1.2 V电源电压,常温(25℃),典型corner(TT)。故障位置、操作类型、最小开路电阻值以及最大失效概率阻值整理如表1所示,TSV开路引起的SRAM失效在考虑工艺偏差情况下的最大失效率用Fmc来表示。

表1 TSV开路导致3D SRAM失效的最小电阻值

表1中,定义Dfi-nom为在标称条件下导致SRAM失效的TSV最小开路电阻值;定义最大失效概率阻值Dfi为在考虑工艺偏差时,导致SRAM最大概率(100%)出现功能故障的TSV开路最小电阻值。

对应的曲线图如图3所示,图中横坐标为TSV开路电阻的相对最小阻值(Dfi-rel),由式(1)获得;纵坐标为SRAM失效率,最大值为100%。

(1)

图3 3D SRAM失效率随TSV开路电阻变化Fig.3 3D SRAM failure probability change under TSV open-circuit resistance

通过图3中曲线数据可得出如下结论:

在考虑工艺偏差的情况下:

1)当注入故障位置的开路电阻阻值等于该故障位置在标称条件下最小可探测开路电阻值时,引起的存储器失效概率大约在40%~60%之间(即Dfi-rel=1)。换句话说,在标称条件下,TSV存在开路故障时会导致存储器产生故障行为的最小可探测值,在考虑工艺偏差对电路影响的情况下,失效率不到60%。

2)随着TSV开路电阻值的增加,存储器的失效率也随之升高。从图3中还可以看到,当Dfi-rel处在0.5~1.5之间时,TSV的开路电阻只有小幅增加,但由此引起的存储器失效率却呈直线上升,最高达到100%。这说明当考虑工艺偏差对电路的影响时,TSV的开路故障对存储器功能故障的影响更严重。

3)对于Df1处开路故障位置,最小开路电阻值是标称条件下TSV开路电阻值的3.0倍(B_WL),即Dfi-rel=3.0;相应地,对于Df2处开路故障位置,最小开路电阻值是标称条件下TSV开路电阻值的2.5倍(M_WL),即Dfi-rel=2.5;对于Df3处开路故障位置,最小开路电阻值是标称条件下TSV开路电阻值的1.5倍(B_BL_W),即Dfi-rel=1.5;对于Df4处开路故障位置,最小开路电阻值是标称条件下TSV开路电阻值的2.0倍(M_BL_S_R),即Dfi-rel=2.0。

除此之外,本小节还分别对字线和位线的操作类型以及开路位置进行广泛的模拟研究,模拟结果如表2所示。

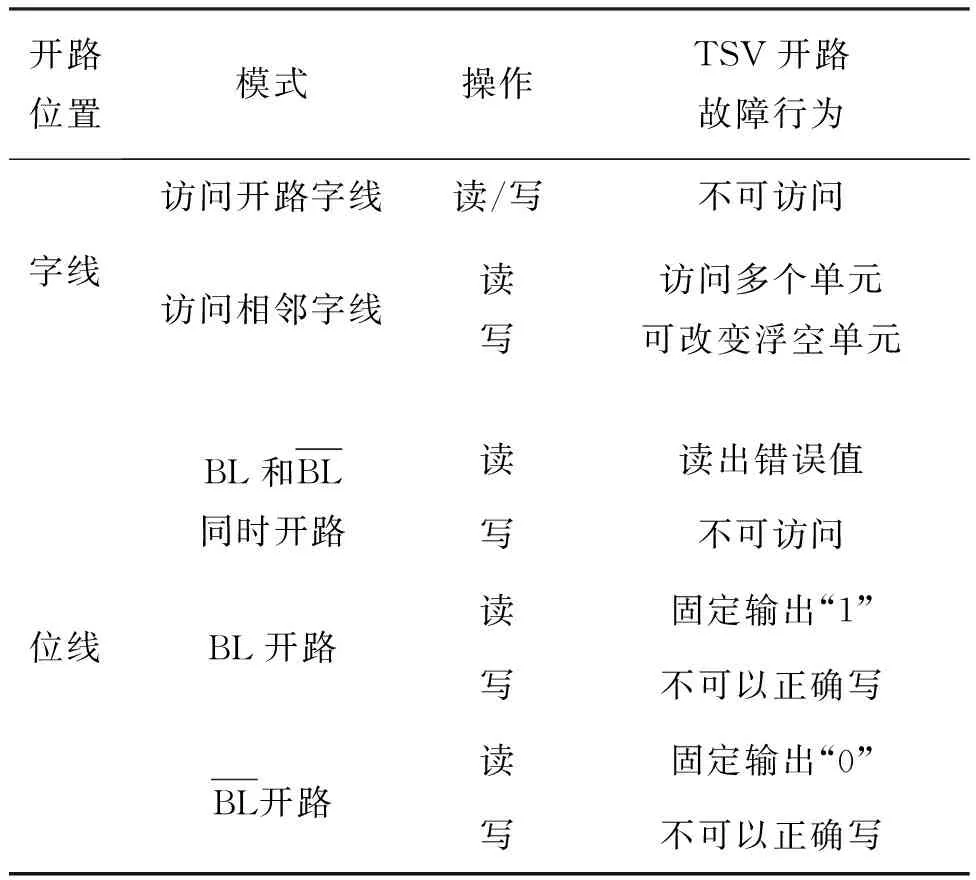

表2 3D SRAM中TSV开路故障行为

字线TSV存在开路故障时,存储器所对应的故障行为主要有三类,即“不可访问”“访问多个单元”以及“可以改变浮空单元里的值”。位线TSV存在开路故障时,存储器所对应的故障行为有四类,分两种情况:当两根位线同时开路时,故障行为有“读出错误值”和“不可访问”两类,当其中某一根位线开路时,故障行为有“不可以正确写”和“固定输出0或1”两类。

2 故障原语及TSV开路测试算法

2.1 故障原语定义

功能故障检测的两个基本组成部分为:读写操作序列以及相应单元的状态变化。因此,3D SRAM中每一种TSV开路故障的单一单元故障原语可采用S,F,R的组合来表示存储器的故障行为;多单元故障用

2.2 故障行为与March元素

访问多个单元故障行为,普通的测试算法就可以检测到。针对访问多个单元故障的最简化March元素为:(r0,w1)或(r1,w0),其中“”为地址增序,“”为地址降序。

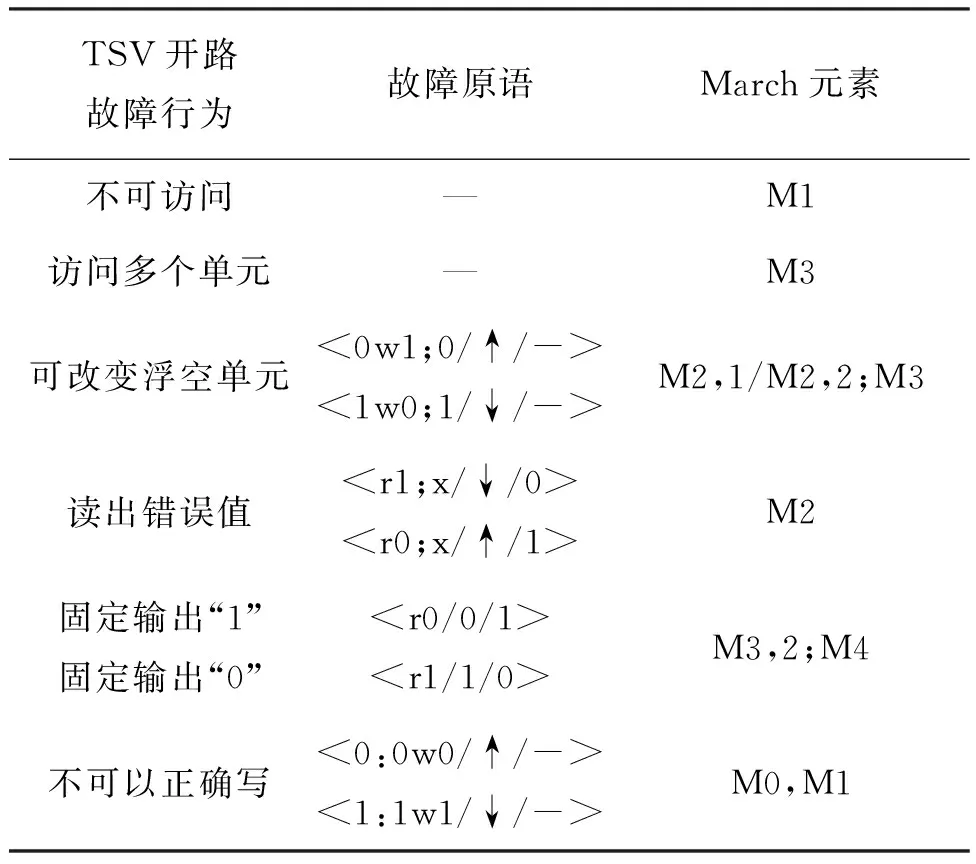

因此,根据前述3D SRAM中每一种TSV开路故障行为的故障原语定义,可以得到3D SRAM中TSV开路故障的故障原语及其March元素,结果如表3所示。

表3 TSV开路故障的故障原语及其March元素

2.3 TSV开路测试算法

表3中所提的这些基本故障类型的March元素可以为本节TSV开路测试算法的研究提供基础,通过对所有测试序列进行算法合并与优化,从而得到符合设计要求的测试算法。经合并优化之后的算法如式(2)所示:

① ②③ ④⑤⑥ ⑦⑧ ⑨

(2)

M0 M1 M2 M3 M4

此算法共九个操作步骤,分为五个状态,分别为①~⑨九个操作步骤和M0~ M4五个状态:

M0:存储单元初始化为状态“1”;

M1:按地址增序对所有存储单元进行w1和r1的操作;

M2:按地址降序对所有存储单元进行r1,w0和r0的操作;

M3:按地址降序对所有存储单元进行r0和w1的操作;

M4:按地址增序对所有存储单元进行r1操作。

式(2)检测故障的原理总结如表4所示。

表4 TSV开路故障及其March元素检测原理

表4中March元素列,Mi表示测试算法中对第i个March元素,Mi,j表示测试算法中第i个March元素的第j个操作,如M2,2表示第2个March元素中的第2步操作“w0”。

3 TSV开路测试算法实现与验证

前面已经从理论上推导出了TSV开路故障的测试算法,本节将根据以上研究成果实现具体的TSV开路测试算法,并验证提出的TSV测试算法的正确性和有效性。

3.1 算法代码实现

TSV开路测试算法共五个状态,本文采用Verilog语言实现TSV测试算法有限状态机的设计,算法的伪代码描述如算法1所示。

算法1 TSV开路测试算法有限状态机

完成整个TSV测试算法需要9×N个循环,因此所有数据完成读写操作所需的总时间为9×N×D,其中N为地址深度,D为数据位宽。

3.2 算法电路实现

本文所提测试算法的一大优势就是可以采用2D的测试方法来完成TSV开路故障的测试,所以该算法的测试电路依然可以采用典型的BIST测试电路,如图4所示。

图4 BIST测试电路Fig.4 BIST test circuit

系统工作流程如图5所示。

图5 系统工作流程Fig.5 Systematic work flow

当进入BIST模式时,外部控制信号BIST_start有效,系统进入测试模式,多路选择器MUX将选择从FSM控制器中产生的数据作为系统输入,存储器输出的数据被送到输出响应比较器,与BIST控制器产生的理想数据进行比对,进而判断存储器是否存在故障,如果存在故障,输出响应器的故障标志位有效,并向冗余修复模块发送故障地址和故障类型,便于后续修复工作。最后,当FSM状态控制器根据算法步骤完成所有测试步骤后,BIST_done信号有效,表示存储器完成了自测试。

当BIST_start无效时,系统进入正常的功能模式,多路选择器MUX将选择从System_in输入的数据作为系统输入,System_in和System_out有效,如果有错误单元,系统将按照重新分配的新地址进行数据存储,并由System_out输出。

3.3 算法验证

本文采用Verilog和Nanosim仿真工具,对3D SRAM进行测试。仿真中加入TSV开路故障模型,通过观察字线开路和位线开路在TSV开路测试算法中的测试情况,分析了TSV开路测试算法的有效性及正确性。

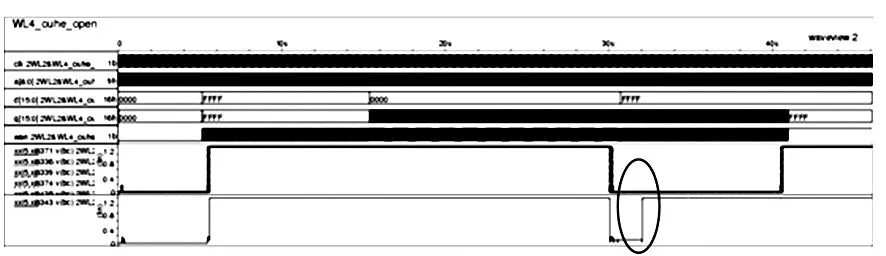

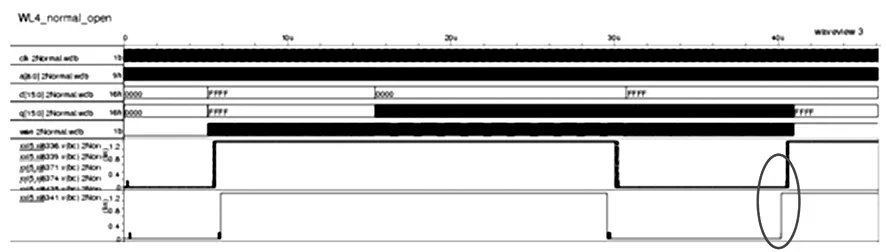

字线TSV存在开路故障的模拟结果如图6所示(模拟的是WL2和WL4)。

(a) 注入故障(a) With fault injection

(b) 未注入故障(b) Without fault injection图6 字线TSV注入开路故障模拟结果Fig.6 Result of open-circuit fault injection on word line

图6中,椭圆为TSV测试算法中的某一步写操作。从图6(b)中椭圆可以看出,WL2和WL4上所接单元都在期望的时间点上写入了正确的数据,而图6(a)椭圆中的波形明显不同步,这是由于WL4所接的TSV产生了开路故障,在WL4期望的访问时间点上并没有成功写入数据,且在访问WL2的时候,由于耦合效应,与WL2的写操作同步了,所以在WL2写操作的同时,WL4也进行了相同的写操作。

类似地,可以得到位线的模拟验证结果。首先往任意一根与图2中BL相连的位线TSV中注入开路故障,模拟结果如图7所示。

图7 位线TSV注入开路故障模拟结果Fig.7 Result of open-circuit fault injection on bit line

对于普通字线和普通位线的模拟结果可以采用类似的方法得到,整理结果如表5所示。

表5 开路故障类型统计

4 结论

针对绑定后3D SRAM中TSV的全开路故障展开全面分析,提出一种使用测试算法来探测TSV开路故障的方法。该方法将TSV测试机制与Memory BIST结构相结合,可以在不使用TSV专用测试电路且不增加额外面积开销的情况下解决3D SRAM中TSV的开路测试。模拟结果表明,该TSV测试算法功能正确,能够准确探测到TSV的开路故障,并快速定位TSV的开路位置,实现了探测TSV开路故障的目的。

References)

[1] Koyanagi M, Fukushima T, Tanaka T. Three-dimensional integration technology and integrated systems[C]//Proceedings of Asia South Pacific Design Automation Conference, Asp-Dac 2009, Yokohama, Japan, 2009: 409-415.

[2] Khan N, Rao V S, Lim S, et al. Development of 3-D silicon module with TSV for system in packaging[J]. IEEE Transactions on Electronic Components and Packaging Technologies, 2010, 33(1): 3-9.

[3] Gong S Q, Liu W, Tan J B, et al. Foundry TSV integration and manufacturing challenges[C]//Proceedings of IEEE International Interconnect Technology Conference / Advanced Metallization Conference, 2014: 385-388.

[4] Swinnen B, Ruythooren W, De Moor P, et al. 3D integration by Cu-Cu thermo-compression bonding of extremely thinned bulk-Si die containing 10μm pitch through-Si vias[C]//Proceedings of Electron Devices Meeting, 2006: 1-4.

[5] Huang Y J, Li J F, Chou C W. Post-bond test techniques for TSVs with crosstalk faults in 3D ICs[C]//Proceedings of International Symposium on VLSI Design, Automation, and Test (VLSI-DAT), 2012: 1-4.

[6] Pasca V, Anghel L, Benabdenbi M. Configurable Thru-Silicon-Via interconnect Built-In Self-Test and diagnosis[C]// Proceedings of Test Workshop, 2011: 1-6.

[7] Lin Y H, Huang S Y, Tsai K H, et al. Parametric delay test of post-bond through-silicon vias in 3-D ICs via variable output thresholding analysis[J]. IEEE Transactions on Computer-Aided Design of Integrated Circuits and Systems, 2013, 32(5): 737-747.

[8] Cuviello M, Dey S, Bai X, et al. Fault modeling and simulation for crosstalk in system-on-chip interconnects[C]//Proceedings of IEEE/ACM International Conference on Computer-aided Design, 1999: 297-303.

[9] Yoon K, Kim G, Lee W, et al. Modeling and analysis of coupling between TSVs, metal and RDL interconnects in TSV-based 3D IC with silicon interposer [C] //Proceedings of the 11th Electronics Packaging Technology Conference. Los Alamitos: IEEE Computer Society Press, 2009: 702-706.

[10] Kim J, Cho J, Kim J. TSV modeling and noise coupling in 3D IC[C]//Proceedings of Electronic System-Integration Technology Conference, 2010: 1-6.

[11] 贺翔.面向三维集成的硅通孔互连信号完整性与电气建模研究[D].南京:南京航空航天大学, 2012.

HE Xiang. Signal integrity analysis and electrically modeling of through silicon via connection in 3D integration[D]. Nanjing: Nanjing University of Aeronautics and Astronautics, 2012. (in Chinese)

[12] Woo D, Seong N, Lewis D, et al. An optimized 3D-stacked memory architecture by exploiting excessive, high-density TSV bandwidth [C]//Proceedings of IEEE 16th International Symposium on High Performance Computer Architecture (HPCA), 2010: 1-12.

[13] Loh G H. 3D-stacked memory architectures for multi-core processors[C]//Proceedings of International Symposium on Computer Architecture. IEEE, 2008: 453-464.

Research and implementation of TSV open test algorithm in 3D SRAM

ZHAO Zhenyu, DENG Quan, LI Peng, JIANG Jianfeng, QU Lianhua, TANG Haoyue

(College of Computer, National University of Defense Technology, Changsha 410073, China)

In 3D-IC (three dimensional-integrated circuit) technology based 3D SRAM(three-dimensional static random access memory), a large number of TSVs (through silicon vias) have been implemented in circuits. The manufacturing process of TSV is not mature,which makes TSVs more prone to open defects and brings new challenges to the 3D SRAM test. The existing method of TSV test can find out where the faults are, but it needs extra specific circuit to implement, which increases both the area overhead and its design complexity. In consideration of what was discussed above, a new idea to detect the open defects of TSV based on a test algorithm was proposed. It proved to be an effective method to detect the open defects of TSV in 3D SRAM using BIST(built-in self test) without any extra overhead. Results show that the proposed method has no functional problem with the algorithm and it can realize the purpose of TSV open fault detection.

three dimensional-integrated circuit; through silicon via; open defects; test; algorithm

10.11887/j.cn.201605002

http://journal.nudt.edu.cn

2015-05-30

国家自然科学基金资助项目(61176030,61272139)

赵振宇(1973—),男,辽宁朝阳人,教授,博士,硕士生导师,E-mail:zyzhao@nudt.edu.cn

TN47

A

1001-2486(2016)05-007-07