65 nm工艺双层三维静态存储器的软错误分析与评估*

李 鹏,郭 维,赵振宇,张民选,2,邓 全,周宏伟

(1.国防科技大学 计算机学院, 湖南 长沙 410073;2.国防科技大学 并行与分布处理国家重点实验室, 湖南 长沙 410073)

65 nm工艺双层三维静态存储器的软错误分析与评估*

李 鹏1,郭 维1,赵振宇1,张民选1,2,邓 全1,周宏伟1

(1.国防科技大学 计算机学院, 湖南 长沙 410073;2.国防科技大学 并行与分布处理国家重点实验室, 湖南 长沙 410073)

新兴的三维静态存储器将代替二维静态存储器被广泛用于高性能微处理器中,但它依然会受到软错误的危害。为了能够快速、自动分析多层管芯堆叠结构的三维静态存储器软错误特性,搭建了三维静态存储器软错误分析平台。利用该平台对以字线划分设计的三维静态存储器和同等规模的二维静态存储器分别进行软错误分析,并对分析结果进行对比。研究结果表明二维和三维静态存储器的翻转截面几乎相同,但三维静态存储器单个字中发生的软错误要比二维静态存储器更严重,导致难以使用纠检错技术对其进行加固。静态模式下二维和三维静态存储器敏感节点均分布于存储阵列中,表明静态模式下逻辑电路不会引发软错误。

三维静态存储器;软错误;分析平台;翻转截面;单粒子翻转;多位翻转

基于三维集成电路(Three-Dimensional Integrated Circuit,3D IC)技术的三维静态存储器(Three-Dimensional Static Random Access Memory, 3D SRAM)满足了传统SRAM设计在大规模、高带宽、高速访存等方面的需求。3D SRAM把传统SRAM划分到多个管芯中,有效减小了芯片面积,还使用硅通孔(Through-Silicon-Via, TSV)作为垂直互连,消除了二维设计中长互连线带来的延迟恶化问题[1]。并且3D SRAM中长互连线的减短还可以降低位线负载过大带来的功耗[2]。

但3D SRAM依然面临着辐照导致的软错误问题,特别是当3D SRAM应用于辐照环境中时,单粒子轰击产生单粒子瞬态(Single Event Transient, SET)和单粒子翻转(Single Event Upset, SEU)[3-4],导致其不能正常工作。已有研究表明,单粒子会穿过3D IC多层管芯结构,并且在每层管芯上都会引起SET和SEU[5-6]。3D SRAM的多层结构使得软错误的产生与传播更加复杂,导致软错误分析越加困难,进而使3D SRAM加固设计也难以展开。目前,国内外均尚未开展3D SRAM的软错误研究工作。因此,分析和研究3D SRAM的软错误特性十分必要。

目前的软错误分析手段主要包括:实时实验,粒子加速器实验和模拟实验[7]。其中模拟实验同另外两种手段相比无须实验芯片,只需要获取芯片信息和辐照粒子的物理特性行为描述,就可以快速模拟得到软错误特性。因此模拟实验虽然精度有限,但花费小、速度快,非常适合于芯片设计阶段的软错误特性分析。

Roche等基于蒙特卡洛模拟搭建集成电路辐照可靠性模拟平台TIARA(Tool Suite for Radiation Reliability Assessment)[8],TIARA可以评估各种小尺寸工艺下的集成电路软错误特性。文献[9]通过集成粒子传输代码和器件模拟器,搭建了评估中子引发软错误的代码系统,并成功应用于65 nm,45 nm和32 nm工艺集成电路的辐照评估。但这些平台和代码系统都是针对传统的二维集成电路开发的,不能用于3D IC的辐照特性分析与评估。

1 软错误分析平台搭建

1.1 3D SRAM软错误分析平台框架

3D SRAM软错误分析平台(3D SRAM Soft Error Analysis Platform, 3D SRAM-SEAP)涉及电路网表与版图信息的处理与分析、3D SRAM模型建立、轰击粒子信息获取、激励电流源加载、模拟环境设置、模拟脚本生成、粒子轰击模拟、数据处理与分析,包括了版图分析工具Calibre、建模与蒙特卡洛模拟工具Geant4、器件模拟工具TCAD、电路级模拟工具Nanosim、数据处理工具ROOT 和脚本工具Shell、Perl,最终获得3D SRAM的翻转截面、多位翻转(Multi Bit Upset, MBU)特性以及敏感部件(节点)分布。3DSRAM-SEAP的框架如图1所示。

图1 3D SRAM-SEAP 框架示意图Fig.1 Frame schematic of 3D SRAM-SEAP

根据上述的框架结果开发设计3D SRAM-SEAP。此分析平台可进行大量随机轰击模拟,通过对多次随机模拟结果的统计和分析获得3D SRAM的翻转截面和敏感部件分布。为了更加贴近实际情况,此平台中的粒子轰击位置都是随机的,并且轰击粒子种类和入射能量以及入射角度都是可以设置的,这样使得3D SRAM-SEAP的结果更加接近于实时实验和粒子加速器实验。

3D SRAM-SEAP的输入包括3D SRAM的堆叠结构、电路网表、版图信息、入射粒子信息(入射粒子种类、初始能量、影响范围等)以及随机模拟次数。下面介绍3D SRAM-SEAP的基本工作流程。

首先,根据3D SRAM的堆叠结构、版图尺寸和所使用工艺的信息,在Geant4模拟工具中建立3D SRAM的简洁模型[5],例如图2给出的65 nm 双层管芯堆叠的SRAM在Geant4中构建的模型,表1给出了各层材料和厚度信息。利用Geant4模拟得到粒子在器件层中的轰击位置、能量、角度等信息[10]。之后根据轰击位置信息,并结合版图信息和轰击影响半径,经过计算得到被轰击影响的所有器件列表。

图2 双层die堆叠3D SRAM的Geant4模型Fig.2 Geant4 model of dual-layer 3D SRAM

表1 模型中单个die的各层信息

然后,利用电路级模拟工具Nanosim进行电路级模拟,模拟中对已得到的粒子轰击影响范围内器件的漏极加入激励电流源,以此来模拟辐照粒子轰击时器件漏极产生的瞬态电流[11]。使用从计算机辅助工艺设计(Technology Computer Aided Design, TCAD)器件模拟中提取的分段线性(Piece Wise Linear,PWL)电流源来表征粒子轰击产生的瞬态电流[12]。为了满足对不同器件和线性能量传输(Linear Energy Transfer, LET)值采用相应激励电流源的需求,建立PWL电流源查找表。然后利用Nanosim进行电路行为模拟,并自动把错误信息输出到指定文件中。

最后,集中每次模拟中得到的软错误信息数据,根据制定的软错误评估体系,利用相关脚本得到相应的数据。

除输入信息之外,3D SRAM-SEAP中的单粒子轰击影响半径、轰击次数等参数需要设定,测试模式需要指定,同时还要根据不同辐照环境和集成电路工艺要求来配置PWL电流源查找表。

1.2 评估体系制定

当前对SRAM的评估都集中在翻转截面上,即SRAM发生软错误的概率[13]。除此之外,深亚微米下电荷共享导致的多单元翻转(Multi Cell Upset, MCU)和MBU越来越严重,使得已有SRAM加固设计失效。其中MCU是指一次轰击中SRAM整体产生的多个翻转,MBU是指一次轰击中单个字中产生的多个翻转。所以当前的3D SRAM必须包括对其中产生的MCU和MBU进行分析与研究。为了得到3D SRAM的敏感部位,还需对引发软错误的轰击点进行定位,并从大量模拟中找到导致翻转的轰击节点位置。综合考虑上述SRAM软错误分析的需要,最终选择将以下几个作为3D SRAM辐照特性的研究对象。

1.2.1 翻转截面

翻转截面又包括总翻转截面,单个单元翻转(Single Cell Upset, SCU)截面和MCU翻转截面。翻转截面的计算方法如式(1)所示,其中σ为翻转截面,N1是产生翻转的轰击次数,N为总的轰击次数,S为SRAM的面积。

(1)

1.2.2 单个字中SCU总数(TNMBU)

单个字中的SCU总数是指一个字中发生翻转的位的总数,它用于评估MBU。TNMBU越大,说明3D SRAM被轰击后会产生越严重的MBU,则此时简单的错误纠正编码(Error Correction Codes, ECC)技术就会失效,并且利用ECC编码技术对此3D SRAM进行加固也越加困难。同样,TNMBU信息也从sim.err文件中获取。根据错误产生时间和输入激励,计算产生翻转的字的序号,再根据sim.err中产生错误的输出端口序号可得到产生翻转的位序号。进而可以得到每个字中产生SCU的数量。

1.2.3 单个字中最多相邻翻转数量(MNMBU)

此分析平台中另一个评估MBU特性的量就是一个字中最多相邻错误的个数。文献[14]中提到对于ECC编码,探测和纠正多个错误时,需要借助相邻位的信息进行验证,如果相邻位均发生错误,则给ECC加固技术带来了更大的难题。MNMBU的获取方法同TNMBU相类似,从sim.err文件中得到单个字产生的错误信息后,再判断产生SCU位的序号是否相连,得到最多相连个数即可。

1.2.4 敏感节点分布

敏感节点分布即指导致3D SRAM发生软错误的轰击粒子在其版图中的位置集合。从敏感节点的分布中可以找到3D SRAM中最为敏感的部位,针对敏感部位进行重点加固,可使加固设计事半功倍,得到更好的加固效果。某次轰击产生软错误后,立即追溯此次轰击模拟中加载的轰击位置,并且3D SRAM版图中标出此位置。

确定软错误特性评估体系后,编写Perl和Shell脚本从每次电路级轰击模拟得到的sim.err文件中提取相关数据,再经脚本统计、分析处理后即能得到上述的各个评价指标。

2 2D SRAM和3D SRAM结构

为了更好地分析3D SRAM的软错误特性,将利用3D SRAM-SEAP分析同样容量的2D SRAM和3D SRAM,其中3D SRAM采用了字线划分的设计方法。通过对比分析两者的软错误特性,得到3D SRAM软错误特性有别于2D SRAM的特点。

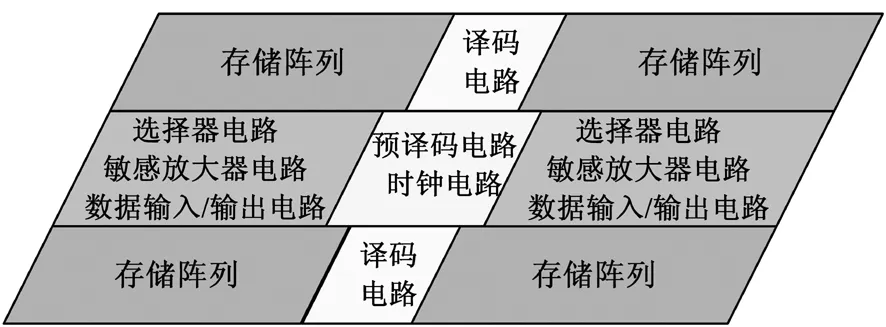

首先,基于某商用65 nm工艺,使用Memory Compiler工具生成一款存储规模为256字×16位的2D SRAM。此款2D SRAM的版图成矩形,其面积为191.18 μm×82.39 μm。图3给出了此款2D SRAM版图结构的示意图。从图3中可以看到其存储阵列被分为4个块(bank),分别被放置于版图的四个顶角,版图中间的“十字”位置上放置了逻辑电路,包括时钟电路、译码电路、敏感放大器电路和数据输入输出电路。此款2D SRAM还使用了位交叉技术,交叉位数为8,由于位交叉技术拉开同一个字中相邻单元的距离,因此可以有效降低MBU。

图3 2D SRAM版图示意图Fig.3 Layout configuration of 2D SRAM

3D SRAM是把2D SRAM以字线划分方式从中间切开堆叠而成的,并在一侧加入垂直互连硅通孔(Through-Silicon-Via, TSV),使得两层管芯可以进行信号传递。3D SRAM的版图结构如图4所示。因为3D SRAM版图中TSV部分不含有器件,不会产生软错误,所以轰击模拟中不会轰击此部分版图,故3D SRAM单层有效面积为95.59 μm×82.39 μm。

图4 3D SRAM版图示意图Fig.4 Layout configuration of 3D SRAM

3 分析结果评估

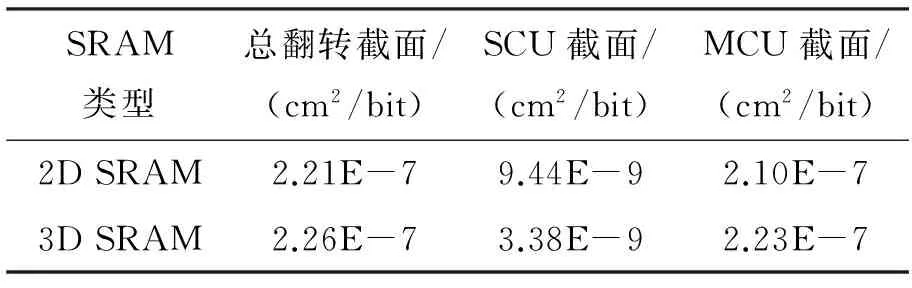

表2和表3给出了不同测试模式下3D SRAM和2D SRAM的SCU和MCU截面,从ROOT记录数据中可知,本次模拟中粒子入射器件层时LET值在40 MeV·mg-1·cm-2左右,并且PWL查找表中加入的PWL电流源也是在LET=40 MeV·mg-1·cm-2条件下的模拟中得到的。文献[14]中给出了LET为40 MeV·mg-1·cm-2时的翻转截面为2×10-8cm2/bit,而3D SRAM-SEAP得到的2D SRAM的翻转截面约为2×10-7cm2/bit。相差一个数量级的原因是文献中使用的质子,而本文使用的是重离子Kr,重离子比质子电离电荷的数量多,因此更容易产生单粒子效应(Single Event Effect, SEE)。除去此因素,两者较为接近,可以证明3D SRAM-SEAP的准确性。

表2 全0静态测试中翻转截面

表3 全1静态测试中翻转截面

从数据上来看,2D和3D SRAM中SCU 截面均远小于MCU截面,这是因为本分析平台把轰击半径设定为1 μm,在1 μm内的器件上均加入激励电流源,因此每次轰击多个器件会产生SET,特别是轰击存储阵列时,轰击范围会覆盖多个存储单元,使得多个存储单元同时发生SEU,因而更容易产生MCU,此点会在下面的敏感节点分布中被更加清晰地看到。

从2D和3D SRAM的翻转截面数据对比来看,3D SRAM和2D SRAM的几乎相同。一方面3D SRAM虽然进行了两层堆叠,但存储单元数量和面积没有变,从翻转截面计算公式来看,它和SRAM的结构没有关系,而是和轰击次数以及产生SEU的次数有关;另一方面,3D SRAM中die1和die2中的存储阵列在垂直方向上是完全重合的,因此在垂直轰击的条件下,粒子入射到存储阵列的概率是相同的,因此两者的翻转截面也相同。结果中的少许差别是因为轰击粒子在3D SRAM中不完全以直线传播,发生了些许偏差,使得3D SRAM中轰击到存储阵列的概率略大。

2D SRAM的TNMBU和MNMBU均为1,说明2D SRAM中一个字中最多只会出现1个SCU。而3D SRAM的TNMBU和MNMBU均为2,说明3D SRAM中一个字则可能出现2个SCU,并且这2个SCU可能相邻。对于2D SRAM,采用8位交叉技术可以有效避免MBU的发生。但对于3D SRAM,虽然使用了8位交叉技术但依然会产生2位相邻的MBU。这是因为此款3D SRAM中同一个字的高8位和低8位分别位于die1和die2,并且在同一垂直方向上。因此粒子轰击时,一个字的高8位与低8位可能同时发生翻转,其TNMBU是2D SRAM的2倍,并且如果低8位中最高位发生翻转,而高8位中最低位产生翻转,则就会产生2位相邻SCU。综上所述,由于3D SRAM会产生2位相邻的MBU,因此难以采用ECC技术对其进行加固设计。

从分析结果中发现全0和全1测试方案下,敏感节点分布情况相同。图5给出了全0静态模式下,引发不同翻转数量的敏感节点在2D SRAM和3D SRAM版图中的分布。图5中不同灰度的点代表引起不同翻转数量的轰击位置。从敏感节点分布图中还可以看到2D SRAM中最多出现10位的MBU,而3D SRAM中最多出现了20位的MBU,这表明3D SRAM产生的MBU比2D SRAM产生的更加恶劣。

(a) 2D SRAM中敏感节点分布(a) Sensitive node distributions in 2D SRAM

(b) 3D SRAM中敏感节点分布(b) Sensitive node distributions in 3D SRAM图5 两种SRAM中敏感节点分布Fig.5 Sensitive node distributions in both 2D SRAM and 3D SRAM

对于2D SRAM而言,所有导致软错误的轰击位置均集中在存储阵列上,并且导致1个SCU的敏感节点都分布在存储阵列的边界上。这说明在静态模式下,SRAM只有存储阵列是敏感的,轰击组合逻辑不会导致软错误。这是因为存储单元在任何工作时刻都是敏感的,而组合逻辑在静态模式下即使轰击后产生SET,但SET不会沿着路径传播而导致软错误。导致较少数量SCU的敏感节点均分布在存储阵列边界,这是因为当粒子轰击存储阵列边界时,其敏感范围只会覆盖一小部分存储单元,其余覆盖的是逻辑电路,而逻辑电路不会导致SCU,因此只有其覆盖的存储单元发生了SCU。

对于3D SRAM而言,由于其面积只有2D SRAM的一半,并且轰击的粒子数量相同,故其敏感节点要比2D SRAM的更为密集。3D SRAM的敏感节点分布基本同2D SRAM的相同,不同的是导致数量较少SCU的敏感节点落入到了组合逻辑中。通过检查模拟结果,发现导致此种情况的原因有以下两个:①粒子轰击在die1的逻辑电路中,与材料原子核发生碰撞发生极大偏转,轰击到die2的存储阵列中导致了SEU;②粒子与材料碰撞发生核反应发出次粒子,主级粒子轰击逻辑电路,而次级粒子轰击存储阵列导致了SEU。

4 结论

针对3D SRAM的多层堆叠结构搭建了3D SRAM软错误分析平台。此平台通过大量随机电路级轰击模拟,得到了多种翻转截面、单字中MBU信息以及敏感节点分布,利用这些参数可以对其软错误特性进行分析。根据分析结果可以指导3D SRAM加固设计。使用此3D SRAM软错误分析平台对规模相同的2D SRAM和3D SRAM进行了分析,其中3D SRAM采用字线划分设计。分析结果表明3D SRAM和 2D SRAM的翻转截面几乎相同,但3D SRAM一个字中最多翻转数量和最多相邻翻转数量均是2D SRAM的两倍,说明3D SRAM比2D SRAM更加难以用ECC技术进行加固。在静态模式下,2D 和3D SRAM的敏感节点均分布于存储阵列中,因此,SRAM的逻辑电路不会导致软错误。

References)

[1] Puttaswamy K, Loh G H. 3D-integrated SRAM components for high-performance microprocessors [J]. IEEE Transactions on Computers, 2009, 58(10): 1369-1381.

[2] Hsu C L, Wu C F. High-performance 3D-SRAM architecture design[C]//Proceedings of 2010 Asia Pacific Conference on IEEE, 2010: 907-910.

[3] Chen J J, Chen S M, He Y B, et al. Novel layout technique for single-event transient mitigation using dummy transistor[J]. IEEE Transactions on Device & Materials Reliability, 2013, 13(1): 177-184.

[4] Chen J J, Chen S M, He Y B, et al. Novel layout techniques forn-hit single-event transient mitigation via the source-extension [J]. IEEE Transactions on Nuclear Science, 2012, 59(6): 2859-2866.

[5] Gouker P M, Tyrrell B, D′Onofrio R, et al. Radiation effects in 3D integrated SOI SRAM circuits [J]. IEEE Transactions on Nuclear Science, 2011, 58(6): 2845-2854.

[6] Gouker P M, Tyrrell B, Renzi M, et al. SET characterization in logic circuits fabricated in a 3D IC technology [J]. IEEE Transactions on Nuclear Science, 2011, 58(6): 2555-2562.

[7] Tsiligiannis G, Dilillo L, Bosio A, et al. 90 nm SRAM static and dynamic mode real-time testing at concordia station in antarctica [J]. IEEE Transactions on Nuclear Science, 2014, 61(6): 3389-3394.

[8] Roche P, Gasiot G, Autran J L, et al. Application of the TIARA radiation transport tool to single event effects simulation[J]. IEEE Transactions on Nuclear Science, 2014, 61(3): 1498-1500.

[9] Abe S, Watanabe Y, Shibano N, et al. Multi-scale Monte Carlo simulation of soft errors using PHITS-HyENEXSS code system[J]. IEEE Transactions on Nuclear Science, 2012, 59(4): 965-970.

[10] Huang P, Chen S M, Chen J, et al. Single event pulse broadening after narrowing effect in nano CMOS logic circuits[J]. IEEE Transactions on Device and Materials Reliability, 2014, 14(3): 849-856.

[11] Touré G, Hubert G, Castellani-Coulié K. Simulation of single and multi-node collection: impact on SEU occurrence in nanometric SRAM cells[J]. IEEE Transactions on Nuclear Science, 2011, 58(3): 862-869.

[12] 刘必慰.集成电路单粒子效应建模与加固方法研究[D].长沙: 国防科学技术大学, 2008.

LIU Biwei. Modeling and hardening of single event effect in integrate circuit [D].Changsha: National University of Defense Technology, 2008.(in Chinese)

[13] Gorbunov M S, Vasilegin B V, Antonov A A, et al. Analysis of SOI CMOS microprocessor′s see sensitivity: correlation of the results obtained by different test methods [J]. IEEE Transactions on Nuclear Science, 2012,59(4): 1130-1135.

[14] Gorbunov M S, Dolotov P S, Antonov A A, et al. Design of 65 nm CMOS SRAM for space applications: a comparative study [J]. IEEE Transactions on Nuclear Science, 2014, 61(4): 1575-1582.

Soft error analysis and evaluation of dual-layer 3D SRAM based on 65 nm technology

LI Peng1, GUO Wei1, ZHAO Zhenyu1, ZHANG Minxuan1,2, DENG Quan1, ZHOU Hongwei1

(1.College of Computer, National University of Defense Technology, Changsha 410073, China;2. National Key Laboratory for Parallel and Distributed Processing, National University of Defense Technology, Changsha 410073, China)

The 3D SRAM (three-dimensional static random access memory) will take the place of 2D SRAM (two-dimensional static random access memory), and will be widely used in high performance microprocessor. However, 3D SRAM still suffers from the dangers of soft error. A novel 3D SRAM soft error analysis platform was designed for studying the soft error characteristic of 3D SRAM. The soft error characteristic of the designed 3D SRAM and the original 2D SRAM were analyzed by using our designed platform. It is found that 3D SRAM and 2D SRAM have the same upset cross section, but the soft error of 3D SRAM is more serious than that of 2D SRAM, which makes it difficult to harden 3D SRAM by using error correction codes technologies. At the static test mode, the upset sensitive nodes were only distributed in the memory array of both 3D SRAM and 2D SRAM. It indicates that the logic circuit can’t induce soft error at static test mode.

three-dimensional static random access memory; soft error; analysis platform; cross section; single event upset; multi cell upset

10.11887/j.cn.201605004

http://journal.nudt.edu.cn

2015-11-11

国家自然科学基金资助项目(61373032,61303069);高等学校博士学科点专项科研基金资助项目(20124307110016)

李鹏(1986—),男,吉林吉林人,工程师,博士,E-mail:li1986p@163.com

TN386.1

A

1001-2486(2016)05-020-06