高速低功耗SRAM体系结构及设计仿真

赵以诚,周 刚

(中国电子科技集团公司第四十七研究所,沈阳110032)

高速低功耗SRAM体系结构及设计仿真

赵以诚,周刚

(中国电子科技集团公司第四十七研究所,沈阳110032)

提出了一种高速低功耗1M-bit静态随机存储器的体系结构设计,在此体系结构基础上完成了整体电路架构的搭建。同时,运用Hspice模拟电路仿真工具完成了电路系统仿真。在5V电源电压下,采用CSMC 0.35μm工艺模型,地址取数时间为15ns,平均动态功耗为100mA,静态功耗为6mA,实现了静态随机存储器高速、低功耗的良好性能。

静态随机存储器;体系结构;高速低功耗;译码器;灵敏放大器;内核

1 引 言

由于现代数字系统需要高速存储能力,因此越来越高密度的存储器设计与制造技术被人们所采用,无论是最早的独立式存储器,还是发展迅速的嵌入式存储器,在未来都是集成电路市场中持续增长的部分。

主要针对异步独立式1M-bit静态随机存储器(SRAM)的体系结构进行了细致的分析与设计。首先提出一种新型的1M-bit SRAM体系结构,然后按照这种体系结构,对整体电路进行搭建,最后完成整体电路的模拟仿真,并分析其波形结果和性能指标,总结后得出结论。

2 1M-bit位SRAM体系结构

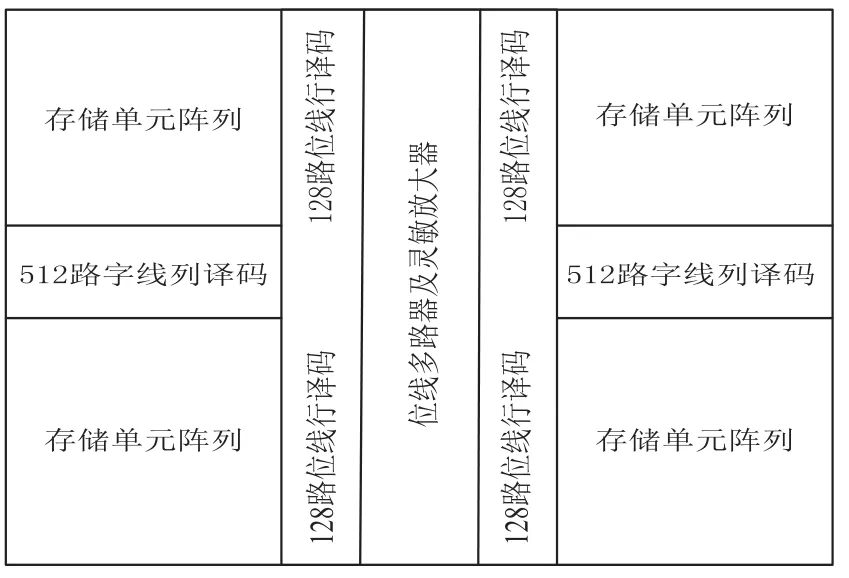

下面设计一种1M-bit SRAM体系结构,采用多层次的译码结构,如图1所示,从而更好地实现并满足静态随机存储器高速低功耗的特点。

其中包含的存储单元内核阵列是图中最大的块。512路列译码器分布在横向左右两侧,128路位线行译码分布在纵向两侧,位线多路器和灵敏放大器放置在内核阵列的中间部分。

其中列译码器由一个初级译码器和一个次级译码器组成,它用来驱动竖直方向穿过阵列的字线。而每一对位线连接一个位线行译码器,同时这个译码器连接着位线的I/O电路,一般包括灵敏放大器和写驱动器电路。所有的存储单元都在水平方向和垂直方向上镜像排列成规则阵列[1]。

该静态随机存储器的容量一共1Mbit,每次读写一个由8bit构成的字节,又由于是八位并行数据输出,所以可以写成128K×8bit。由于1M

位的存储器可以按照下面的等式计算:1Mbit=128×1024×8=27×210×8bit。

图1 存储器体系结构

所以,如果能够完成所有位的随机写读,一共需要17位的地址进行译码操作。

由于1M位SRAM容量较大,它的阵列长度和宽度过大,导致了连接存储单元的横向字线与纵向位线较长。因为金属互连导线的RC延迟与长度的平方成正比,所以整体存储器的访问时间也与阵列的宽度和高度的平方成正比[2]。同时,随着阵列的增加,大容量存储器带来的导线电容增大,会使得一次读写所消耗的功耗过大。如何实现高速低功耗的1M-bit SRAM体系结构设计,是研究的关键内容。

设计的存储器体系结构按照分块译码、列译码(字线译码)、行译码(位线译码)三个层次进行划分,最终有效实现一个字节的读写功能操作。

首先进行块译码划分。通过把存储器阵列分割成一定数量的小块,然后利用块地址译码选中需要读写的一块,如此可以显著降低横向字线的长度。另外,使用分级译码操作后,可以改善字线过长带来的电阻过大、字线开启延迟时间过长的问题[3]。

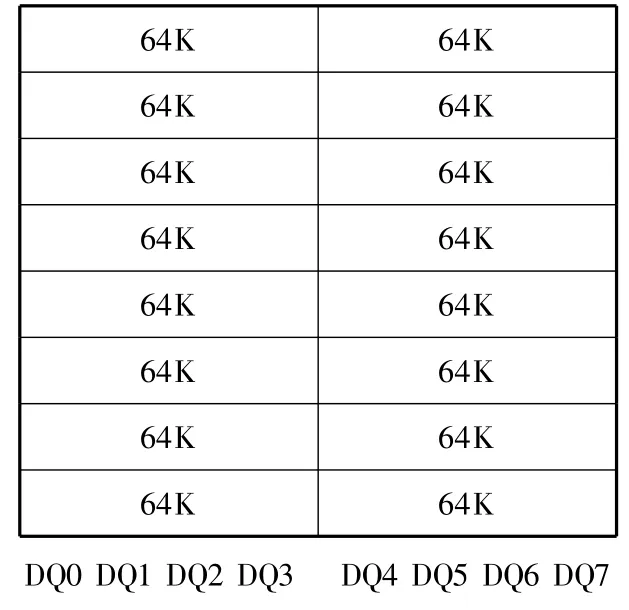

设计中将1M-bit SRAM分成八大块,每一块为128K,它由A8、A9、A11三个地址组成的三八译码器实现。接着,地址A13将每一块分成左右2小块,每一小块为64K,由此将整个存储器分成了16小块,如图2所示。

图2 分块后的SRAM阵列

经过块译码操作后,将一条竖直的长字线分成了8段。这样,每次读写时,仅在某一块中的字线被开启,使得分块后字线上的延迟比原来分块的延迟降低了64倍。

其次进行列译码(字线译码)划分。设计中的列译码实质上属于字线译码,以其中一个64K的小块为例,它在横向上一共有512列单元,也就是有512根字线[4]。

由于512=29,所以字线译码需要9个地址,设计中采用A3-A7,A12,A14-A16地址作为字线译码。

因为字线一般用多晶硅制作,并且由于分布的RC寄生参数对信号产生一定的延迟,极大影响了存储器的读写速度,而且上面的大电容也带来了额外功耗。

为了减少延迟和功耗,设计采用了一种新的SRAM字线分割技术。其核心技术在于用A3-A7,A12,A14等7个地址定义全局字线,总共产生128条全局字线[5]。这128条字线不直接驱动存储单元,因此比正常字线的电容小得多。余下的两个地址位A15、A16用于产生实际驱动单元存取管的局部字线,一共产生128×4=512根字线。

由于之前划分了8个大块并且使用局部字线对其进行存取,总单元电容减少的最大因数是8。因此,这种设计使得功耗大大减少,同时使字线上的延迟也减小,加快了存储器的读写速度。

最后进行行译码(位线译码)划分。设计中的行译码实质上属于位线译码,以64K的小块为例,它在纵向上一共有128对位线,这128对位线又分为8组,每组中包含16对位线。经过位线译码的作用,从16对位线中选中一对位线,每一对位线对应1位。如此,8组中同时被选中一对位线连接到灵敏放大器作为输出,便实现了8位输出,即一个字节的输出。

由于16=24,所以位线译码需要4个地址,设计中采用A0-A2构成3-8译码器,然后再与A10组合成4-16译码,最终选中需要读出的存储单元位线。

由于一对位线通常用金属制作,所以它的电阻相对较小,但是随着金属线变长变细,它的延迟效应不可忽略[7]。同时,连线和许多连接到它上面的平行存取管的组合电容使每条线上都有一个大的等效集总电容,因此也带来了额外功耗。

设计中首先采用地址A13将128K分成左右2小块的64K,目的就是为了将很长的位线分割成左右两部分,从而减小信号延迟。同时,每两对位线之间用电源和地的宽金属线隔离开,减小等效集总电容,如此一来也就减小了额外功耗。

总之,以上采用了分级字线、位线译码技术,形成了多层次的译码结构,使得它的字线和位线的延迟时间要减小很多,而且最大限度地节约了译码时间,降低了阵列功耗,从而实现高速低功耗的1M-bit SRAM的体系结构设计。

3 1M-bit SRAM的整体电路架构

根据以上1M-bit SRAM体系结构的论述,设计出它的具体电路架构,如图3所示。它的电路结构完全按照SRAM的体系结构进行搭建,主要包括控制电路、地址译码电路、存储单元阵列核心电路、I/O电路四部分,组成整个1M-bit SRAM的体系结构[6]。其中,A<16:0>端口为地址输入端;DQ<7:0>为数据I/O端口;NCS为片选信号;CE为使能控制信号端;NEW为读写控制信号端;NOE为I/O读控制端。

其中控制电路主要产生读写控制信号、I/O控制信号、片选使能信号,以确保电路能够正常实现功能操作。

地址译码电路由地址A<16:0>按照规律组合而成,主要包括2-4译码器,3-8译码器,4-16译码器等等。

图3 1M-bit SRAM的电路架构

I/O电路指的是输入输出电路,设计它时必须考虑到存储单元设计和存储器的时序规范,否则存储器在读写时数据会发生错乱,导致功能失效。

总之,在设计整体电路时,既要保证各个部分电路连接的正确性,又要保证其功能和时序的正确性,这样才能实现整个电路系统的稳定性。

4 仿真数据与波形

仿真采用csmc 0.35μm工艺模型,采用Hspice仿真工具,工作电压源为5V。为了能够更好的观察仿真结果,本设计只给出TT_25度的波形[7]。

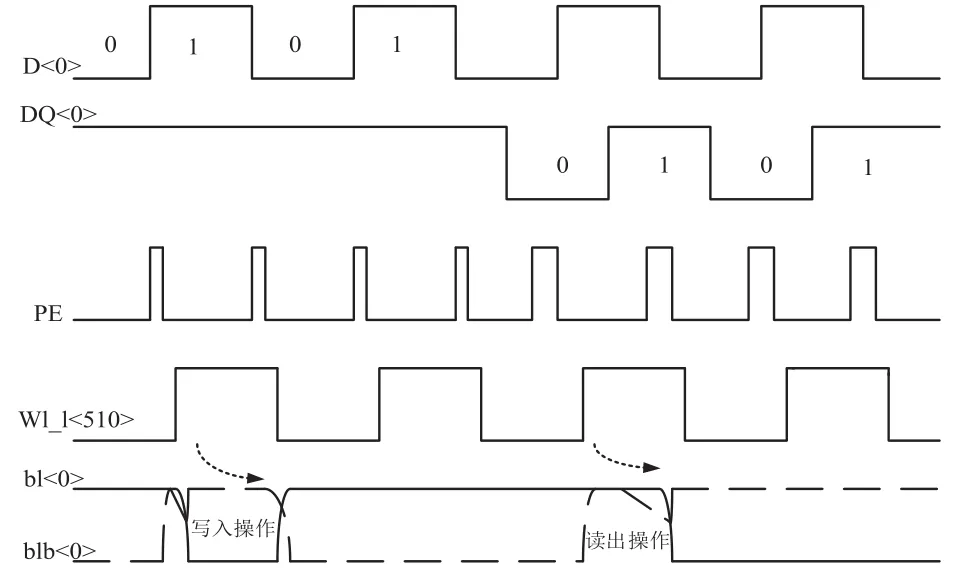

如图4所示,观察8个输入、输出中的D<0>、DQ<0>,前200ns为写入数据时间,后200ns为读出时间。在写入周期内连续写入4个数据0101,而在读出周期内连续读出4个数据0101,可以看出存储器的读写功能正确。

如果观察某个1bit存储单元的读写情况,可以通过观察这个存储单元的一对位线变化情况即可。

在图4中,选中了1M-bit SRAM的一条关键路径中的一个存储单元,分别通过块译码、字线译码、位线译码来确定这个存储单元的位置。将地址A<16:0>分别进行组合译码,选中第八块的左半部分;经过字线译码,选中第510条字线那一列的单元;经过位线译码,选中每一组位线中的第0条位线。所以,需要观察的目标是一对位线为bl<0>,blb<0>,一条字线为wl_l<510>的那个单元,如此便选中了需要观察的这个1bit存储单元。

图中画虚线箭头的部分,分别为这个1bit存储单元的写入、读出操作过程。存储单元写入时,blb<0>要完全被拉到低电平,并维持10ns左右,这样才可以使单元内部的信号翻转,写入正确的数据;读出过程中,由于bl<0>,blb<0>连接到外部的灵敏放大器,所以二者只需有微小的电压差即可被灵敏放大器识别放大,blb<0>的电平略有下降,但不必完全下降到低电平,这样便提高了存储器的读出速度[8]。

图4 写入、读出功能仿真

5 结束语

提出了一种高速低功耗的静态随机存储器体系结构,并根据这种体系结构,构建了1M-bit SRAM的整体电路架构。利用Hspice仿真工具对整体电路进行模拟仿真,通过观察电路关键路径中某一个1bit存储单元的写入、读出情况,可以看出设计基本上满足随机存储器的功能、速度、功耗等参数的性能指标。在今后的工作中,根据电路布局,可以完成它的物理版图设计,进而流片制造出成品。

[1][美]拉贝尔,等著.数字集成电路—电路、系统与设计[M].周润德,等译.北京:电子工业出版社,2004.[American]Rabaey,J.M.Digital Integrated Circuits:A Design Perspective[M].Zhourundei Translate.Beijing:Electronic Industry Press,2004.

[2]T Hirose,et al.A 20-ns 4-Mb CMOS SRAM with Hierarchical Word Decoding[J].IEEEJournal of Solid State Circuits,1990,25(5):1068-1074.

[3]T Ootani,et al.A 4-Mb CMOS SRAM with PMOS Thin-Film-Transistor Load Cell[J].IEEE Journal of Solid State Circuits,1990,25(5):1082-1092.

[4]J Chang.Theory of MNOS Memory Transistor[J].IEEE Trans.ElectronDevices,1977,ED-24:511-518.

[5]B S Amrutur,M A Horowitz.Fast Low-Power Decoders for RAMs[J].IEEE Journal of Solid-State Circuits,2001,36(10):1506-1515.

[6]B Prince,Emerging Memories:Technologies and Trends[M].Kluwer Academic Publishers,Boston,MA,2002.

[7]何乐年,王忆,编著.模拟集成电路设计与仿真[M].北京:科学出版社,2008.Helenian,Wangyi,Compile.Analog CMOS Integrated Circuits Design[M].Beijing:Science Press,2008.

[8][美]宋莫康,等著.CMOS数字集成电路—分析与设计[M].王志功,等译.北京:电子工业出版社,2005.[American]Songmokang.CMOSDigitalIntegrated Circuits:AnalysisandDesign[M].Wangzhigong Translate.Beijing:Electronic Industry Press,2005.

Design and Simulation of System Structure of High Velocity and Low Power SRAM

Zhao Yicheng,Zhou Gang

(The 47th Research Institute of China Electronics Technology Group Corporation,Shenyang 110032,China)

A design of a system structure of high velocity low power 1M-bit SRAM is described in this paper,and the construction of circuit is finished on the basis of system structure.At the same time,the simulation of the circuit system is accomplished by Hspice.In the conditions of 5V and CSMC 0.35μm process model,with the address access time of 15ns,the average dynamic power of 100mW and the static power of 6mW,good capability of low power and high velocity SRAM are carried out.

Static random memorizer;System structure;High velocity low power;Encoder;Sensitive amplifier;Kernel

10.3969/j.issn.1002-2279.2016.05.002

TN603

B

1002-2279(2016)05-0006-03

赵以诚(1984-),男,辽宁沈阳人,工程师,主研方向:集成电路设计。

2016-06-13