一种减小数字时钟延时单元温漂的方法

涂波,赵晓静,谢长生

(1.中国电子科技集团公司第五十八研究所,江苏无锡214072;2.无锡中微亿芯有限公司,江苏无锡214072)

一种减小数字时钟延时单元温漂的方法

涂波1,赵晓静1,谢长生2

(1.中国电子科技集团公司第五十八研究所,江苏无锡214072;2.无锡中微亿芯有限公司,江苏无锡214072)

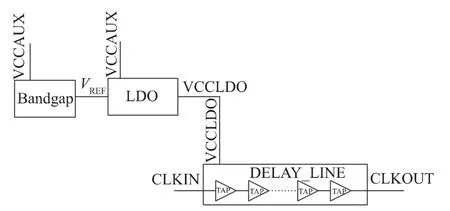

介绍了一种减小数字时钟延时单元温漂的方法,利用一个具有正温度系数的带隙基准电压源Bandgap,产生参考电压VREF;电压缓冲器LDO接收参考电压VREF并作用于延迟链;延迟链由延迟单元TAP串联而成,用来产生时钟的相位延迟。通过调整Bandgap的正温度系数,使LDO的输出电压随温度升高而升高,升高的电压会使延迟单元TAP的延时减小,从而抵消延迟单元TAP由于温度升高而增大的延时。

延时单元;温漂;带隙基准;LDO

1 引言

在延迟锁相环(DLL)中,需要使用延迟链对时钟进行去歪斜、频率合成以及相移。组成延迟链的基本单元是延时TAP,每个延时TAP的延时(tD)约为几十皮秒。DLL的锁定过程即调整TAP的个数,使目标时钟相位与基准时钟相位对齐[1]。DLL一旦锁定就不再对时钟相位进行检测。但是当延迟TAP电源电压稳定不变、温度升高时,TAP的延迟会增大。即DLL锁定后,如果温度升高,时钟的相位关系将发生变化,然而DLL并不会重新锁定。所以如果有一种设计方法能减小TAP的温漂,就可以提高DLL的相移精度、减小数字时钟的抖动等。

本方法设计的目的是针对现有实现方案存在的不足,设计了一种能减小数字时钟延时单元温漂的方法。

2 设计与实现

为了简化分析,以单端时钟经过一个反相器为例进行延时分析。当反相器的输入电平发生翻转时,输出电平也要随之变化,由于CMOS结构的原因,输出节点存在着容性负载,即在输出电平翻转过程中,需要对输出节点的负载电容充放电,由此决定了反相器的上升和下降延时时间。下面对CMOS反相器的上升时间瞬态特性进行简单分析。

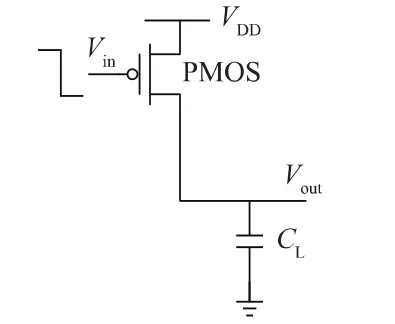

当反相器输出由低变高时,NMOS晶体管截止,PMOS开始导通对输出结点的负载电容CL充电,使输出上升为高电平。图1为分析上升时间的等效电路[2]。

图1 反相器输出高电平等效电路

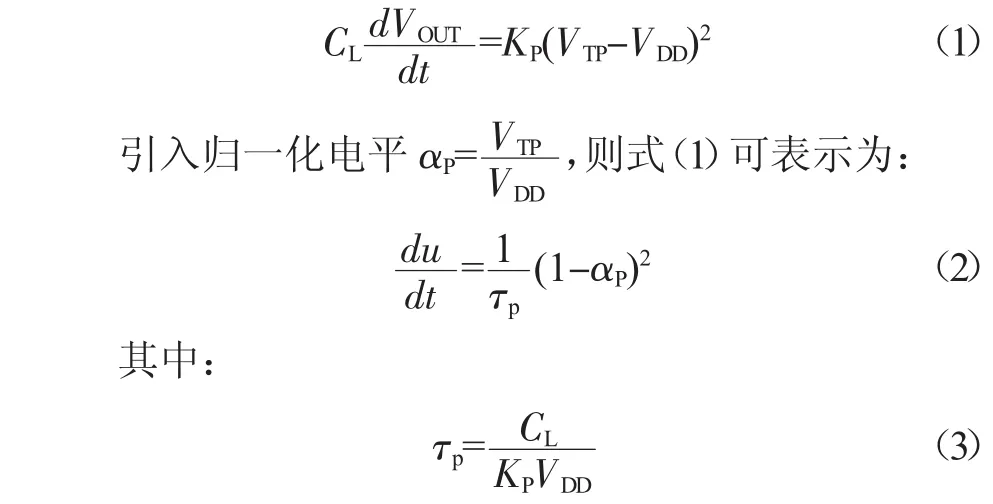

在VOUT≤-VTP时,PMOS工作在饱和区,因此有:

τp为上升时间常数,当VDD确定和管子工艺确定之后,τp为一个定值。对公式(2)积分得到饱和区充电时间:

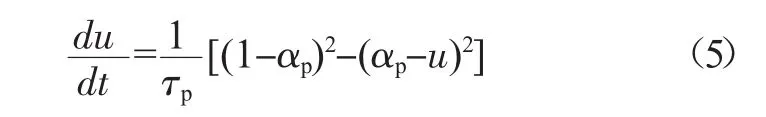

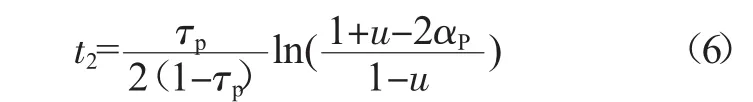

其中u为上升的输出电压,当VOUT>-VTP以后,PMOS管进入到线性区,根据线性区电流公式可以建立充电的微分方程:

由此可以得到PMOS管在非饱和区的充电时间:

总的上升过程包括饱和区充电与非饱和区充电两段时间。根据公式(4)和公式(6)可以得到电压上升到u所需的上升时间表达式。但以上是在假设VDD与负载电容一定这种特定情况下得到的t1与t2。既然特殊情况下得出了t1与t2的表达式,再考虑几种一般情况:(1)假设PMOS管的工艺、尺寸大小已经确定,不难发现t1与t2都与VDD成反比例关系,也就是说t1与 t2随着电压的增大而减小(将公式(3)带入公式(4)和公式(6));(2)假设VDD一定,发现t1与t2都与VTP成正比例关系(将归一化电平带入公式(4)和公式(6))。

1.3.1 体位固定与定位影像 对21例头部肿瘤患者制作发泡胶个体化头枕,再用面部开口的热塑面膜制作固定面罩。在Brilliance CT Big Bore CT模拟定位机上扫描采集影像,扫描条件:3 mm层厚、120 kV、400 mAs,进行重建得到三维影像,制定治疗计划,获得靶区定位影像、体表影像和治疗参数,并传输到EDGE直线加速器。

通过上面对反相器延时的分析,我们得出一个结论:反相器的延时随电压的增大而减小、随温度的升高而增大。如果我们设计一个系统,使系统电压随温度升高而升高,当升高电压产生的延时减小与升高温度产生的延时增大相等时,那么这个系统的延时就不会随温度变化而变化。

经过以上的论证,我们提出了新的设计方案,该方案的原理如图2所示。

图2 设计原理图

Bandgap、LDO为电源部分,DELAY_LINE为核心部分。其中Bandgap具有正温度系数,输出电压VREF随温度升高而升高,LDO为电压缓冲器,为DELAY_LINE提供内部电源,还可以隔离外部电源的噪声。

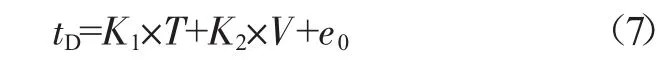

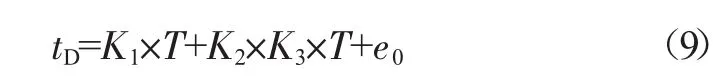

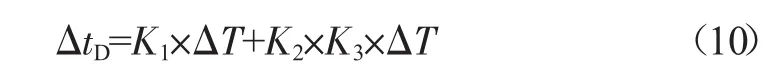

下面将从这两部分详细阐述其瞬态特性。DELAY_LINE由一连串的延时单元TAP构成,起到延迟时钟相位的作用。TAP采用差分结构,该TAP的特征是:当电压不变、温度升高时,TAP延时(tD)增大;当温度不变、电压升高时,TAP延时(tD)减小。下面我们假设DELAY_LINE中TAP的延时可以表示为:

其中V是指LDO的输出电压VCCLDO,具有正温度系数,可以表示为:

将公式(8)代入公式(7),该系统中TAP的延时可以表示为:

如果温度变化为△T,那么延时变化量△tD可表示为:

为减小延时单元TAP的温漂,△tD应尽可能小,当K1=-K2×K3时,公式(10)等于0,即延时单元TAP零温漂。在设计中,当TAP的尺寸和工艺确定后,系数K1、K2也就确定了,这时只要调整系数K3,使K1=-K2×K3即可实现零温漂。

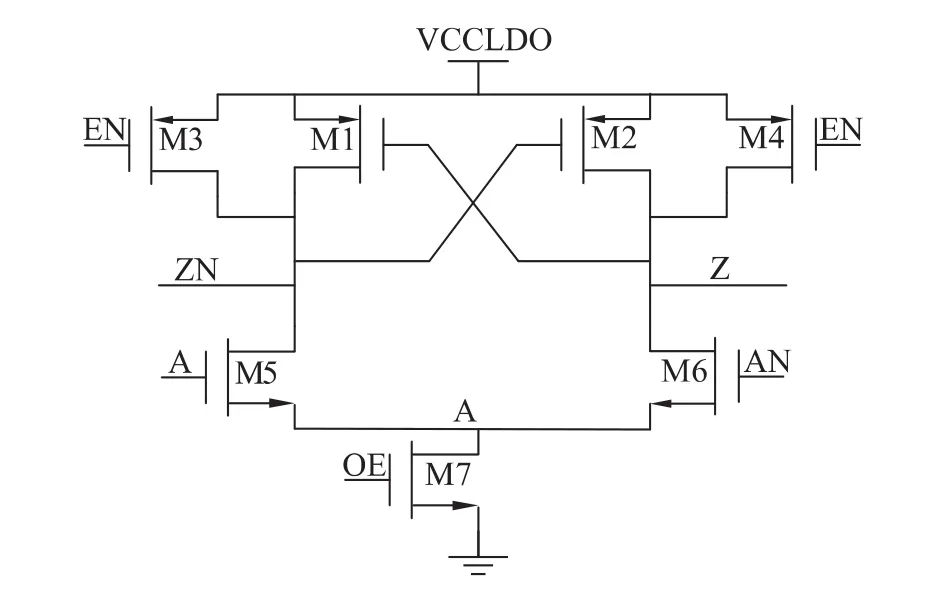

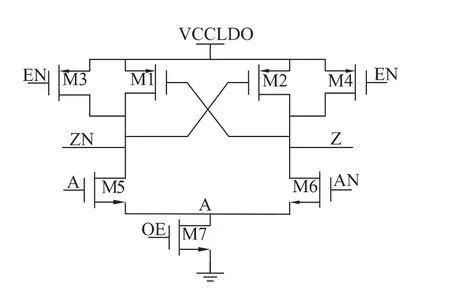

本设计为了处理差分时钟,延迟单元TAP采用差分结构(其延时的温度和电压特性与单端反相器类似),通过仿真的方法求得系数K1和K2的近似值,再由系数K1和K2计算出系数,完成本设计。差分延迟单元TAP结构[3]如图3所示。

图3 TAP设计电路图

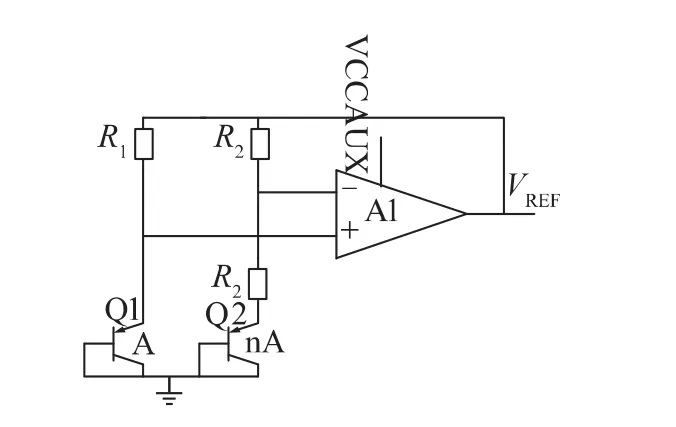

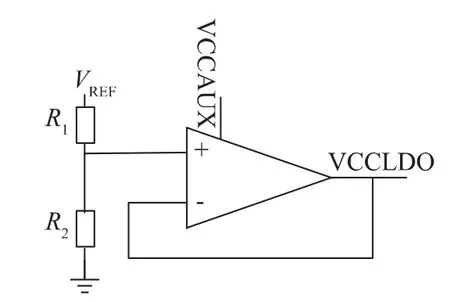

Bandgap的供电电源VCCAUX为2.5 V,输出电压VREF随温度的升高而增大,常温下为1.5 V。该VREF为LDO的参考电压。该设计中的Bandgap原理图[1]如图4所示。

图4 Bandgap原理图

根据对图4 Bandgap原理图的分析,有VBE1-VBE2=VTlnn,得到流过右边支路的电流为VTlnn/R3,因此VREF为:

整理得到:

Bandgap输出VREF给LDO作为参考电压,LDO可以有效抑制外部电源的噪声并驱动延迟链,其采用传统结构,输入电压为VREF经过分压后的电压,常温下该LDO的输出电压为1.1 V。当温度变化时,LDO的输出电压随VREF线性地变化,通过调整电阻R1和R2的比例,可以改变VCCLDO输出电压以及输出电压随温度变化的斜率,使其更好地匹配TAP的温度系数。该设计中的LDO原理如图5所示。

图5 LDO原理图

在图5中,参考电压VREF为具有正温度系数的电压(常温下为1.5 V),经R1与R2分压后(1.1 V)给运放的同相端(INP),该运放的输出端直接与输入端相连,为一个电压跟随器,其驱动电压为VCCAUX(典型值为2.5 V)。因此,无论驱动电压VCCAUX在正常范围内变化多少,输出电压VCCLDO都被钳位在运放的同相端(INP)电压值。

3 仿真验证

基于SMIC 40 nm工艺,建立整个仿真验证环境,利用Cadence公司仿真工具spctre设计仿真验证。仿真模型版本为smic40ll_1125_2tm_oa_cds_1P10M_ 2012_10_11_v1.4,本仿真中的TAP电路原理如图6所示。

图6 仿真中的TAP电路原理图

在图6中,M5与M6为差分输入对管,M1与M2分别为M5与M6的负载,M7为M1和M5或M2和M6提供偏置电流。其如图6所示的连接方法形成了正反馈回路,加快了时钟的翻转速度。其中各个CMOS管的尺寸如下。

M1、M2:W/L=1.35 μm/100 nm;

M3、M4:W/L=200 nm/200 nm;

M5、M6:W/L=1.35 μm/40 nm;

M7:W/L=1.8 μm/40 nm。

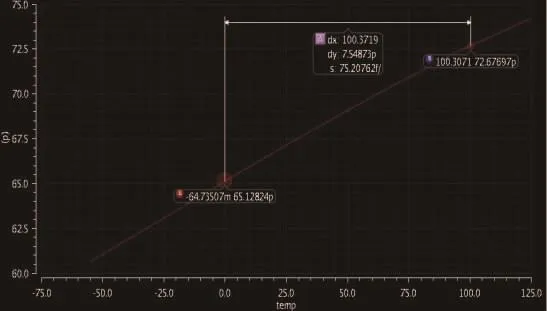

TAP延时随温度变化如图7所示(TT VCCLDO=1.1 V)。

图7 温度与延时曲线

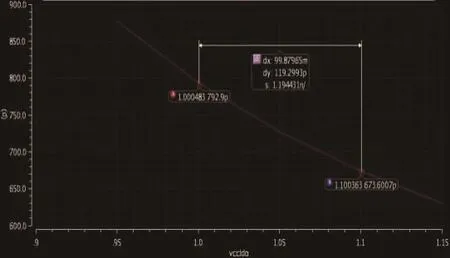

图8 电压与延时曲线

由图7可见,当VCCLDO电压一定时,该尺寸的TAP的温度特性为+75 fs/℃,即K1=+75 fs/℃,表示电压一定时温度每增加1℃,TAP延时增大75 fs。在图8中,当温度恒定为27℃时,TAP的延时随LDO电压的升高而减小,为了测量更加准确,将10个TAP串联起来然后求平均值,即可得到每个TAP的变化率。由仿真图可见,每个TAP的电压特性为-0.119 fs/μV,即K2=-0.119 fs/μV,表示温度一定时电压每增大1 μV,TAP延时减小0.119 fs。至此,如果忽略温度对TAP电压特性的影响,即假设任意温度下TAP的电压特性均为-0.119 fs/μV,则可以设计一个正温度系数的Bandgap,使其温度系数K3=+630 μV/℃(75÷0.119= 630),这样TAP就实现了零温漂。但是,由于实际中TAP的电压特性也会随温度的变化而变化,所以不可能实现TAP延时的零温漂,但该方法可以使TAP的温漂达到最小化。

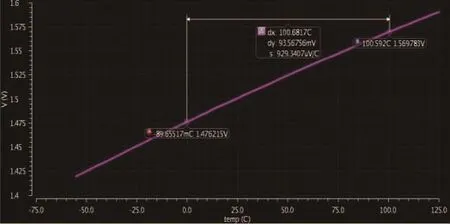

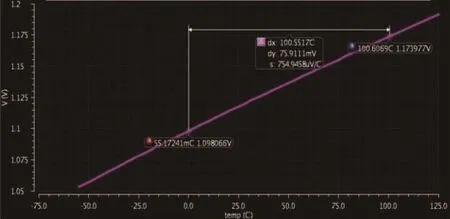

下面开始仿真调试Bandgap和LDO,本设计中Bandgap温漂如图9所示(TTcorner,VCCAUX=2.5V),LDO输出温漂如图10所示(TT VCCAUX=2.5V)。

图9 Bandgap电路电压随温度曲线

图10 LDO电路电压随温度曲线

由图9、图10可见,Bandgap温漂为+929.34μV/℃,LDO输出电压的温漂系数为+754.94 μV/℃(温漂为曲线的斜率)。

LDO本身基本没有温漂,由于Bandgap提供的参考电压随温度变化,所以LDO的输出也会随温度变化,由于参考电压VREF经电阻分压后送给LDO,所以LDO输出随温度变化曲线的斜率会变小,使其与TAP的温度系数相匹配,最大程度地减小TAP延时的温漂。

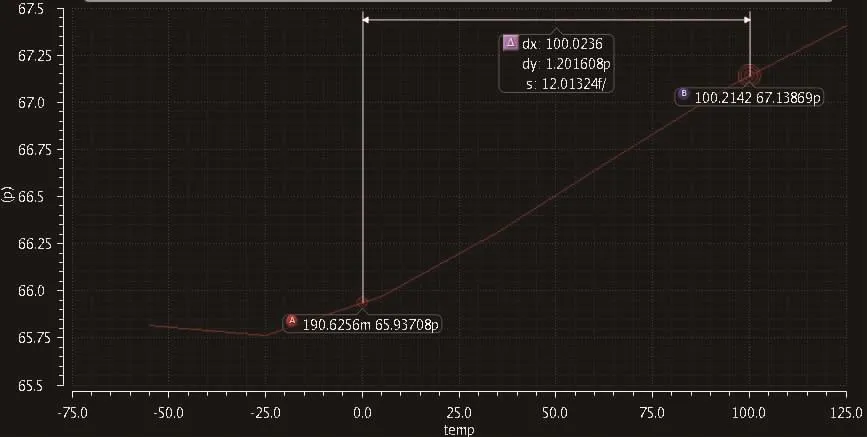

最后,我们将TAP和调试好的Bandgap和LDO进行联合仿真,观察TAP的延时随温度变化的曲线。TAP延时随温度变化(抵消后)情况如图11所示(TT VCCAUX=2.5 V)。

图11 TAP延时随温度变化情况

由图11可见,TAP的温度特性约为+12 fs/℃,即电压一定时温度每增加1℃,TAP延时增大12 fs。相比较图6中VCCLDO电压不变时TAP的延时温漂+75 fs/℃,本方法设计TAP延时的温漂减小了(75-12)÷75=84%。

4 小结

本文介绍了一种减小数字时钟延时单元延时温漂的设计方法,主要应用于数字时钟管理领域,可以有效降低数字时钟的抖动,提高相移的精度等。通过仿真验证,延时单元TAP的延时温漂减小了84%。

[1](美)毕查德·拉扎维.模拟CMOS集成电路设计[M].西安:西安交通大学出版社,2002.

[2]甘学温.数字CMOS VLSI分析与设计基础[M].北京:北京大学出版社,1999.

[3]邱有刚,黄建国.基于FPGA数字延迟单元的实现和比较[J].电子测量技术,2011,34.

[4]卢剑寒,张剑.一种RC延时电路的温漂分析和补偿[J].集成电路通讯,2012,4.

A Method of Reducing the Delay Temperature Drift for Digital Clock Delay-Cells

TU Bo1,ZHAO Xiaojing1,XIE Changsheng2

(1.China Electronics Technology Group Corporation No.58 Research Institute,Wuxi 214072,China;2.East Technologies,inc.Wuxi 214072,China)

In the paper,a design reducing the delay temperature drift of digital clock delay-cellis described, which includes a Bandgap reference voltage(VREF)generator having a positive temperature coefficient,a LDO whichreceivesthe VREFandpowerthe delayline.The delayline contains a series of delay-cells and used for shift the clock phase.By a positive temperature coefficient of Bandgap designed,the delay-cell power voltage will change same direction with temperature,which compensates the delay variation of delay-cell caused by the changedtemperature.

delay-cell;temperature drift;bandgap;LDO

TN402

:A

:1681-1070(2017)09-0028-04

2017-4-8

涂波(1985—),男,四川南充人,本科,工程师,研究方向为千万门级FPGA设计与验证。