基于FPGA的嵌入式通信系统核心模块设计

杨胜利 李超 余亮

摘 要: 基于IP核的SpaceWire?PCI通信卡进行通信时,没有考虑传输过程内相位失真问题,其通信效果存在实时性能低、抗干扰性差和通用性低的缺点。据此设计基于FPGA的嵌入式通信系统的通信卡,其整体架构由FPGA模块、以太网88E1111 PHY芯片、MCP2515 CAN控制器等组成。采用FIR滤波器分布式算法处理通信卡信号传输时的内相位失真问题。利用SoPC系统的Nios Ⅱ集成开发环境设计通信卡软件:设计初始化程序实现FPGA模块中Cyclone Ⅲ 3C25F32芯片控制寄存器的配置;设计通信程序实现通信卡中数据信息的发送和接收。实验证明,所设计通信卡通信效果具有实时性高,抗干扰性好及通用性高等优势,能够极大地提高通信效率。

关键词: FPGA; 嵌入式系统; 通信卡; 接口电路; 控制寄存器; 通信程序

中图分类号: TN914?34; TP274 文献标识码: A 文章编号: 1004?373X(2018)22?0088?04

Abstract: The SpaceWire?PCI communication card based on the IP core has the disadvantages of low real?time performance, poor anti?interference and low universality in communication effect because the internal phase distortion problem in the transmission process is not considered. Therefore, a communication card based on FPGA is designed for the embedded communication system. The overall architecture of the communication card is composed of the FPGA module, Ethernet 88E1111 PHY chip, MCP2515 CAN controller and so on. The FIR filter distributed algorithm is adopted to deal with the internal phase distortion problem during the signal transmission of the communication card. The Nios Ⅱ integrated development environment of the SoPC system is utilized to design the software of the communication card. The initialization program is designed to realize the control register configuration of the Cyclone Ⅲ 3C25F32 chip in the FPGA module. The communication program is designed to realize transmitting and receiving of data information in the communication card. The experimental results show that the designed communication card has the advantages of high real?time performance, good anti?interference and high universality in communication effect, which can greatly improve the communication efficiency.

Keywords: FPGA; embedded system; communication card; interface circuit; control register; communication program

0 引 言

目前,半导体技术日益成熟,研究开发大范围可编程逻辑器件成为电子系统开发领域内的主要研究目标。在大范围可编程逻辑器件中FPGA最具代表性[1],随着嵌入式系统与网络结合的日益加深,其已渐渐成为未来的发展趋势。人们能够利用嵌入式系统通过网络对家庭及工作、学习等不同环境中的状态进行远程查看。因此,嵌入式通信系统在未来对人们的影响更为深远[2]。传统基于IP核的SpaceWire?PCI通信卡进行通信过程中,没有考慮传输过程内相位失真问题,其通信效果存在实时性能低、抗干扰性差和通用性低等问题,已经不能满足人们的需求[3]。本文设计基于 FPGA的嵌入式通信系统通信卡提高通信系统的通信效率和抗干扰性。

1 基于FPGA的嵌入式通信系统的通信卡设计

1.1 设计通信卡总体架构

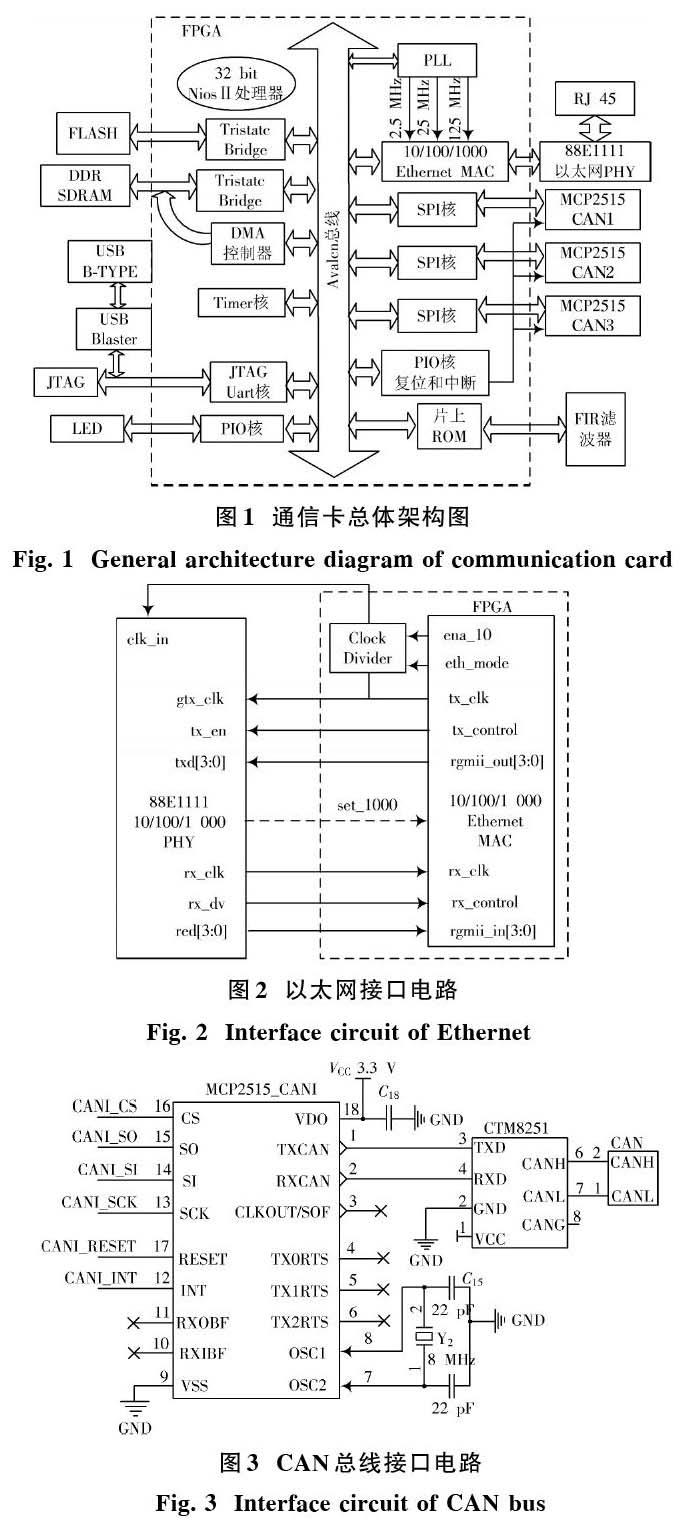

基于FPGA的嵌入式通信系统通信卡总体架构如图1所示。采用Cyclone Ⅲ 3C25F32芯片及NiosⅡ嵌入式处理器设计通信卡FPGA模块,其是通信卡的关键模块,该模块内核电压是1.2 V,内存控制器可使用1.8 V,2.5 V和3.3 V等电压。在FPGA模块外增加FIR滤波器[4]、以太网88E1111 PHY芯片、MCP2515 CAN控制器等,其中以太网链路层传输速率选择自适应10/100/1 000 MAC与2.5 MHz,25 MHz及125 MHz时钟频率两两关联。

1.2 设计通信卡接口电路

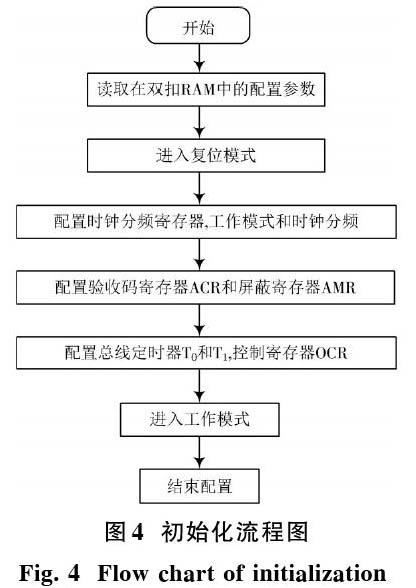

设计通信卡的以太网接口电路及CAN总线接口电路,实现通信卡数据的有效传输,可为通信卡上电提供服务[5]。以太网物理层和链路层分别采用千兆位88E1111芯片、吉比特介质独立接口和三速以太网内核。其中88E1111芯片的内存控制器可用2.5 V电压,图2为以太网与FPGA接口电路图。

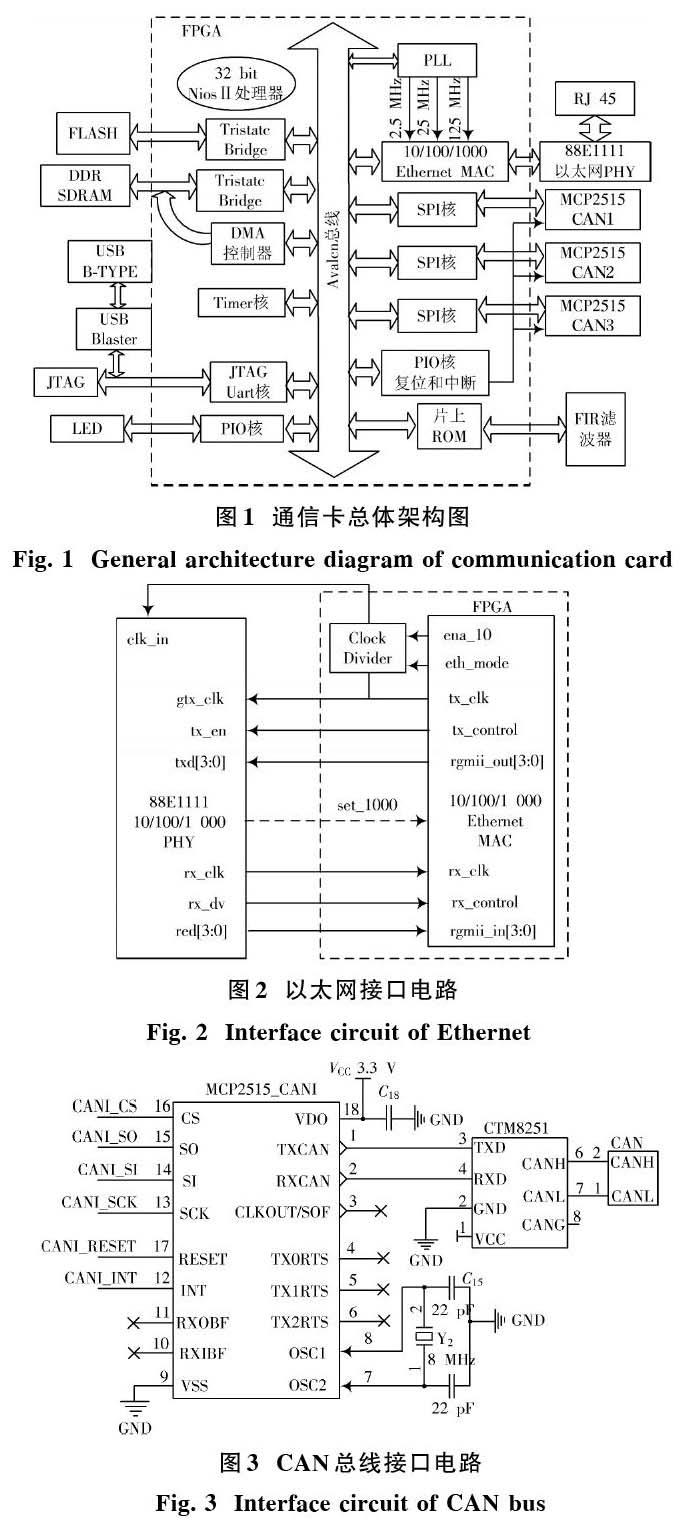

CAN控制器和CAN收发器分别采用MCP2515控制器和CTM8251收发器。由于MCP2515控制器的工作电压范围是2.7~5.5 V,为了使控制器和FPGA模块忽略电平变更,FPGA供电系统需采用3.3 V电压。由于CTM8251收发器可以使用3.3 V及5 V电压的CAN控制器,因而MCP2515控制器同CTM8251收发器间同样可以忽略电平的变更[6]。在MCP2515控制器内含未用过的管脚,管脚内的上拉电阻使其悬浮。设计CAN总线接口电路如图3所示。

1.3 向FPGA模块内融入SoPC系统

经过第1.2节的操作,为通信卡数据通信提供基础,实现通信卡上电后,针对FPGA模块进行SoPC的设计,通过可编程片上技术SoPC系统塑造通信卡模块的硬件模型,为通信卡的程序编程提供服务。

1) 使用可编程片上系统(System?on?a Programmable Chip,SoPC)Builder定制NiosⅡ处理器。进入Quartus Ⅱ软件,点击“tools”按键,开始项目定制,其中HDL代码由Verilog语言构建,对目标FPGA和时钟进行取舍[7]。

2) 增设模块。点击 “Avalon Components”和“Nios Ⅱ Processor”,进入“Add New Nios ⅡProcessor”,点击“Nios Ⅱ / f”(全能型CPU), Nios ⅡCPU就这样生成。继续增设系统时钟、FLASH和以太网等串行外设接口(Serial Peripheral Interface,SPI)核。

3) 模块增设结束后,进行中断优先级操作。进行操作时SoPC Builder给不同系统IP模块设置一个通过许可的基地址[8]。

4) 生成并修订SoPC系统。完成上述操作后,为实现Nios Ⅱ处理器融入Quartus Ⅱ项目内,形成SoPC系统并进行修订,全部结束后将SoPC系统添加进通信卡的FPGA模块的硬件内,为通信卡模块的程序编程提供服务。

2 通信卡软件设计

本文通信卡采用SoPC系统中的Nios Ⅱ集成开发环境(IDE),进行通信卡片上硬件的软件代码写入,对设计通信卡软件的效率有积极作用[9]。基于FPGA的嵌入式通信系统的通信卡进行通信的步骤分为两部分。系统上电和正常运行。为实现正常运行需要进行初始化程序设计、通信程序设计。

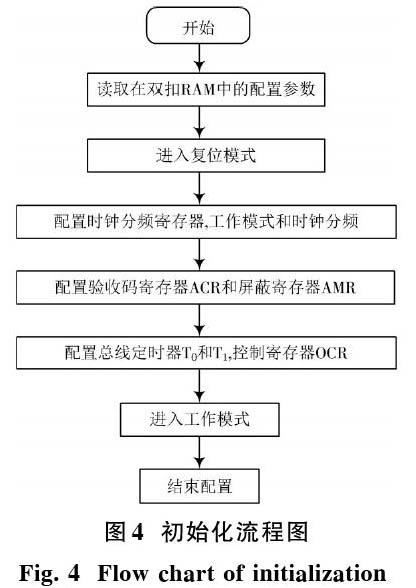

对系统实施初始化,预定波特率及节点ID,装备通信参考数据是通过CAN初始化函数进行的。当通信卡FPGA模块中Cyclone Ⅲ 3C25F32芯片于上电或硬件上实施复位时,处于复位状态内,通过Nios Ⅱ处理器实现Cyclone Ⅲ 3C25F32芯片的控制寄存器的配置。装备时钟分频寄存器:通过PeliCAN格式判断实现CLKOUT管脚[10];装备验收码寄存器对接收报文的验收码进行描述;装备验收屏蔽寄存器对照报文和验收码的相关位描述验收实施阻拦;除此之外还有其他寄存器装备。图4为初始化流程图。

3 实验分析

实验对本文设计的基于FPGA的嵌入式通信系统的通信卡进行通信功能的验证。设置参数如下:通过VC++ 6.0构建客户端操作界面;基于Windows Sockets规则设计通信卡接口。打开客户端采用本文设计通信卡进行以太网参数设定,完成连接后,对PMSM电机的电流环、速度环等参数进行设置。图5为客户端得到的PMSM电机速度监测数据。分析图5能够得到:客户端使用本文设计的通信卡获取的PMSM电机的转速保持在400 r/min;客户端能够获取的驱动器电机数据,其数据表示完成PMSM电机转速预定后,电机的工作速度从开始的加速转为解剖匀速。为了验证本文通信卡的实时性能,利用本文设计的通信卡和基于IP核的 SpaceWire?PCI通信卡进行实时检测对比。对比结果见表1。

分析表1可知,基于IP的SpaceWire?PCI通信卡平均响应时间为146 ms,而本文通信卡是利用以太网进行传输,所以响应时间大大降低,平均响应时间为23 ms。實验证明,应用本文通信卡可以大幅度降低服务端响应时间,提升通信系统通信的实时性。

为了验证本文设计的通信卡具有较高的使用性能,将本文设计的通信卡与基于IP的SpaceWire?PCI通信卡在不同的性能方面进行对比,对比结果如表2所示。

通过表2能够得到,相比于基于IP的SpaceWire?PCI通信卡,本文设计的通信卡在抗干扰性、通用性、通信效率等方面均有较大的优势。实验证明,本文设计的通信卡具有抗干扰性好、传输速率快及通用性高等优势,能够极大地提高通信效率。

4 结 论

本文设计基于FPGA的嵌入式通信系统的通信卡。其运用FIR滤波器分布式算法处理相位失真问题,提高通信质量;并且向通信卡FPGA模块内融入SoPC系统,实现通信卡初始化程序及通信程序的设计。本文设计的通信卡使用范围将越来越广泛,对人们未来的生活、工作、学习的影响会更为深远。

参考文献

[1] 贺永鹏,张向前,张凯,等.一种基于FPGA的嵌入式实时以太网[J].电气传动,2015,45(7):70?73.

HE Yongpeng, ZHANG Xiangqian, ZHANG Kai, et al. FPGA?based embedded real?time Ethernet protocol [J]. Electric drive, 2015, 45(7): 70?73.

[2] 马飞,刘琦,包斌.基于FPGA的AXI4总线时序设计与实现[J].电子技术应用,2015,41(6):13?15.

MA Fei, LIU Qi, BAO Bin. Design and implementation of AXI 4 bus timing based on FPGA [J]. Application of electronic technique, 2015, 41(6): 13?15.

[3] 鄧广志,孙元.基于FPGA的嵌入式真彩色数字视频采集系统[J].半导体光电,2016,37(4):592?595.

DENG Guangzhi, SUN Yuan. True color digital video acquisition embedded system based on FPGA [J]. Semiconductor optoelectronics, 2016, 37(4): 592?595.

[4] 贲广利,王永成,徐东东,等.以太网数传系统在FPGA上的实现[J].液晶与显示,2017,32(8):607?613.

BEN Guangli, WANG Yongcheng, XU Dongdong, et al. Realization of Ethernet data transmission system on FPGA [J]. Chinese journal of liquid crystals and displays, 2017, 32(8): 607?613.

[5] 赵爱明,杨亮.基于FPGA的多通道智能CAN卡设计[J].电测与仪表,2016,53(14):106?111.

ZHAO Aiming, YANG Liang. Design of multiple channels CAN card based on FPGA [J]. Electrical measurement & instrumentation, 2016, 53(14): 106?111.

[6] CARRI? F, KIM H Y, MORENO P, et al. Design of an FPGA?based embedded system for the ATLAS tile calorimeter front?end electronics test?bench [J]. Journal of instrumentation, 2014, 9(3): 705?710.

[7] 王静.嵌入式通信网络系统的抗毁性设计方法研究[J].现代电子技术,2016,39(16):64?67.

WANG Jing. Research on invulnerability design method of embedded communication network system [J]. Modern electronics technique, 2016, 39(16): 64?67.

[8] 周天剑,吴方.基于嵌入式技术的路况识别系统设计与实现[J].计算机仿真,2015,32(9):185?188.

ZHOU Tianjian, WU Fang. Design and implementation of traffic identification system based on embedded technology [J]. Computer simulation, 2015, 32(9): 185?188.

[9] 时旭,付成伟.基于FPGA的CAN总线通信系统的设计[J].现代电子技术,2015,38(22):59?61.

SHI Xu, FU Chengwei. Design of FPGA?based CAN bus communication system [J]. Modern electronics technique, 2015, 38(22): 59?61.

[10] 郭志红,石春,吴刚.嵌入式以太网通信系统设计与实现[J].小型微型计算机系统,2015,36(4):754?758.

GUO Zhihong, SHI Chun, WU Gang. Design and implementation of the embedded Ethernet communication system [J]. Journal of Chinese computer systems, 2015, 36(4): 754?758.