TFT-LCD摩擦工艺过程中静电放电不良分析及改善设计

王国磊,陈 鹏,李恒滨,王景棚,杜化鲲,马 力,宋红花,王勇辉,张熠点,李 宁

(合肥鑫晟光电科技有限公司,安徽 合肥,230012)

1 引 言

在TFT-LCD 制造业和集成电路(Integrated Circuit,IC)制造业中,静电放电(Electro Static Discharge ,ESD)一直扮演着重要角色,其直接会影响到产品的良品率,在设计、制造、测试和运送过程中都要考虑ESD的影响[1]。

摩擦取向工艺是液晶成盒阶段比较重要的工序,至今仍然是各类液晶显示器制造过程中使用最广泛的取向技术[2]。摩擦具体工艺就是摩擦设备将基板真空吸附在基台上,一边转动滚筒,一边使基台移动进行摩擦。由于摩擦取向工艺是通过物理摩擦的方式,所以极其容易引入静电,当静电积累到一定程度后释放就会引起相应的不良。

ESD引起的不良现象主要表现为画面显示异常(Abnormal Display)、亮暗线(Line Defect)、亮暗点不良(Dot Defect)等。ESD是行业的顽疾,是影响良率的重要因素,除了在生产制造过程中,加强生产管理和除静电设施的使用外[3],预先防止的设计也是非常重要的[4-7]。

本文以摩擦取向工艺过程中的不良分析为出发点,通过设计方案优化进而提升液晶面板抗静电能力作为主要论述内容。

2 分析及结果

2.1 实际产品ESD不良分析

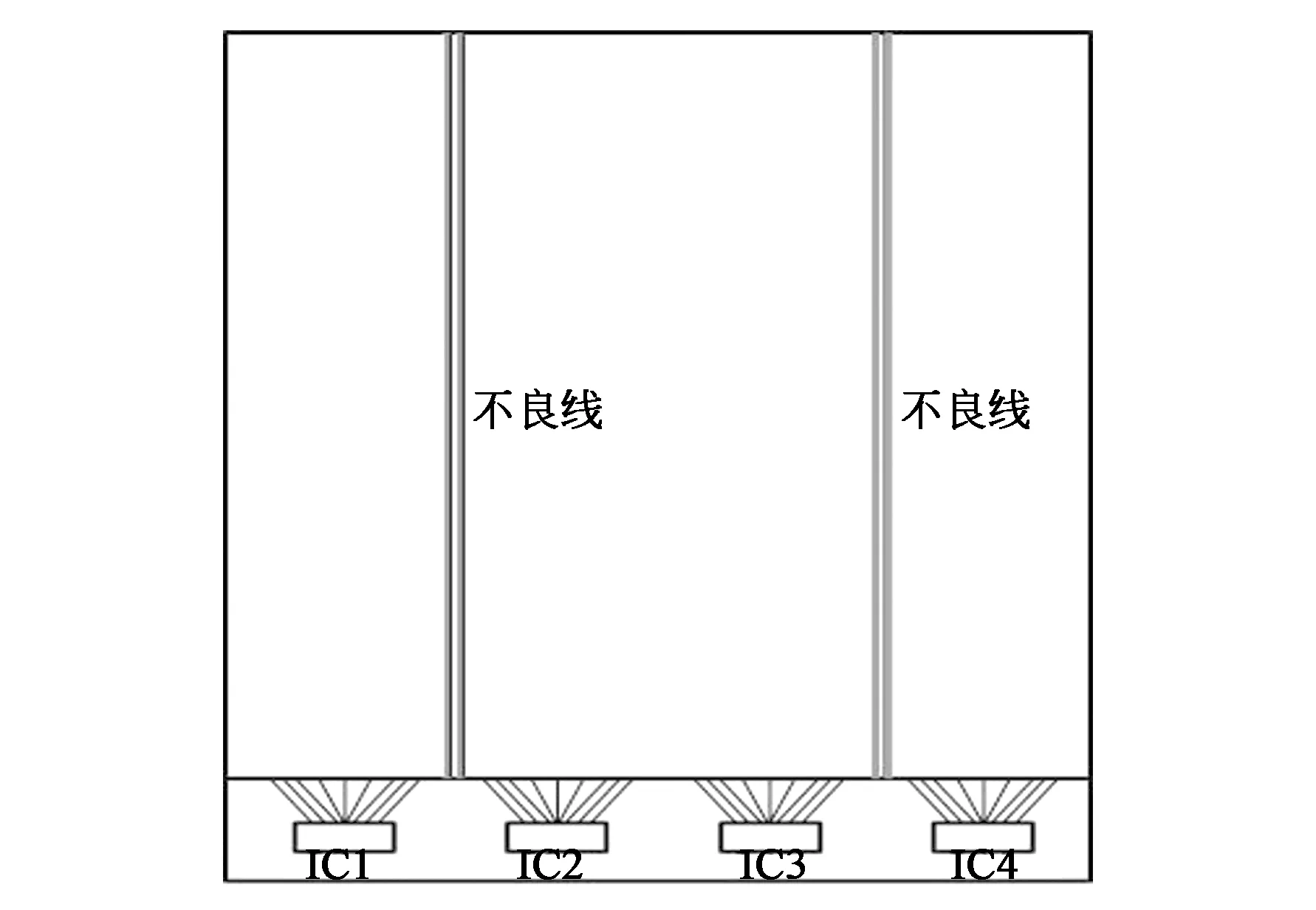

对于TFT-LCD工艺制程和产品良率管控来说,能够迅速定位不良发生的工艺环节以及根本原因是极为重要的。图1为某实际产品不良示意图,在初次工艺生产过程中,此不良引起的不良率约为20%。从图中可以看出,在驱动IC1和IC2中间以及IC3和IC4中间有两条线不良。经过对大量工艺数据进行统计学分析及逐个工序确认,最终确认不良发生工序为成盒过程中的摩擦工艺工序。

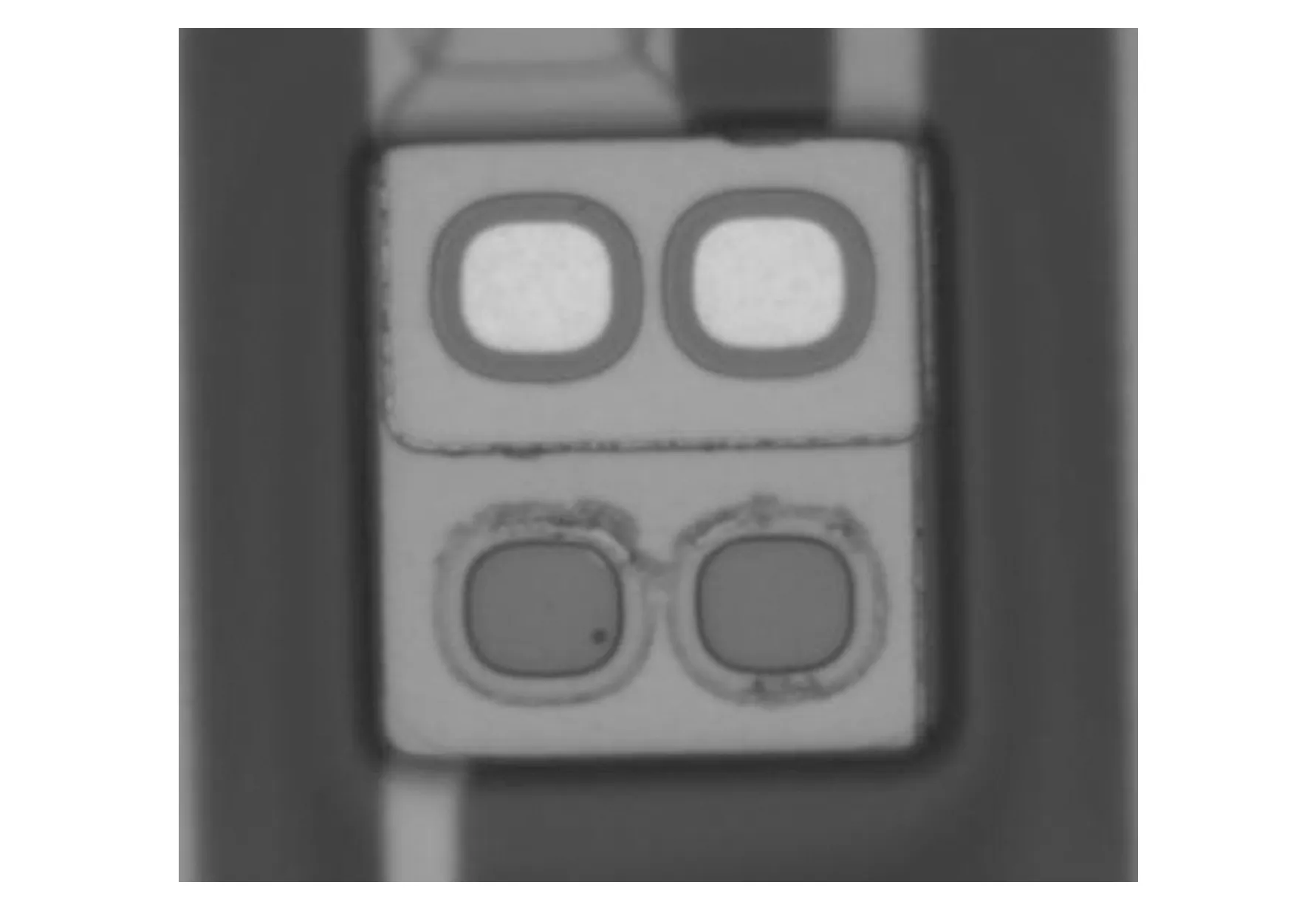

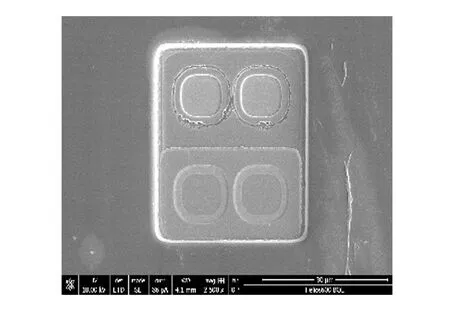

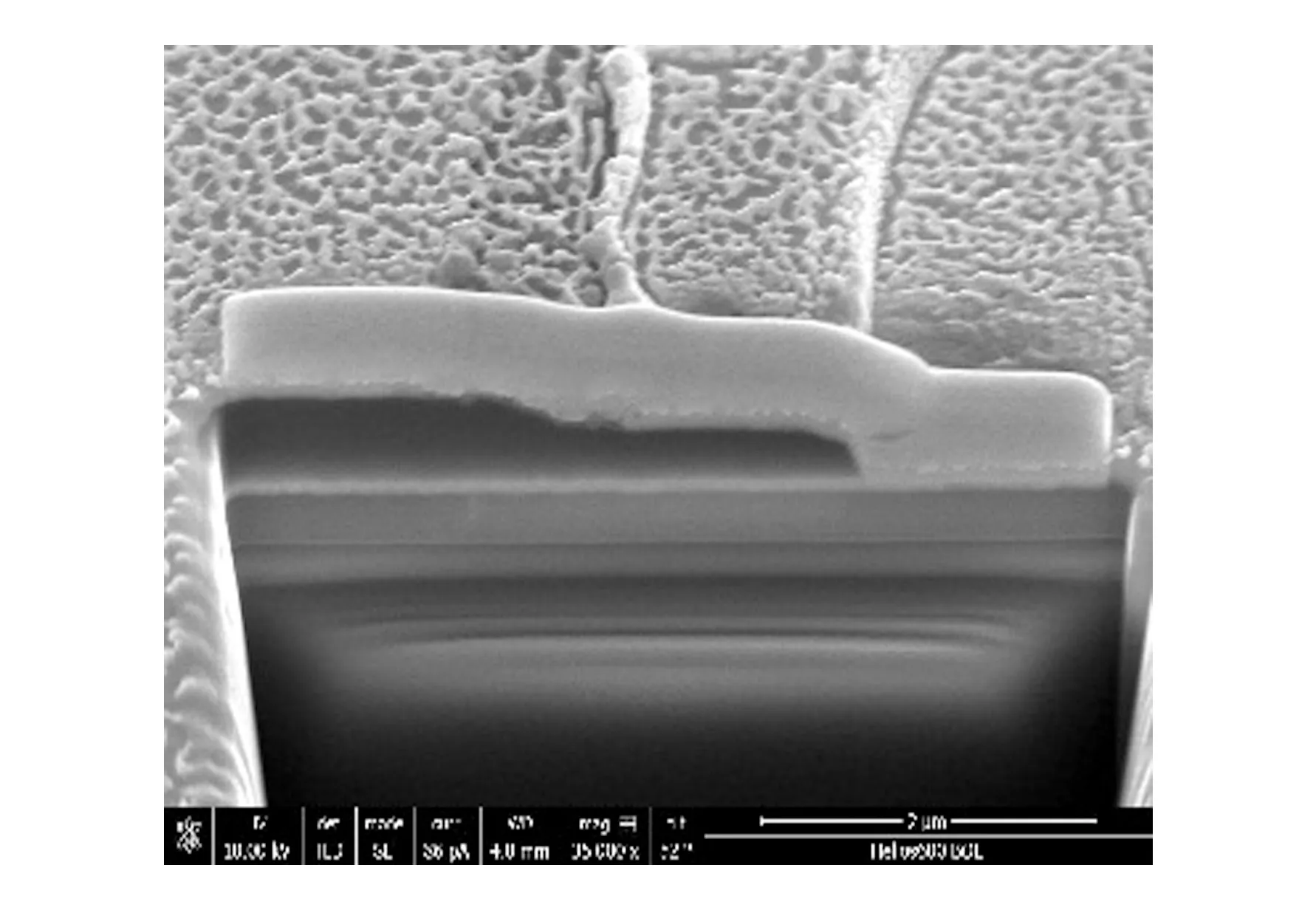

图2是IC1和IC2中间及IC3和IC4中间有两条线不良位置的连接过孔在显微镜下的图片。从图中可以看出,在连接过孔的周围有ESD烧毁的痕迹。为了进一步明确此过孔位置ESD烧毁是出现此线不良的根本原因,在扫描电镜(SEM)下确认了此过孔位置的俯视图和断面图。图3和图4为过孔位置的俯视图和断面图。俯视图和断面图进一步说明,连接过孔位置确实存在桥接金属断裂问题。

图1 产品不良示意图Fig.1 Product defect schematic diagram

图2 线不良位置过孔显微镜图Fig.2 Contact hole at line defect position under microscope

图3 线不良位置过孔扫面电镜俯视图Fig.3 Top picture of contact hole at line defect position under SEM

图4 线不良位置过孔扫描电镜断面图Fig.4 Cross section of contact hole at line defect position under SEM

2.2 产品设计相关分析

为了进一步从设计源头明确此不良的相关性,对比了IC1和IC2中间、IC2和IC3中间及IC3和IC4中间填充图形的设计。表1是针对不同位置填充图形的对比结果。从表中可以看出,IC1和IC2中间及IC3与IC4中间填充图形的面积较IC2和IC3中间较大,而IC2与IC3中间无线不良的发生。

表1 不同IC中间填充图形比较Tab.1 Comparison of dummy pattern between different IC location

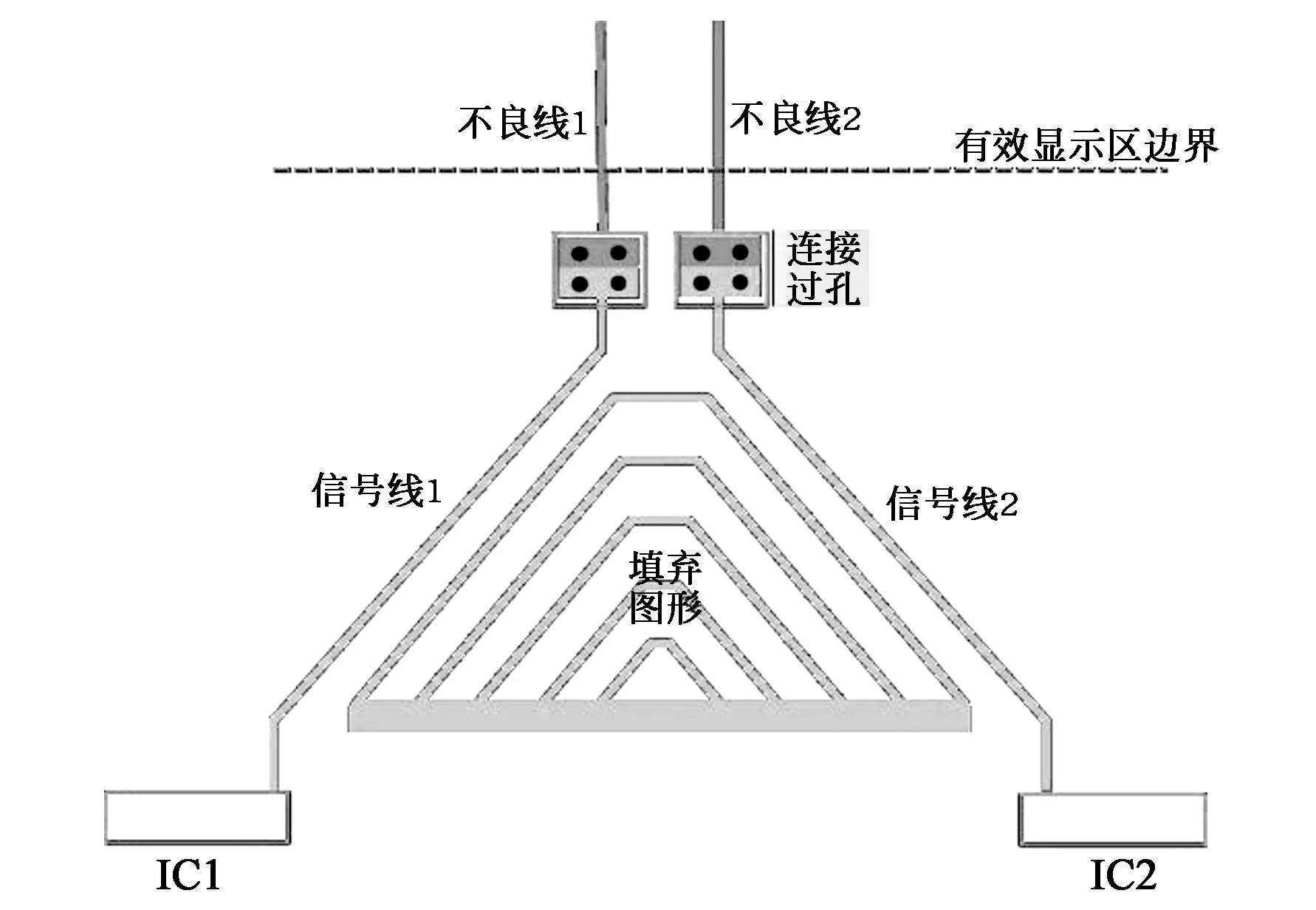

为了更清楚地说明不良位置的结构及填充图形的位置,此部分的结构示意图参考图5。

图5 线不良位置结构示意图Fig.5 Line defect position schematic diagram

从图中可以看出,IC1的最右端信号线1和IC2最左侧信号线2分别通过连接过孔连接到有效显示区的不良线1和不良线2。在信号线1和信号线2中间是孤立的填充图形。填充图形是为了保证阵列(Array)工艺过程中的金属线在刻蚀过程中的均一性,为了保证成盒工艺段摩擦工艺中不易发生摩擦Mura而必须存在的。

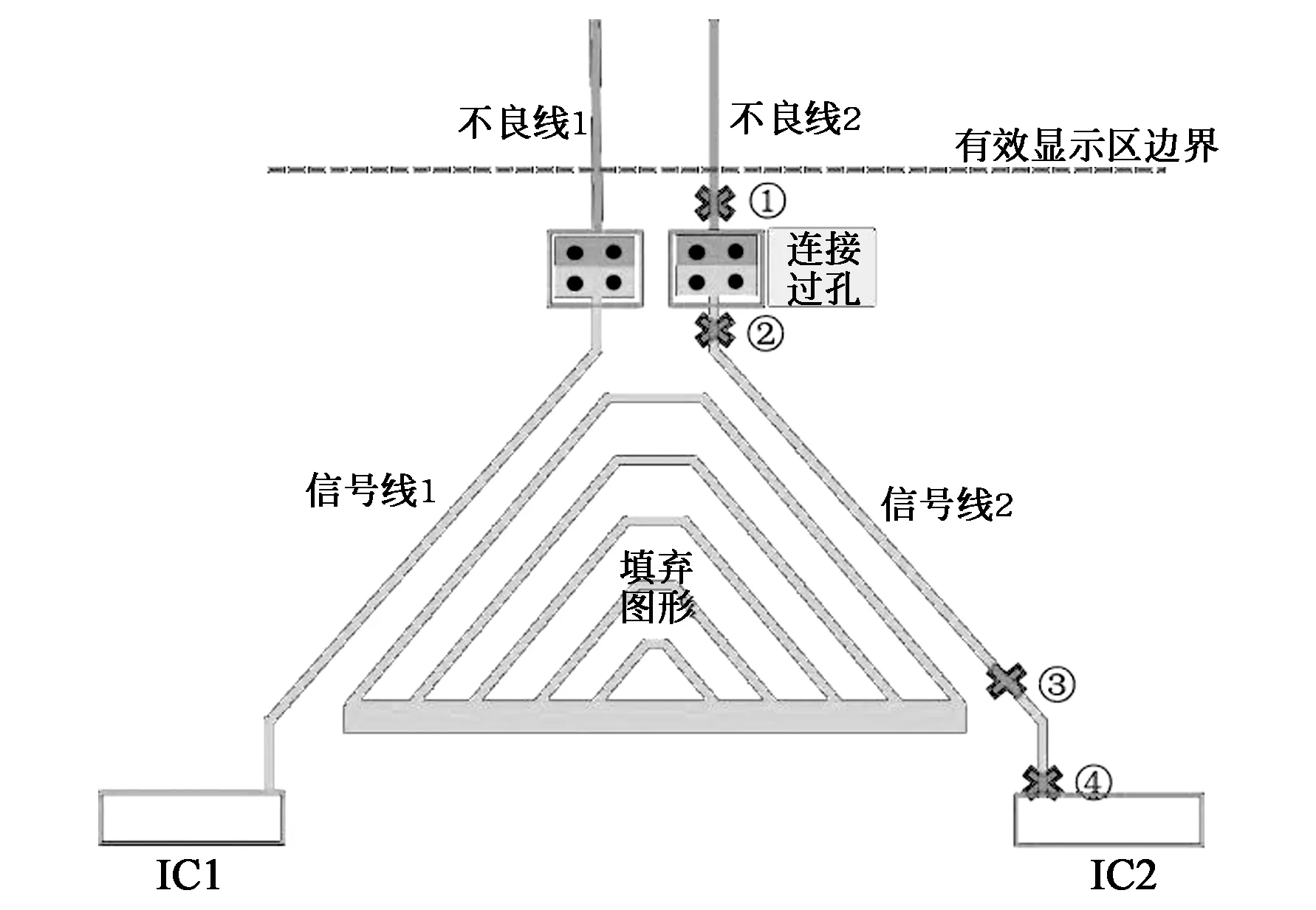

为了探寻填充图形对于此不良的影响,进而找到此不良的根本原因,针对此部分做了相应的切割测试。切割测试的示意图见图6。

图6 线不良位置切割验证示意图Fig.6 Line defect position cutting evaluation schematic diagram

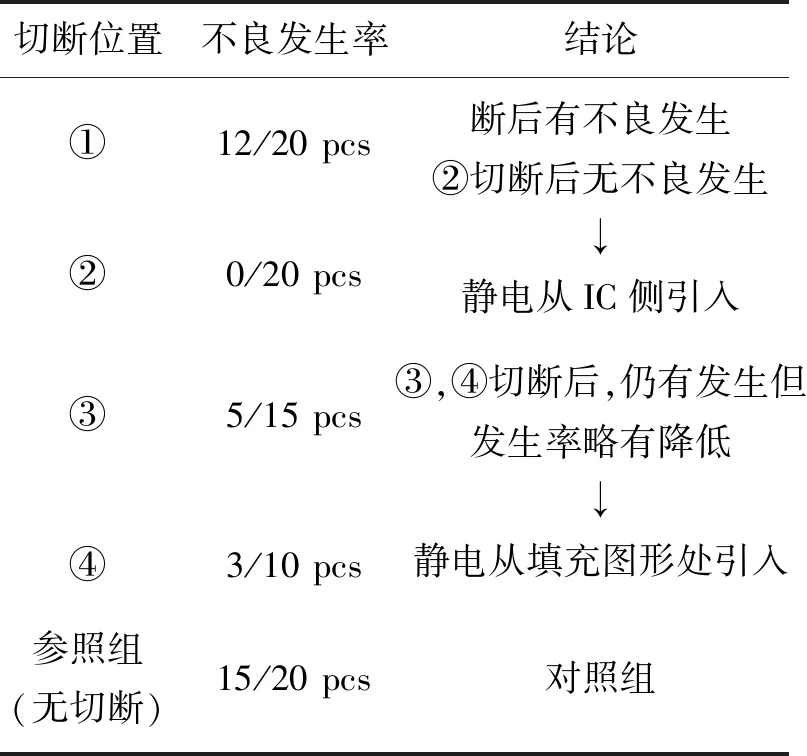

图中①、②、③、④分别为切割的位置,①、②、③、④切割打断各取20,20,15,10片面板进行验证,同时对比20片不做任何处理的面板结果。

表2是切割打断验证的结果。从表中可以看出,切断②的位置后,不良没有发生。此结果可以验证静电是从IC侧引入。切断③、④后,不良虽略有降低但是仍有发生。通过上述的测试可以看出,静电是由靠近IC侧的填充图形引入。

表2 切割验证结果Tab.2 Results of cutting evaluation

2.3 ESD发生机理分析

针对上述切割测试的结果,为了更好地理解ESD发生的原因,分析了摩擦工艺过程中ESD的发生机理。

根据原子结构的理论[8],原子由带正电的原子核和核外带负电的电子组成。静电产生的一个根本问题,是原子结构的不稳定性。在自然状态下,原子所含的正、负电荷是相等的,物质处于电平衡的中性状态,即不带电。在一定条件下(如接触、挤压、分离或受热等),外层的电子由于离核较远,受核束缚力小,物质中的这种电平衡状态被打破,丢失或得到电子,物质就由中性状态变为带电状态,如电荷不能很好地被移动,就形成了静电。

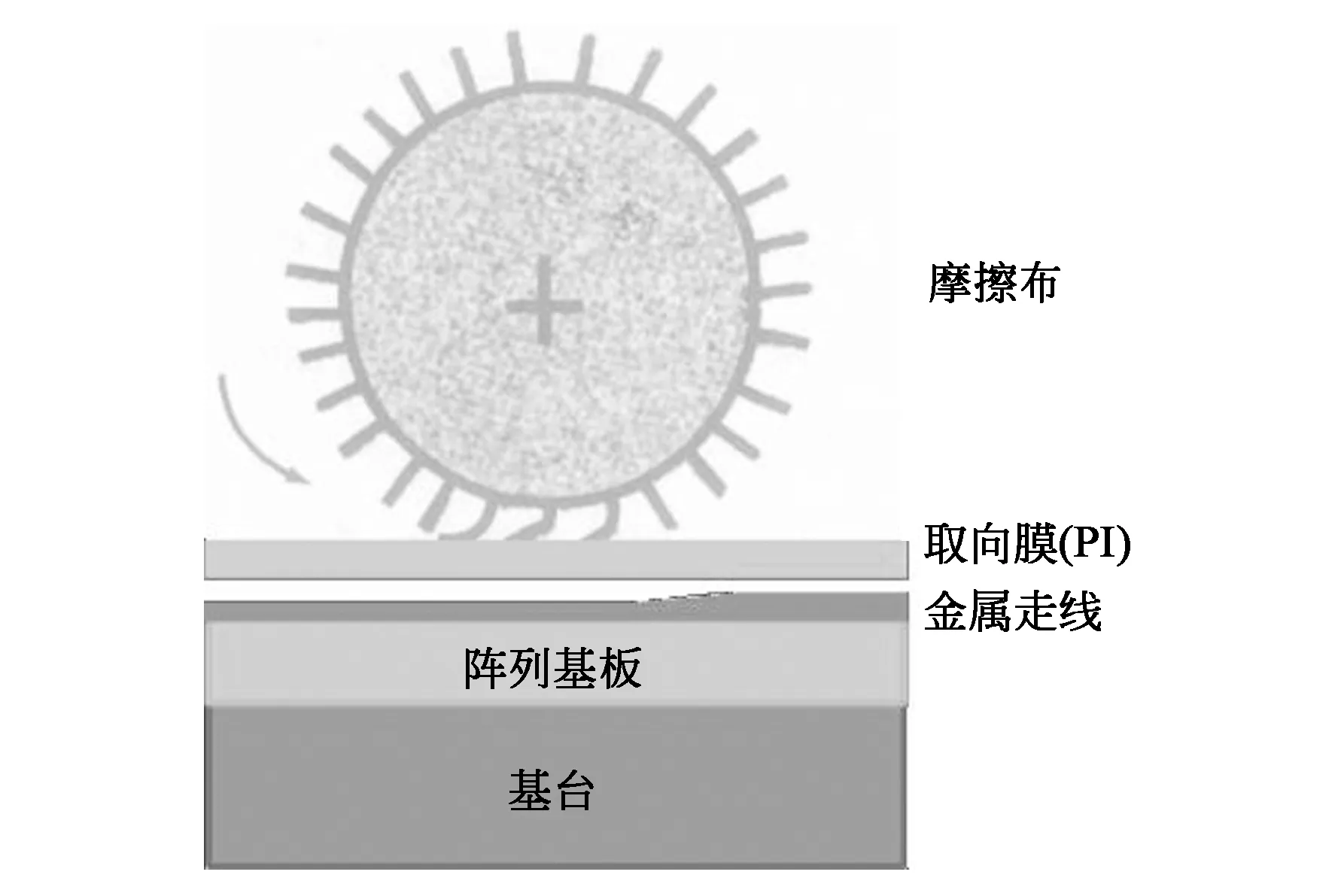

图7是摩擦工艺的示意图。摩擦设备将基板真空吸附在基台上,一边转动滚筒,一边使基台移动进行摩擦。

图7 摩擦工艺示意图Fig.7 Rubbing process schematic diagram

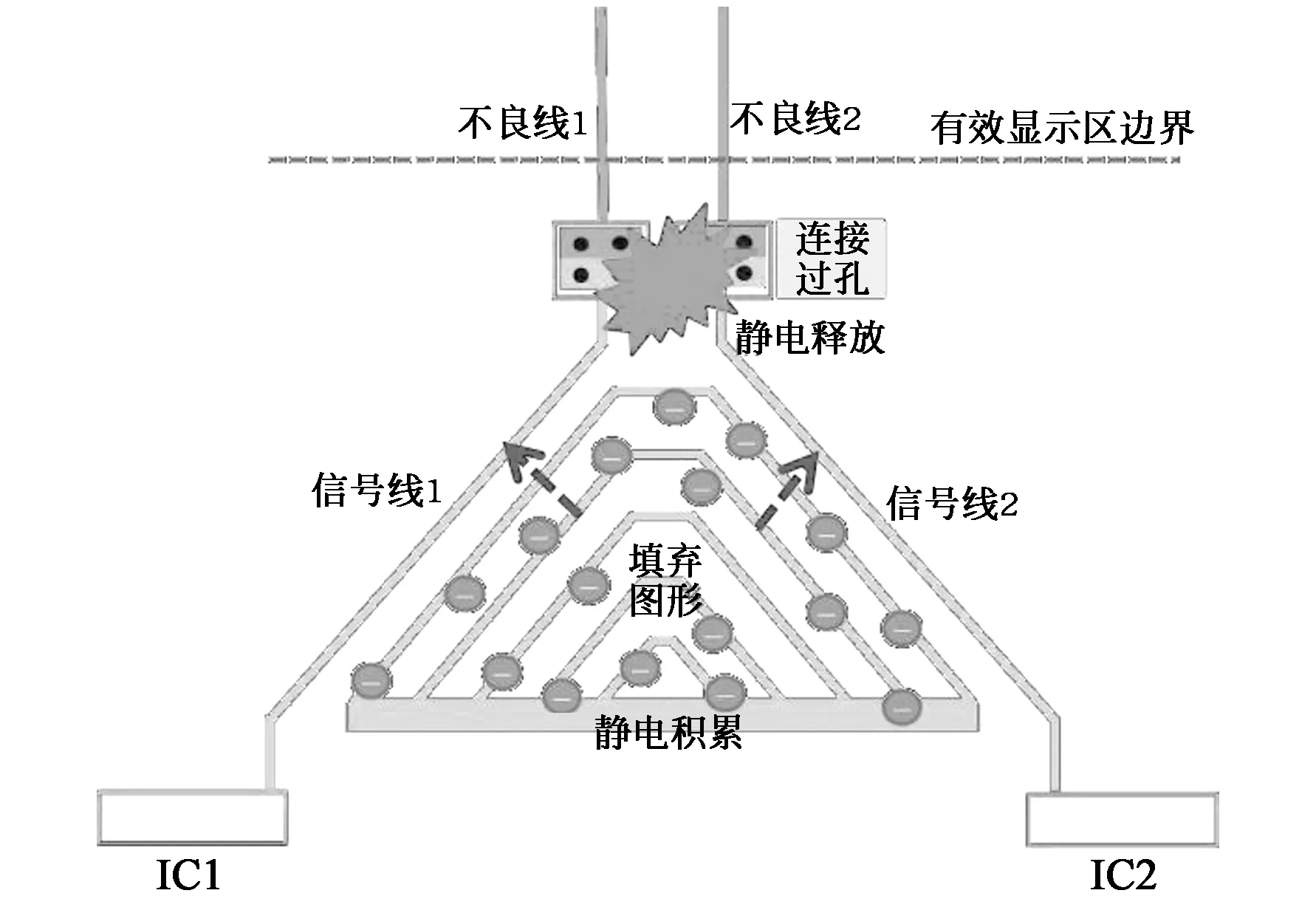

由于在阵列基板侧很多金属走线,并且随着产品分辨率的逐渐增加,金属走线在阵列基板的密度会越来越高。根据上述静电形成的理论,在摩擦布摩擦阵列基板的时候,就很容易在阵列基板和摩擦布上形成静电积累。由于该产品在IC1和IC2中间及IC3和IC4中间有较大面积的填充图形,摩擦工艺过程中,在经过一段时间的摩擦静电积累,在填充图形位置积累的静电量会越来越多。当填充图形上积累的静电到达一定的量后会寻找相应的释放路径,而与之相邻的两根信号线(信号线1和信号线2)就是最容易释放的位置。当静电释放到信号线1和信号线2上时,静电会在电阻最大的位置即连接过孔的位置进行释放。其静电释放的路径示意图如图8。

图8 静电释放示意图Fig.8 ESD discharge path schematic diagram

2.4 设计方案变更验证及结果

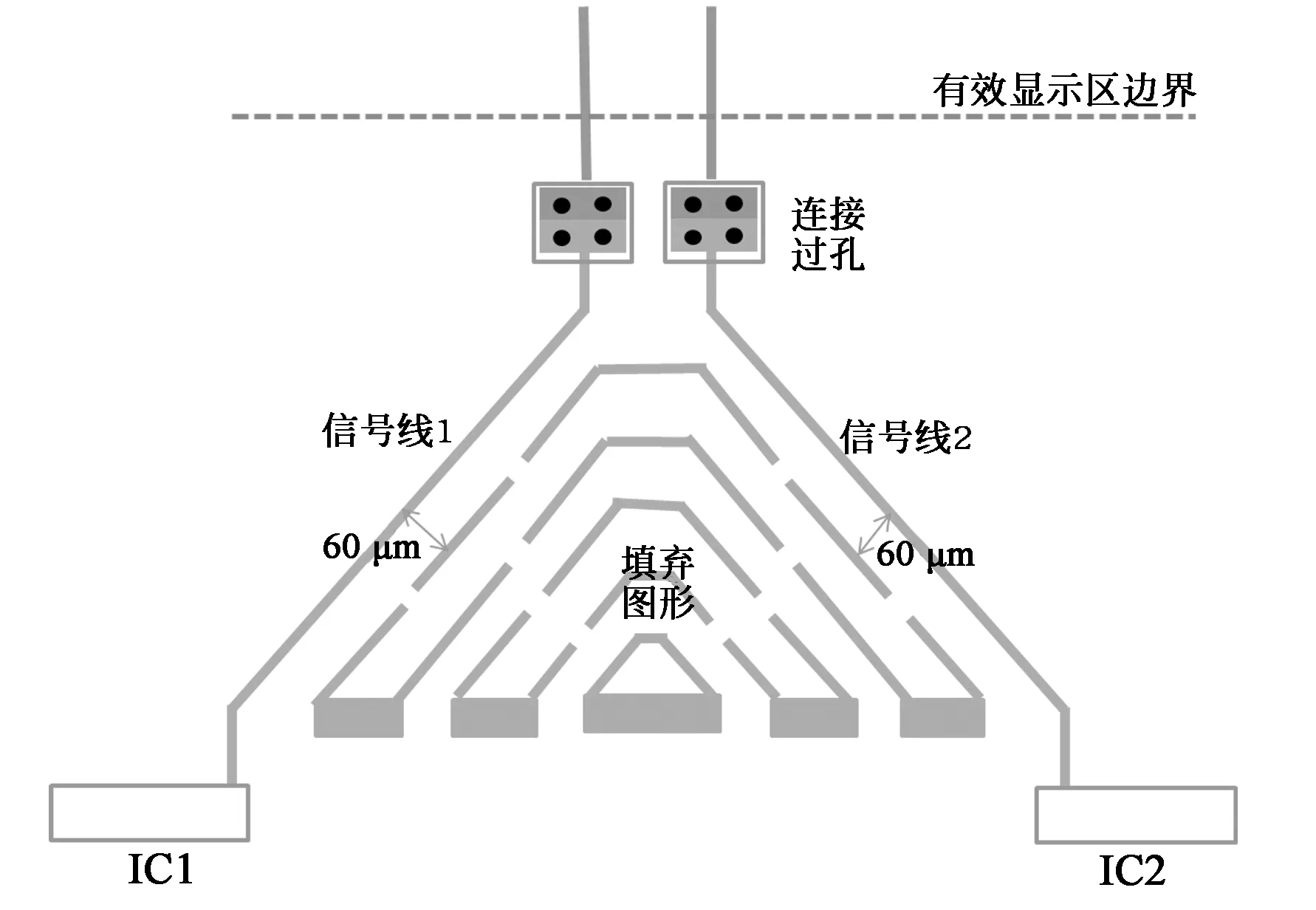

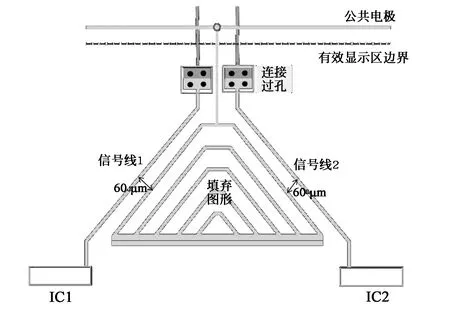

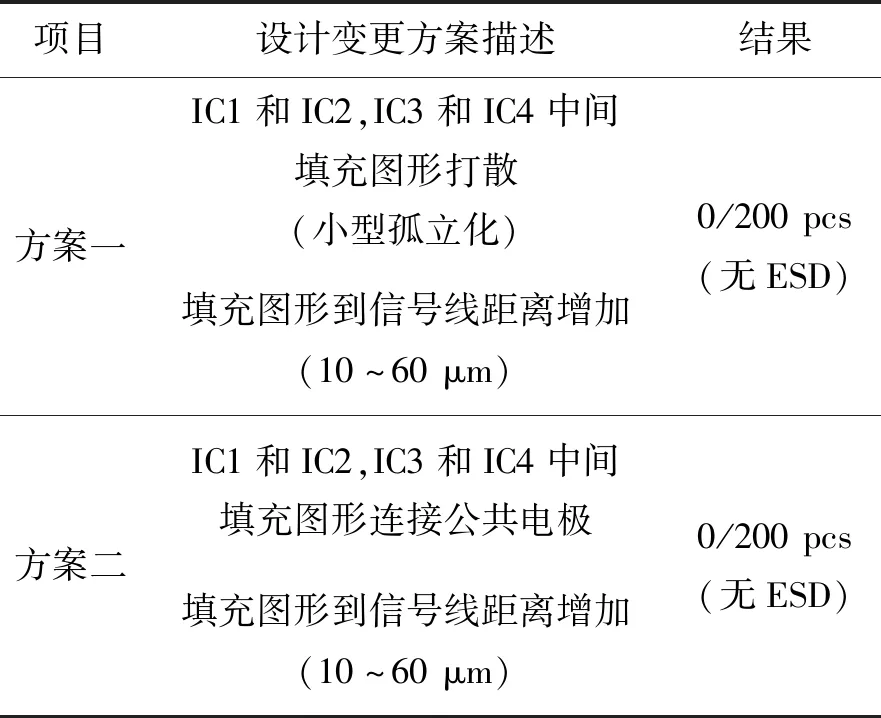

为了进一步验证填充图形的相关性,进而从设计源头上降低此线不良发生的风险,对设计方案进行了变更。设计变更包括以下两种方案:方案一,将IC1和IC2,IC3和IC4中间的填充图形打散(图形小型孤立化),并且增加填充图形到信号线的距离(10 μm增加到60 μm);方案二,将IC1和IC2,IC3和IC4中间的填充图形连接到面板内部公共电极,并且增加填充图形到信号线的距离为60 μm。公共电极信号为面板内部工作的基准信号,所有公共电极信号均连接到一起。图9和图10为方案一和方案二的示意图。

表3是设计方案一和设计方案二的验证结果,从实际的验证结果看,两种方案都能降低此线不良发生的风险,均没有ESD发生。

图9 设计变更方案一示意图Fig.9 Design change solution-1 schematic diagram

图10 设计变更方案二示意图Fig.10 Design change solution-2 schematic diagram

表3 设计方案变更验证结果Tab.3 Result of design change

2.5 结果分析

从设计变更方案一和方案二的结果看,降低ESD发生风险的方法主要有两个方向:

(1)减小填充图形的面积可以降低填充图形上静电积累的量;增加填充图形到信号线的距离可以降低填充图形上积累的静电释放到信号线上的风险;

(2)将填充图形连接到公共电极,当在填充图形处静电积累后,由于填充图形连接到公共电极,所以静电可以释放到面板内部均连接到一起的公共电极上,进而降低ESD发生的风险。

3 结 论

本文对摩擦工艺过程中的线不良进行了分析,通过切割验证、设计方案变更验证了降低ESD风险的两个方向。通过实际的验证结果分析我们发现,减小填充图形的面积或者将填充图形连接到公共电极,同时搭配增加填充图形到信号线的距离大于60 μm,可以大大降低ESD发生的概率,不良率由20%降低到0%。结果充分表明,此设计方案可应用于实际产品设计中以降低摩擦工艺过程中的ESD风险。