三维堆叠芯片电源分配网络电源完整性建模与仿真∗

胡 晋 王彦辉 张 弓

(江南计算技术研究所 无锡 214083)

1 引言

随着半导体集成电路工艺制程的不断跃升,在未来数十年左右的时间内,晶体管尺寸的缩减将受限于基本物理定律,继续通过缩减晶体管尺寸来提升半导体集成电路系统集成度将变得尤为困难。目前,基于硅通孔(TSV)的三维芯片堆叠技术已经成为一项可以实现超大规模集成电路集成度跨越式发展从而延续摩尔定律甚至超越摩尔定律的潜在技术解决方案[1~4]。

三维芯片通过TSV 实现多层芯片垂直方向堆叠与互连,可以显著提高半导体芯片的集成度,缩短互连长度,提高传输带宽。与此同时,芯片集成度、电源功耗及信号传输速率的大幅提升,也导致电源与信号噪声余量的显著减少,此外由于互连TSV 的引入将导致TSV 电感与芯片电容产生谐振效应,以及电源分配网络寄生分布特性所带来的电源地反弹或同步开关噪声等一系列电源完整性问题,对三维堆叠芯片电源完整性设计提出了严峻的挑战[5~11]。为此,本文针对三维堆叠芯片电源分配网络电源完整性仿真技术进行研究,在分析典型单层芯片电源地金属层物理结构的基础上建立单层芯片电源分配网络分析模型。随后建立多层芯片层间互连电源地TSV 对等效RLGC 电路模型,结合单层芯片电源分配网络分析模型,拓展建立堆叠芯片电源分配网络仿真分析模型。在电源完整性仿真分析中,利用数值分析方法,分别进行三维堆叠芯片电源分配网络频域阻抗特性与时域电源波动仿真,并且就芯片级滤波电容对堆叠芯片电源分配网络时域噪声的影响进行了分析。

2 单层芯片电源分配网络分析模型

开展三维堆叠芯片电源完整性仿真技术研究,首先需要针对单层芯片的电源分配网络进行仿真分析。当前超大规模集成电路芯片规模庞大,集成数十亿个晶体管,电源地网络异常复杂,对芯片级电源分配网络仿真分析方法以及分析工具都提出了巨大的挑战。本文利用芯片金属层电源地网格物理结构信息,建立简化的网格型单层芯片电源分配网络等效电路模型。

图1 为单层芯片网格型电源分配网络。为简化分析,芯片级电源分配网络由两个电源地金属层构成,分别为Metal1 和Metal2。在Metal2 层水平的电源线和地线以均匀间隔垂直布设,相应地,在Metal1 层垂直的电源线和地线以均匀间隔水平布设,电源与地通过Metal1层和Metal2层间过孔连接构成网格型电源分配网络。

图1 单层芯片网格型电源分配网络

图2 单层芯片网格型电源分配网络等效电路模型

图2 为由单层芯片网格型电源分配网络所建立的等效电路模型,其单元网格电路参数可由电源地金属层物理结构信息理论推导得到[12]。

其中,LP 为金属层线间隔,LW 为金属层线宽,T1、T2分别为Meta1和Metal2层层厚,H1、H2分别为介质层层厚,σCu为金属铜的电导率,εrμ0分别为介电常数和磁导率,Cor为趋肤效应因子。

在芯片级金属层电源地网格规划中选择较大的线宽,同时缩小电源地线间隔,可以降低电源分配网络的频域阻抗,进而提高芯片电源分配系统的稳定性。与此同时,需要考虑的是芯片级金属层电源地网格规划必须要结合工艺制程、芯片面积、布局规划、电源供电、功耗控制等多种因素来综合考量。此外,在金属层中插入片上滤波电容也可以直接有效地降低芯片电源分配网络的频域阻抗特性。

3 三维堆叠芯片电源分配网络分析模型

3.1 电源地TSV对建模

硅通孔是三维堆叠芯片的重要组成部分,单层芯片通过硅通孔层间互连构成三维堆叠芯片。相应地,三维堆叠芯片电源分配网络分析模型可以由单层芯片电源分配网络模型及电源地TSV 对RLGC模型级联而得到,简化起见,这里忽略了信号与电源地之间的相互影响。电源地TSV 对RLGC 模型由信号TSV 对模型[13]引申而来,如图3 所示。其中,模型参数CUnderfill、CIMD、CInsulator、CBump、CSi、GSi、RTSV、RBump、LBump与信号TSV 对RLGC 等效电路模型相同,具体计算方法可参考文献[13],限于篇幅,这里不再赘述。所不同的地方在于需要考虑电源地TSV 之间的耦合效应对硅通孔寄生电感的影响。

电源地TSV 寄生电感LTSV可以由式(4)~(6)计算得到:

其中,LST为硅通孔自电感,LMT为硅通孔互电感,dTSV、hTSV、μr,TSV、pTSV分别为硅通孔的直径、高度、磁导率以及TSV的间距。

图3 电源地TSV对RLGC模型

3.2 网格型电源地TSV对互感

在分析网格型电源分配网络时,需要进一步考虑相邻多个电源地TSV对所带来的互感耦合效应。

图4 为网格型电源分配网络电源地TSV 对互感计算的示意图,其电源地摆放采用典型的交错排布布局。图中LTP为电源TSV 电感,LTG为地TSV电感,LMT1,2,3分别为水平、垂直和对角方向上的互感。在电源地网格型交错分配条件下,水平和垂直方向上电源电流同向流动,LMT1,2为正值,而在对角方向上电源电流反向流动,LMT3为负值。因此,位于网格阵列中心区域的电源TSV 电感LTP可以通过式(7)计算得到,LMT1,2,3可通过式(6)计算得到,位于网格阵列中心区域的地TSV 电感LTG可以参照式(7)计算,而位于网格阵列边沿区域的电源地TSV电感可以类似计算得到。

图4 网格型电源地分配网络硅通孔互感

4 电源完整性仿真

4.1 频域仿真

在频域仿真中,利用前文所述方法计算电源分配网络频域阻抗曲线,对比单层芯片与三维堆叠芯片的频域阻抗特性。考虑两层芯片堆叠,芯片尺寸为1000μm×1000μm,金属层层厚T2、T1分别为1μm 和0.8μm,介质层层厚H2、H1分别为0.6μm和4μm,线宽LW 与线间隔LP 分别为10μm 和25μm。芯片间互连TSV 高度为50μm,电源地TSV对采用交错布局,水平与垂直方向间隔为100μm。分别计算得到电源地TSV对的寄生电感,结合单层芯片电源分配网络等效电路模型及层间互连电源地TSV 对RLGC 模型可最终得到多层堆叠芯片的电源分配网络频域阻抗曲线。

图5 单层与堆叠芯片电源分配网络频域阻抗特性

图5 为所得到的单层芯片与三维堆叠芯片电源分配网络频域阻抗对比曲线。图中可以看出,堆叠芯片由于堆叠了两层芯片,芯片电地网格寄生电容翻倍,导致电源分配网络频域阻抗在较低频段(1GHz~10GHz)内阻抗降低,而由于层间互连TSV的引入导致TSV电感与芯片电容产生谐振,从而在较高频段(>10GHz)内产生频域阻抗谐振点。进一步比较堆叠芯片内不同位置的电源分配网络频域阻抗特性,可以看出底层芯片与顶层芯片两者的频域阻抗曲线近似相同,由于电源网格级联,顶层芯片电源分配网络寄生电感大于底层芯片,导致电源分配网络频域阻抗谐振点向低频方向移动。

4.2 时域仿真

频域阻抗性能仿真主要表征电源分配网络频域LCR寄生参数特性,三维堆叠芯片电源分配网络性能评估还需要结合负载翻转电流特性开展精确的时域电源波动仿真分析。由三维堆叠芯片电源分配网络频域分析所得到的多端口S 参数模型频带宽、动态范围大,直接级联多端口S 参数模型并利用DesignerSI、Speed2000 等电路仿真器[14-15]进行复杂电源分配网络时域电路仿真,不仅导致仿真时间过长、仿真效率偏低,更易于激发无源及稳定性问题[16],导致仿真失效。

这里利用Matlab 数值分析方法对三维堆叠芯片电源分配系统时域电源波动响应进行分析。具体做法为首先对负载翻转电流进行数字时域采样,随后对时域变化电流进行快速傅立叶变换得到频域电流,频域电流与前文三维堆叠芯片电源分配网络频域分析所获得的电源分配系统频域阻抗矩阵点乘后再进行逆傅立叶变换得到时域电源压降,理想输入电压源减去电源压降最后得到堆叠芯片电源分配系统实际的时域电源波动响应。

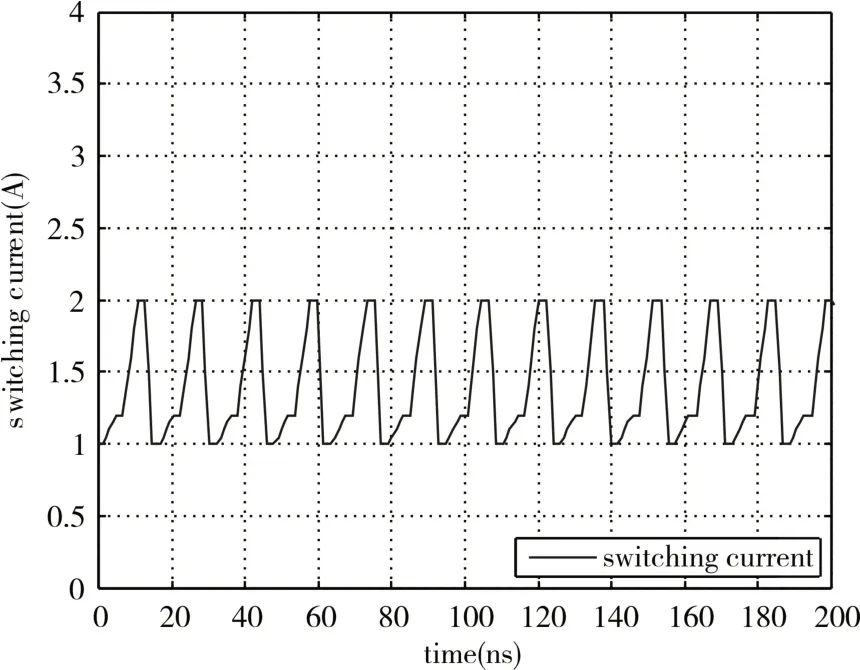

图6 为堆叠芯片负载翻转电流波形,考虑锯齿波形负载翻转电流,电流周期为15.6ns,电流幅度在1A~2A 范围内变化,时域仿真时间为200ns,理想输入电压源为0.9V,采用1024 点快速傅里叶变换进行分析。三维堆叠芯片层数、尺寸、线宽与线间隔等分析条件与前文所述堆叠芯片电源分配网络频域分析相同。

图6 堆叠芯片负载翻转电流

首先分析两层芯片电流同时翻转条件下,底层芯片与顶层芯片电源分配网络的时域电源波动响应,如图7 所示。可以看出,当两层芯片负载电流同时翻转时,顶层芯片与底层芯片电源分配网络均会有负载翻转电流流过,同时两层芯片间电流亦可呈叠加特性,导致在顶层芯片与底层芯片电源分配网格上形成较大的电源噪声,其无论是电源直流压降还是交流摆幅都无法满足电源分配网络的设计要求。

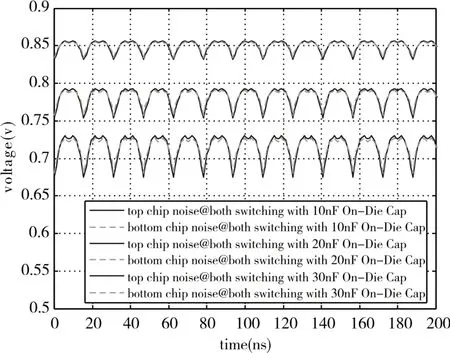

为了降低三维堆叠芯片负载电流同时翻转所产生的电源噪声,需要设计稳健的片上电源分配系统,增加芯片级滤波电容容量,同时结合芯片电流密度分布优化片内滤波电容摆放。这里分别考虑底层与顶层芯片片上滤波电容为10nF、20nF 和30nF 三种情况,同时为简化分析,片上滤波电容采用全芯片均匀配置。图8 为增加芯片片上电容后得到的堆叠芯片电源分配网格时域波动,可以看出,在芯片金属层插入片上滤波电容可以直接有效地降低三维堆叠芯片电源分配网络的时域电源波动。在实际设计中,芯片电容摆放也涉及到芯片面积规划、漏电功耗控制等多种因素,需要综合考虑。

图7 堆叠芯片时域电源波动

图8 堆叠芯片时域电源波动(增加芯片片上电容)

5 结语

本文研究三维堆叠芯片电源分配网络电源完整性建模与仿真技术。首先根据芯片金属层物理结构建立单层芯片电源分配网络分析模型与电源地TSV 对RLGC 等效电路模型,并进一步拓展建立三维堆叠芯片电源分配网络分析模型,随后针对三维堆叠芯片电源分配网络进行时频域电源完整性仿真,分析电源分配网络频域阻抗特性、时域电源波动以及芯片级滤波电容对时域噪声的影响。本文所述方法可以全面准确地分析三维堆叠芯片电源分配网络性能特性,为三维堆叠芯片电源完整性设计提供有效指导。