一种舰载传感器图像编码实现方法

周国良,彭益智,曲 伟

(江苏自动化研究所,江苏 连云港 222061)

0 引言

在舰船火力与指挥控制系统中,采用数字视频总线准确、实时地传输传感器视频图像信息,实现多传感器图像信息共享。传感器视频图像信息先在前端图像处理系统进行编码处理,然后通过数字视频总线实时传输,在指挥终端解码实现图像资源共享。随着视频图像高清化发展趋势,传感器采集的图像数据量激增,为实现图像数据实时传输,对图像处理系统的数据处理能力和数字视频总线传输能力提出了更高的要求。针对舰船传感器视频图像高清化和传输实时化需求,本文在分析多核DSP 并行处理和JPEG 编码算法的基础上,提出了一种基于多核DSP 的JPEG 图像编码实现方法,并实现了多核DSP 核间高效通信和任务级并行处理。

1 TI TMS320C6678 多核处理器

为满足移动网络领域对通道密度及高质量媒体服务日益增长的需求,德州仪器(TI) 推出TMS320C66x 系列数字信号处理器,提供系统级的低成本、低功耗和高密度媒体解决方案。

TMS320C6678(简称C6678)处理器基于创新型Key Stone 构架,集成了8 个C66x 内核,支持高性能信号处理应用。每个内核主频1 GHz,最高可达1.25 GHz,可以进行160 km/s 次浮点运算,功耗不到10 w。每个内核拥有32 kBL1P、32 kB L1D、512 kBL2内存,4 MB 多核共享内存,8 192 个多用途硬件队列,支持DMA 传输。处理器网络性能优越,支持双千兆网口,带有由1 个数据包加速器和1 个安全加速器组成的网络协处理器[1-2]。此外,C6678 的拓展资源丰富,支持PCle、Serial RapidIO[3]、Gigabit Ethernet 以及HyperLink 等多种高速接口。

2 JPEG 编码并行实现框架

2.1 JPEG 算法简介

JPEG 是第一个国际图像压缩标准,能够在提供良好的压缩性能的同时,具有比较好的重建质量,被广泛应用于图像、视频处理领域,尤其适用于互联网和数码相机,网站上80 %的图像都采用了JPEG 压缩标准。

该编码算法步骤如下:源图像数据分成8×8的数据块,通过DCT 变换将8×8 的数据块变换为DCT 系数,数据块按从左到右、从上到下的顺序处理,根据量化表对DCT 系数进行量化,DCT 系数按Z 字形方式排序,其中直流系数采用差分脉冲编码,交流系数采用行程编码,最后经过二次编码输出压缩图像数据[4]。

2.2 基于多核DSP 的JPEG 编码并行实现

JPEG 编码算法分解为以下7 个模块:

1)初始化;2)DCT 变换;3)量化;4)Z 形扫描;5)直流系数(DC)编码;6)交流系数(AC)编码;7)熵编码。

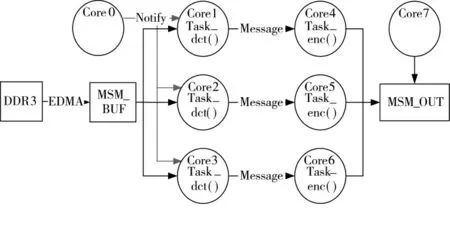

考虑模块间的耦合性、结合性以及模块间通信,将DCT 变换、量化和Z 形扫描合并为DCT 子系统,将DC 编码、AC 编码和熵编码合并为编码子系统,将模块或子系统映射到多核DSP 内核上。JPEG编码算法采用任务并行模式[5],将算法的模块或子系统映射到C6678 处理器内核上,应用多核DSP 并行程序设计方法实现算法的任务级并行处理和核间高效通信。

图1 编码并行实现框图

DCT 子系统和编码子系统涉及大量复杂运算,直接制约了编码速度。因此,采用了3 条任务并行流水线来进行处理,分别为CORE1 和CORE4、CORE2 和CORE5、CORE3 和CORE6。CORE1、2 和3 并行进行DCT 变换,后级的CORE4、5 和6 分别接收CORE1、2 和3 的数据,进行编码,这样把算法映射到多个DSP 核,变换与编码流水线并行处理,提高了编码速度。具体实现机制如下:

1)初始化和同步[6-9]

C6678 处理器共有8 个C66x 内核,命名为CORE0~CORE7,每个内核分别进行初始化,然后同步执行。

* CORE0 初始化:接收源图像数据并存储在DDR3 上、初始化6 个EDMA3[10-11]通道;

*CORE1、2 和3 初始化:根据设定的图像压缩质量初始化量化表,CORE1、2 初始化亮度量化表,CORE3 初始化色度量化表;

* CORE4、5 和6 初始化:直流、交流系数Huffman 编码表初始化,生成相应的直流、交流系数Huffman 码字;

*CORE7 初始化(保留):传输压缩图像数据初始化。

每个内核初始化结束,调用Ipc_start 函数进入同步等待状态,直到所有内核都调用Ipc_start 函数进入同步状态,各个内核上的程序继续执行。

2)内核间任务调度和通信

根据SYS/BIOS 实时操作系统线程调度机制[7-9]和内核间通信机制,为并行JPEG 编码系统选取合适的任务调度方式,并实现内核间高效通信。CORE0 与CORE1、2、3 间的通信采用最小通信模式,CORE1 与CORE4、CORE2 与CORE5、CORE3与CORE6 间的通信采用消息传递模式[5]。

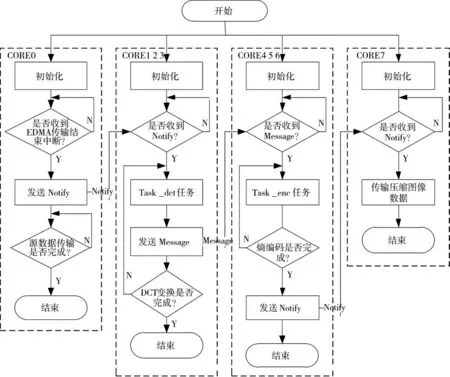

基于C6678 的并行JPEG 编码系统的任务调度过程如下:

*各个内核初始化;

*EDMA 完成从DDR3[12-13]到MSM_BUF 的源图像数据传输后,CORE0 发送Notify 到CORE1、2和3;

* CORE1、2 和3 接收Notify,然后分别调用Task_dct 任务。Task_dct 任务从MSM 缓冲区[14]取源图像数据,并完成DCT 变换、量化和Z 字形扫描后,发送包含DCT 系数的Message 到对应的CORE4、CORE5 和CORE6;

* CORE4、CORE5 和CORE6 接收Message,然后分别调用Task_enc 任务。Task_enc 任务从Message 中读取DCT 系数,并对DC 和AC 系数编码,最后Huffman 编码输出压缩图像数据到MSM_OUT 存储区。

基于C6678 的并行JPEG 编码系统的整个处理流程如图2 所示。

3 测试试验与结果

3.1 算法核心组件测试

本文设计的基于C6678 的JPEG 编码系统采用任务并行方式,各内核执行的任务单一,可以针对具体的任务进行优化。由于不同任务的计算复杂度不同,任务并行很难实现各内核间实时负载平衡,系统性能受限于计算负载最大的处理核[15]。

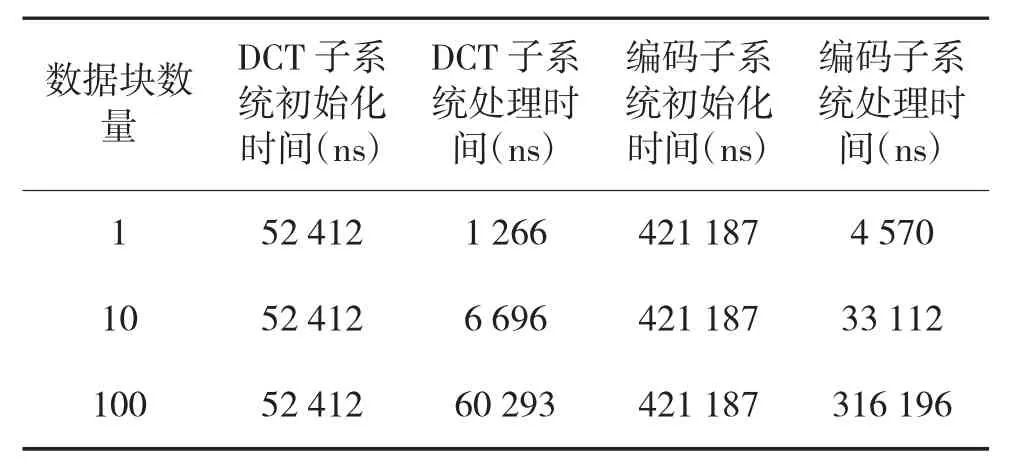

JPEG 编码算法中计算量较大的模块是DCT 子系统和编码子系统,测试这两个子系统的运行时间(包括初始化时间和处理时间),如DCT 子系统中,初始化时间对量化表进行初始化,处理时间对数据块进行DCT 变换、量化和Z 字形扫描等。测试数据为多个8×8 的源图像数据块,实验结果如表1 所示,测试平台是C6678 处理器,主频是1 GHz。

表1 DCT 与Huffman 子系统与测试结果

程序执行时,各个子系统只初始化一次,因此,初始化时间对于子系统的计算量影响有限。DCT 子系统处理一个数据块的处理时间是1 266 ns,而编码子系统的处理时间是4 570 ns,编码子系统的计算量远大于DCT 子系统的计算量,编码子系统制约了系统的实时处理能力。随着数据块数量的增加,子系统的初始化时间不变,但单个数据块的平均处理时间略有下降。若想进一步提高基于C6678 的并行JPEG 编码系统的实时处理能力,最好的方法是继续优化编码子系统。

3.2 系统性能验证

图2 系统处理流程图

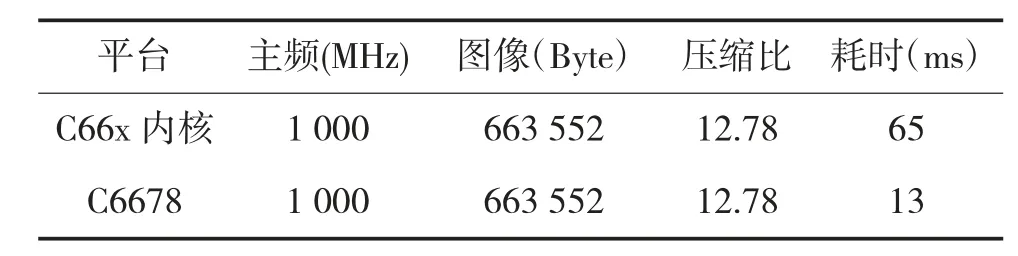

把相同复杂度的JPEG 编码算法程序分别在单核DSP 和多核DSP 处理器上运行,单核DSP 处理器采用C6678 处理器的单个C66x 内核,多核DSP处理器采用C6678 处理器。对比编码系统的处理能力,实验结果如表2 所示。测试源图像来自光电跟踪仪,分辨率为768*576。

表2 系统测试结果

JPEG 编码算法复杂度基本相同(为实现算法的并行处理,多核DSP 平台上算法略有改动),比较不同JPEG 编码系统处理同一源图像数据的时间,基于C6678 的并行JPEG 编码系统的运行时间为13 ms,系统的处理能力是基于单核系统的5 倍。

4 结论

基于TI 公司C6678 处理器,采用任务并行模式,将算法的模块或子系统映射到C6678 处理器多个内核上,实现了JPEG 编码算法的任务级并行处理和核间高效通信。测试结果表明,基于C6678 的JPEG 编码系统是基于C66x 单核系统的5 倍,这说明该系统充分发挥了多核DSP 的性能优势,大幅度缩短了压缩编码时间,提高了视频图像压缩效率。