某型号八位微控制器失效类型分析

王天畅,李岳林

(1.中国电子科技集团公司第四十七研究所,沈阳110000;2.大连交通大学电气信息工程学院,大连116028)

1 引 言

某型号八位微控制器电路,作为一款高效率的CMOS 微控制器芯片,采用了高密度非易失性存储器(Non-Volatile Memory, NVM)工艺制造,在单芯片上具有集成了高效的标准MCS-51 指令系统的八位CPU。该CPU 支持6 时钟和12 时钟模式。芯片内部含有 64 kByte 的 ISP(In-System Programmable)和IAP(In-Application Programmable)Flash 以及 1 kByte RAM。片上Flash 允许程序存储器在系统可编程和在应用可编程,ISP 功能允许用户在线下载新的程序,而IAP 则允许用户在应用时获取和更新程序。

在使用某型号八位微控制器的过程中出现过很多导致器件失效的问题,从整体来看可以分成器件外部损伤、内部软件缺失、器件内部损伤三大类。器件的外部损伤主要包括管脚损伤与沾污,被沾污或损伤的管脚在实际应用中会出现接触不良的情况,导致器件的工作状态不稳定,甚至根本无法工作;内部软件缺失主要指未烧录驱动程序,这会使得器件无法驱动,不能进入工作状态;器件内部损伤主要指静电击穿和浪涌这种过电应力对器件内部结构造成损伤的情况,这会导致器件内部结构遭到破坏,难以正常工作。

针对这些问题,需要进行失效分类和失效机理分析,应用正确的失效分析方法,形成排查纠正措施,以期更快速有效地解决问题。

2 电路结构

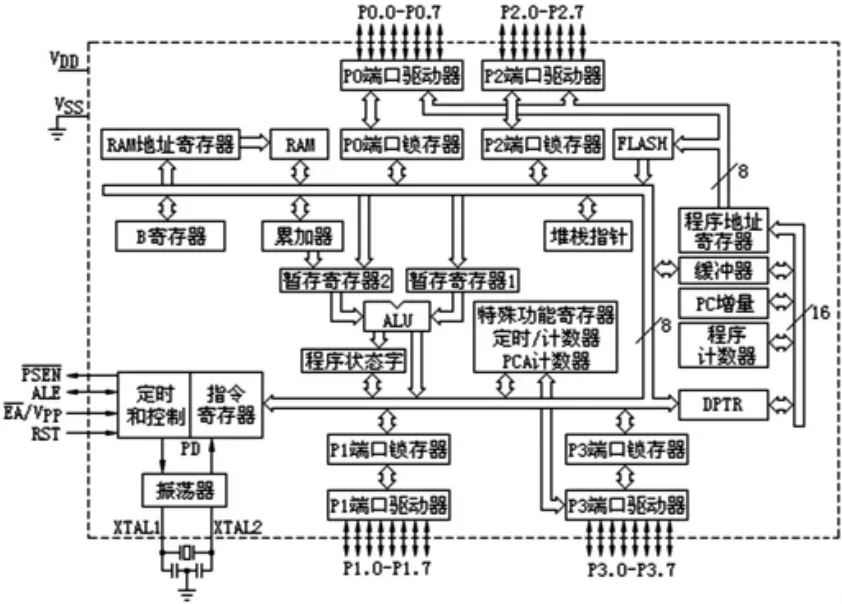

某型号八位微控制器功能框图如图1 所示,主要由CPU、存储器和外设等部分构成。其中存储器有64kByte Flash 和1kByte SRAM;外设有全双工增强型通用异步接收机、计数器0/1/2、可编程逻辑阵列、看门狗、可配置I/O 端口0/1/2/3 和振荡器。该八位微控制器能够方便地组装成智能式测控设备、各种智能仪表和规模应用系统,也可实现多机和分布式控制。

图1 某型号八位微控制器功能框图

3 失效类型及分析方法

目前常用的失效分析方法有电测试技术、显微形貌分析技术、显微结构分析技术、应力试验技术、解剖制样技术等。该款八位微控制器电路的主要失效类型分为:管脚损伤与沾污、未烧录驱动程序、静电击穿和浪涌。此处主要使用显微形貌分析技术、电测试技术以及解剖制样技术[1],从器件的外观、驱动程序和内部结构三个角度进行失效分析。

3.1 管脚损伤与沾污

显微形貌分析技术是通过光学显微镜(OM)、扫描电子显微镜(SEM)、透视电子显微镜(TEM)、原子力显微镜(AFM)等分析仪器,研究各种材料的显微组织大小、形态、分布、数量和性质的一种方法[2]。

管脚(即Pin)是从集成电路内部引出与外部电路相连的引线,其损伤会直接对元器件功能造成影响,因此对其进行检查十分有必要。

用肉眼比对检查失效元器件与良好元器件,可以观察到机械损伤、管壳变色或封装裂缝等异常情况。有时管脚表面会存在着更加细微的沾污或损伤,仅靠肉眼难以察觉,此时即需要使用4~80 倍的立体显微镜,或者更大倍数的金相显微镜来观察管脚部位。

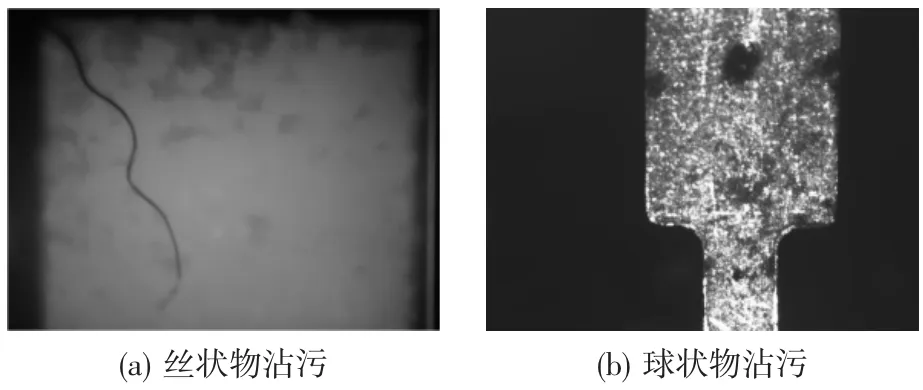

观察到的两种管脚沾污如图2 所示。可以明显看出,电路管脚存在的异物有丝状与球状之分。其中丝状异物使用洗耳球可以去除,燃烧后散发蛋白质燃烧的臭味[3],可推断为运输转移过程中粘连的毛发;球状异物无法用洗耳球清除,整体呈现烧结状态,推断应为防静电海绵在高温状态下的残余。

图2 显微镜下观察到的管脚沾污

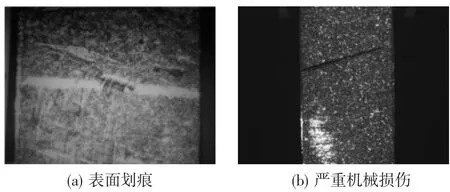

观察到的两次机械损伤如图3 所示。图3(a)中见到的是管脚表面(根部)划痕,该划痕比较明显,但引线表面无镀金层缺失现象,经系统测试合格,证明该损伤对电路功能无明显影响;图3(b)划痕较为严重,金层已遭到破坏,进行系统测试时出现连接不稳定现象,证明该损伤已对电路功能造成较大影响。由此可见,利用显微形貌分析技术对失效元器件进行检查十分必要。

图3 两种不同程度的机械损伤

3.2 未烧录驱动程序

此处选取的该款微控制器为仿制国外Philips公司的P89C51RD2 电路,可进行原位替代。在研制过程中,为保证电路稳定性,在时序写入和时序擦除方面进行了更严格的约束,此外还按照新的时序要求自主研发了专用并行编程器,在供货前烧录驱动程序,同时向用户提供自主设计开发的专用并行编程器,以方便客户烧录程序[4]。

在实际操作过程中,如果使用专用编程器烧录用户程序结果正常,但使用Flash Magic 软件烧录用户程序显示连接失败,且擦除原程序后无法再次烧录,则表明该电路出厂前未烧录驱动程序。此时重新烧录驱动程序即可正常使用。

3.3 静电击穿

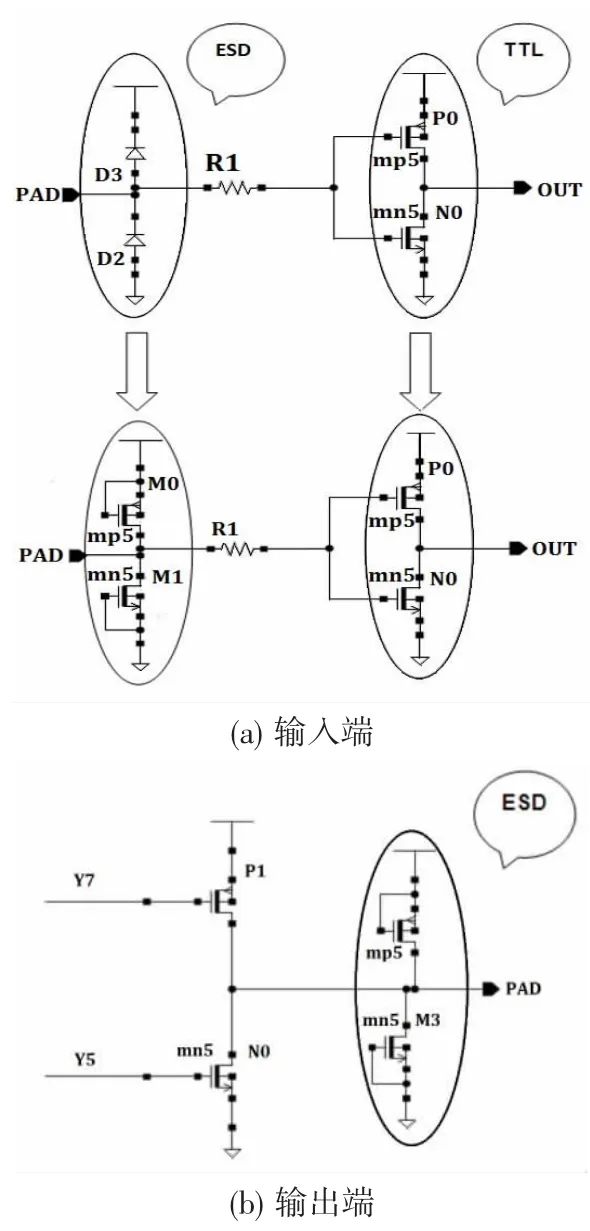

电测试技术是无损失效分析中最重要的步骤,随着集成电路的规模越来越大,利用自动测试设备(ATE)对集成电路进行测试越来越成为失效分析工作的重点。静电释放(Electro-Static Discharge, ESD)是造成集成电路失效的主要原因之一[5]。了解ESD机理并采用合适的方法加以预防,对提高集成电路可靠性有巨大意义。在该型号八位微控制器的端口内部,抗ESD 设计采用二极管结构,其输入输出端口如图4 所示。

图4 端口内部抗ESD 设计

二极管本身具有单向导通性,如果加载在二极管上面的反向电压超过它的最大承受值,反向电流会急剧加大,二极管会失去单向导电性,即发生所谓的击穿[6]。击穿发生时,端口对地和对电源二极管特性消失,二极管处于失能状态,导致电源和地端口ESD 失效, 在端口抗静电结构附近出现热点,导致NMOS 管烧损,对电路内部尤其是临近端口造成影响。在此状态下,该电路的P0.0 端口可能会失效,20 脚VSS与40 脚VCC可能会短接,电路受到不可恢复的损伤。利用电测试技术,测量失效端口是否对电源地短接,可以为失效分析提供有效依据。

3.4 浪涌

浪涌通常由自然界雷电、电网过压、开关打火、空间静电、电源系统(尤其是带有很重的感性负载)开关切换时引起的,是一种上升速度高、持续时间短的尖峰脉冲。浪涌对微电子芯片造成的损坏,轻者干扰芯片正常工作,重者造成芯片永久性损坏。例如感应雷(雷电感应或感应过电压)在RS-485 传输线上引起的瞬变干扰,其能量可在瞬间烧毁连结传输线上的全部器件[7]。

由于电子元器件封装材料和多层布线结构的不透明性,对于芯片内部的观察很多时候必须依赖于解剖制样技术。解剖制样技术主要过程包括:打开封装、去钝化层,有时候还需要去层间介质,保留金属化层及其下方介质,以及硅材料,然后采用剖切面技术和染色技术,进一步观察芯片内部缺陷[8]。

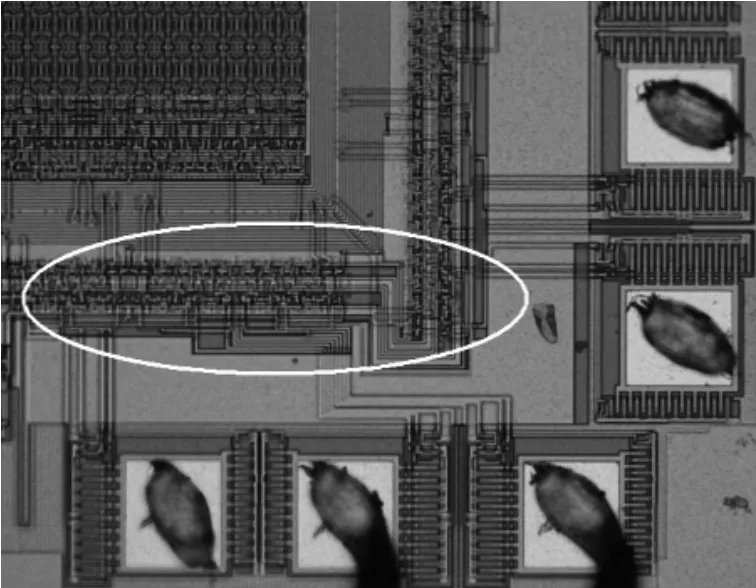

某失效电路P1.7 端口无法正确输出用户原程序所设计的占空比波形。对其进行功能测试,结果为P1.7 端口不合格,经过后续检查,X 光、密封性、DPA检测都合格,开盖后发现故障电路芯片表面与P1.7端口相连的驱动管处有烧毁形貌。开盖后芯片表面放大形貌如图5 所示。

图5 开盖后芯片表面放大形貌

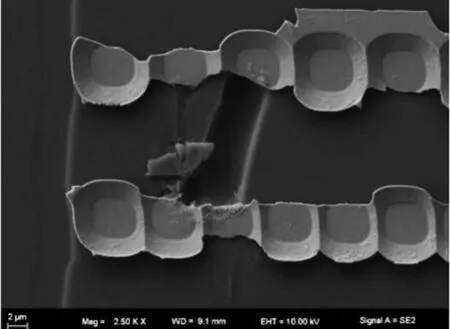

为做更进一步的分析,利用解剖制样技术进行去层检查。结果显示该驱动管在芯片有源区呈现击穿形貌,如图6 所示。去层后有源区层SEM 形貌如图7 所示。

图6 去层后有源区层击穿部位放大形貌

图7 去层后有源区层击穿部位SEM 形貌

通过显微镜观察芯片表面与P1.7 端口相连的驱动管Q3,发现此处有烧毁形貌。去层检查结果显示该驱动管在芯片有源区呈现击穿形貌。出现烧毁形貌是由于故障电路P1.7 端口引入了浪涌,导致芯片内部驱动管被击穿,引发失效,最终使得P1.7 端口无法正确输出用户原程序所设计的占空比波形。至此,将故障定位在P1.7 端口由于浪涌引入大电流导致芯片内部驱动管被击穿导致失效。

4 结束语

在简要介绍某型号八位微控制器芯片四种失效类型及分析方法的基础上,将其作为八位微控制器芯片的典型示例,对相关失效问题展开分析并借助显微手段辅助取证,精确定位问题所在。所做分析不仅有助于更快速精准的解决其本身问题,也可为其他同类型器件提供参考。