基于CPLD+FLASH通用快速的FPGA配置方案*

袁 君,李治辉,姚 超

(中国电子科技集团公司第三十研究所,四川 成都 610041)

0 引言

由于FPGA数据掉电丢失的问题,FPGA配置是系统设计中必不可少的部分[1]。随着FPGA配置文件的增大,配置时间在系统启动过程中所占的时间比例越来越不可忽视。如果FPGA设计中包含PCIE、SDIO等从设备,还必须在CPU启动扫描设备前就配置完成并进入工作态,这时FPGA配置的速度尤为关键。实际应用中,每个项目选用的FPGA型号不尽相同,配置的相关参数也不同,但是FPGA的从模式配置时序却基本一致[1]。为了保证足够的配置速率和配置模块的快速移植,针对嵌入式系统中CPU+FPGA的典型应用[2],本文提出了一种基于CPLD+FLASH的通用、快速、全国产化的FPGA配置方案。该方案兼顾灵活性和通用性,对实际项目具有极大的参考价值。

1 方案架构

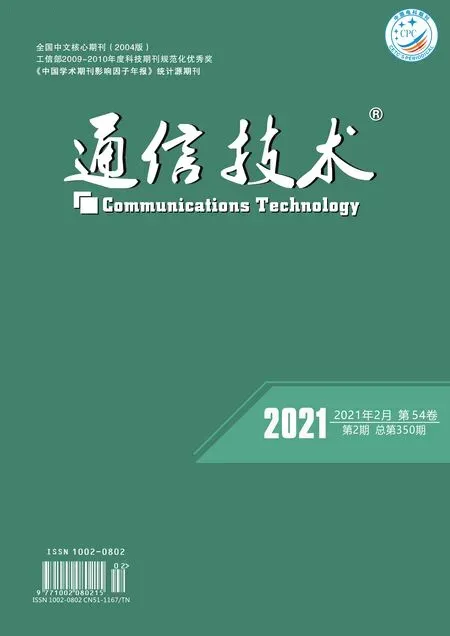

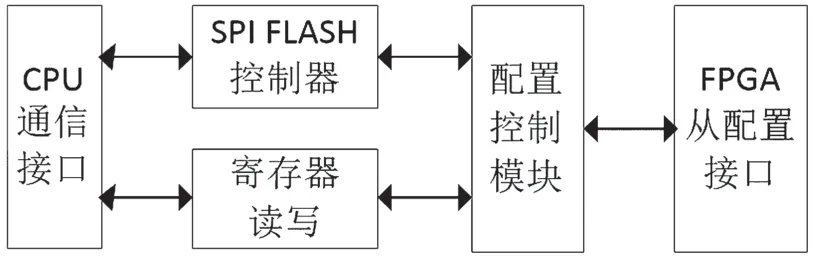

方案的系统组成如图1所示。CPU与CPLD通信一般对速率不敏感,可通过SPI、I2C、LocalBus以及GPIO等简单接口交互,几乎每个系统的CPU都满足条件。CPU不仅可以和CPLD通信,实现接口转换或数据处理等逻辑功能,还可以通过CPLD内部的SPI FLASH控制器操作外部FLASH。CPLD读取FLASH内的配置参数和数据,按照从模式配置接口的时序要求实现FPGA的配置。

图1 方案原理架构

本方案主要有3个优点:

(1)通用性强。硬件设计和CPLD逻辑设计保持不变,CPU仅仅通过改变FLASH上存储的数据格式,便可以实现不同FPGA芯片的程序配置,能够快速应用于新项目,缩短项目开发调试周期。

(2)配置速度快。CPLD整个配置期间无需CPU干预,而且可以上电后立即启动配置[3],能够最大程度地减少配置时间。

(3)灵活性高。支持CPU在线更新FPGA配置文件和配置参数,实时获取配置状态和结果,方便项目调试。

本着国产化的产品目标,兼顾成本和性能,设计中CPLD采用安路公司的ELF2L45。该器件具有4 500个LUT和700 kb的BRAM,足够实现本方案的逻辑功能。FLASH型号选择兆易创新的GD25Q系列,时钟频率高达104 MHz,不同存储大小的型号能做到设计兼容。

2 FLASH数据存储格式

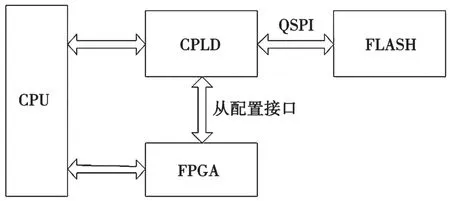

当前市面上的主流FPGA(Xilinx、intel、安路、高云等)都支持从串、从并的配置方式,且遵循如图2所示的配置时序波形。

图2 FPGA从模式配置典型时序

不同型号的FPGA配置主要有复位脉冲时间T1、等待初始化完成的时间T2、等待时钟和数据输出的时间T3、配置文件长度L、比特序bs、字节序Bs、文件加载后DONE拉高前额外需要的CCLK数量N1、DONE拉高后启动完成前额外需要的CCLK数量N2、配置接口数据位宽W等变化因素。

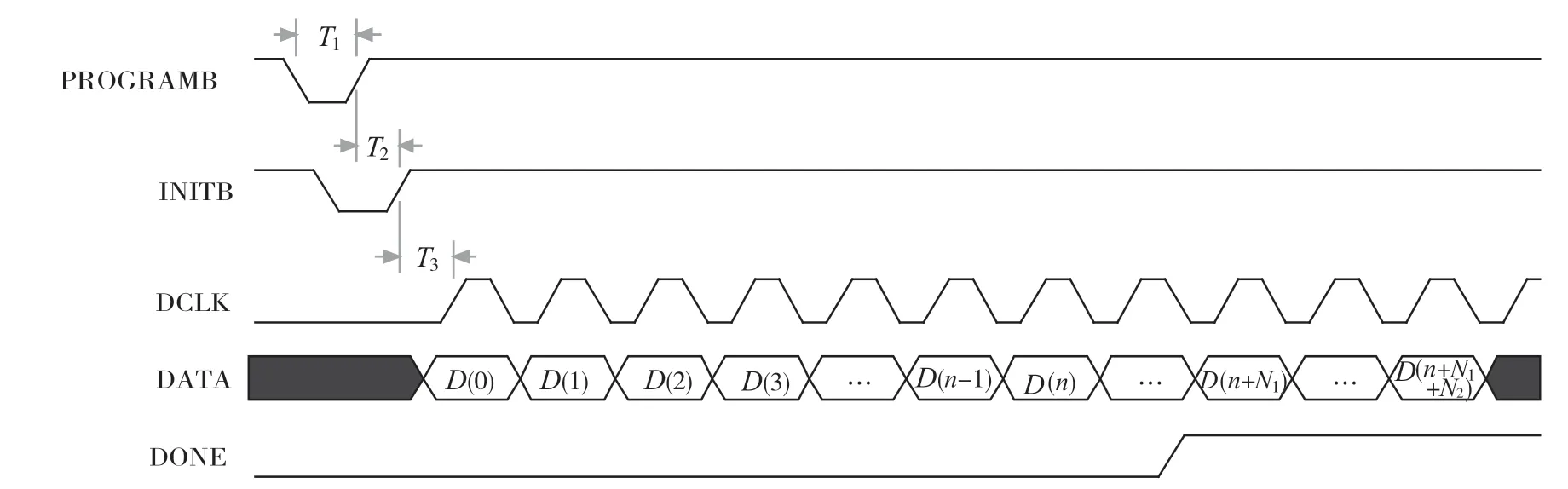

根据上述配置变量,方案中FLASH内部存储的数据格式定义如图3所示。第0个page用于存储配置过程的变量,可随着FPGA配置参数的变化灵活改变。其中,标记定义为常数,用于识别配置参数起始位置,并预留校验和字段,用于验证配置参数的正确性;文件长度包括配置文件后面的填充数据;CPLD在填充数据输出期间继续输出时钟和特定的数据,保证DONE拉高前FPGA能够正常进入启动过程;填充数据的最小长度PL可按PL=([N1/8]+1)×W计算。配置接口数据位宽W支持1 bit和8 bit两种,足够满足实际应用。

3 CPLD设计与实现

3.1 原理框图

如图4所示,CPLD主要完成与CPU的数据通信,实现SPI FLASH控制器和FPGA配置控制等功能。

图3 FLASH数据存储格式

图4 CPLD内部实现

主要有5个子模块。第一,CPU通信接口。按照自定义协议与CPU进行数据收发,并进行通道的分流和合流。第二,SPI FLASH控制器,实现CPU和CPLD对外部FLASH的各种命令操作。第三,寄存器读写,提供RAM读写操作接口。第四,配置控制模块,负责主动发起FLASH的读请求和处理读返回数据。第五,从配置接口,完成FPGA从配置时序的控制。

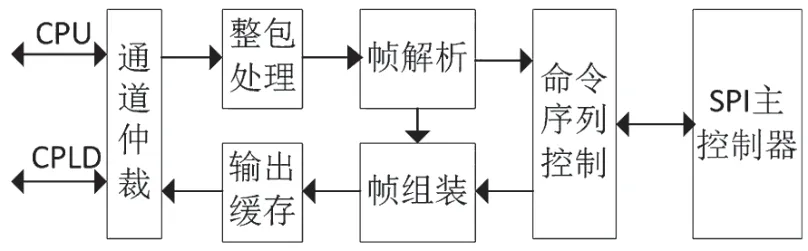

3.2 SPI FLASH控制器

SPI FLASH控制器支持两个8 bit的FIFO通道访问,按数据帧的方式仲裁和处理,实现过程如图5所示。外部CPU实现FLASH的擦除、编程以及读等操作。FLASH编程后置QE位,使能SPI接口的四线模式。CPLD实现配置期间FLASH数据的快速读取。由于FLASH接口没有流控,控制器输入需要做整包处理,保证一帧写数据能够连续发往FLASH。控制器输出缓存需预留足够的空间,保证每次的读数据完整不丢失。命令序列控制主要实现与FLASH交互的字节顺序。SPI控制器完成并串转换和SPI总线的时序控制。

图5 SPI FLASH控制器实现

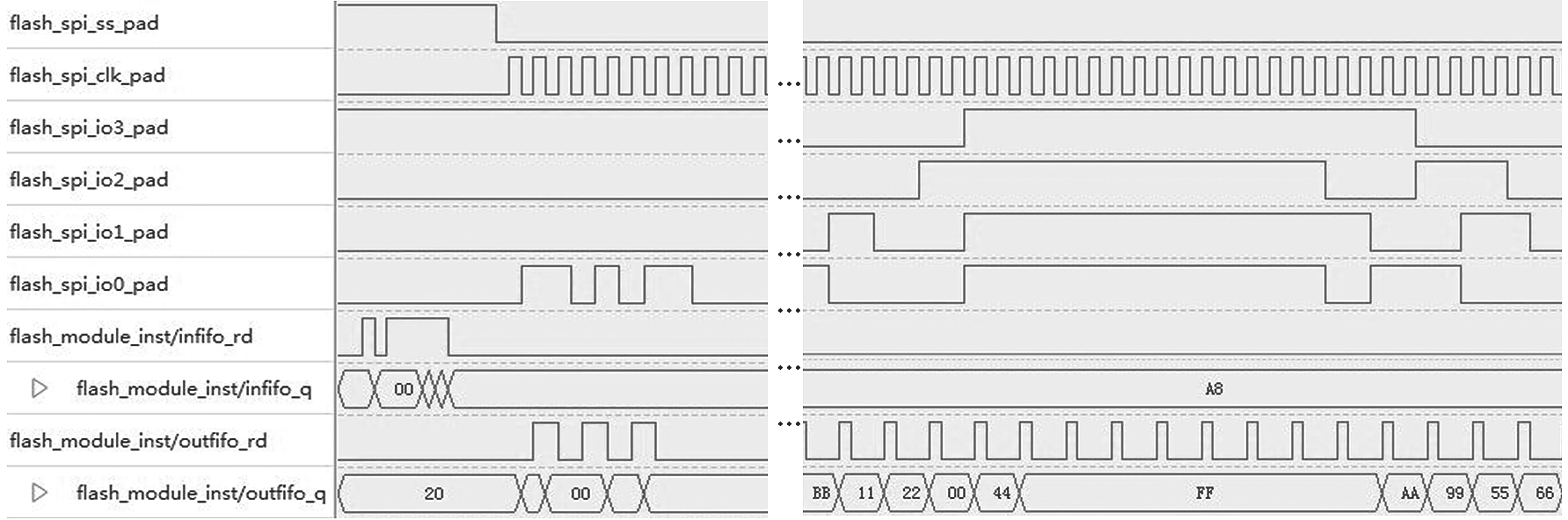

为优化CPLD资源占用,控制器仅支持读ID、写使能、读写状态寄存器、擦除(扇区擦除、块擦除、芯片擦除)、单线/四线读和页编程[4]命令。图6是用安路开发软件抓取到的FLASH四线读操作时序。波形中可以看到8 bit位宽检测码0xBB11220044、同步字0xAA995566等标志性字段,读数据是四线传输,但是命令、地址和dummy都是单线传输。考虑到该部分时间开销,一次操作读取的数据越长效率越高。此外,FLASH的SPI接口时钟频率应满足条件:

图6 逻辑分析仪捕获的FLASH四线读操作波形

3.3 内部寄存器

考虑到设计的灵活性和调试的便捷性,CPLD内部定义以下5个和配置相关的通用寄存器。

寄存器1:读FLASH起始page,默认page0。

寄存器2:配置启动信号,CPLD自清零。

寄存器3:配置结束标志和配置结果,包含错误状态。

寄存器4:配置文件长度,从FLASH中读取的参数值。

寄存器5:当前配置已输出的数据长度。

当FLASH上存储多份配置数据时,可通过寄存器1选择当前配置的版本。如果系统对FPGA上电配置时间有要求,可以修改寄存器2的默认值使能配置启动。CPLD上电后会立即开始FPGA的配置,不占用CPU的启动时间。CPU启动后还可以写寄存器2触发在线配置。CPLD开始配置后自动清零该寄存器。配置过程中,CPLD实时更新寄存器5。CPU任意时刻都可以读相应的寄存器判断配置状态和进度,实时获取配置结果,定位配置失败原因,在项目调试和问题排查中极为方便。

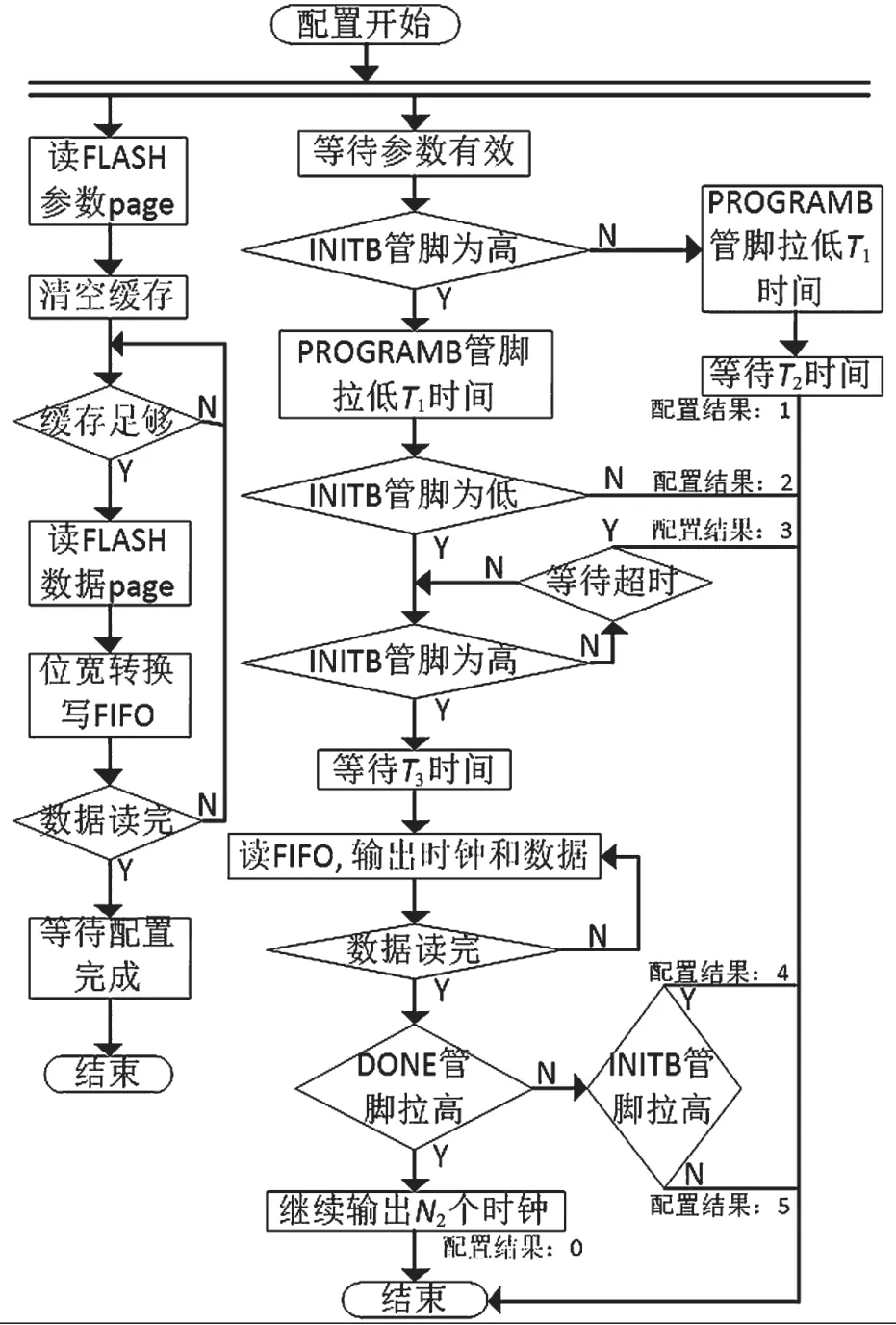

3.4 配置流程

根据上述原理,CPLD的配置逻辑按照图7的流程图设计。上电自动启动配置或者CPU命令启动配置都会触发该流程。每次配置CPLD先主动读FLASH的控制参数page,获取本次配置所需要的参数,随后只要缓存空间足够,就继续读取FLASH的配置数据,且地址依次递增直到累计读取长度达到配置参数L。读返回数据写入一个位宽8 bits、深度1 024 words的异步FIFO中。写入前需根据bs进行比特序调整,根据W进行位宽转换。从串模式下,FIFO中只有最低比特有效。异步FIFO采用showahead模式,初始化完成再等待T3时间后开始读FIFO。只要FIFO非空即读,同时将读数据输出到DATA。读时钟取反后输出到DCLK,保证时钟上升沿处于数据最佳采样窗口。FIFO空时,DCLK和数据都输出低电平。配置数据输出完成后检测到DONE拉高,再根据配置参数N2继续输出时钟,然后结束本次配置。无论配置是否成功,CPLD都会将配置结果记录在寄存器中。

图7 CPLD内部状态跳转示意

4 实测与分析

本文以FPGA型号为复旦微电子公司的JFM7K325T为例[5],配置文件约11 MB,FLASH接口的SPI时钟频率fQSPI为50 MHz,每帧读取一页,配置接口时钟频率fDCLK为25 MHz,数据位宽W为8 bit。

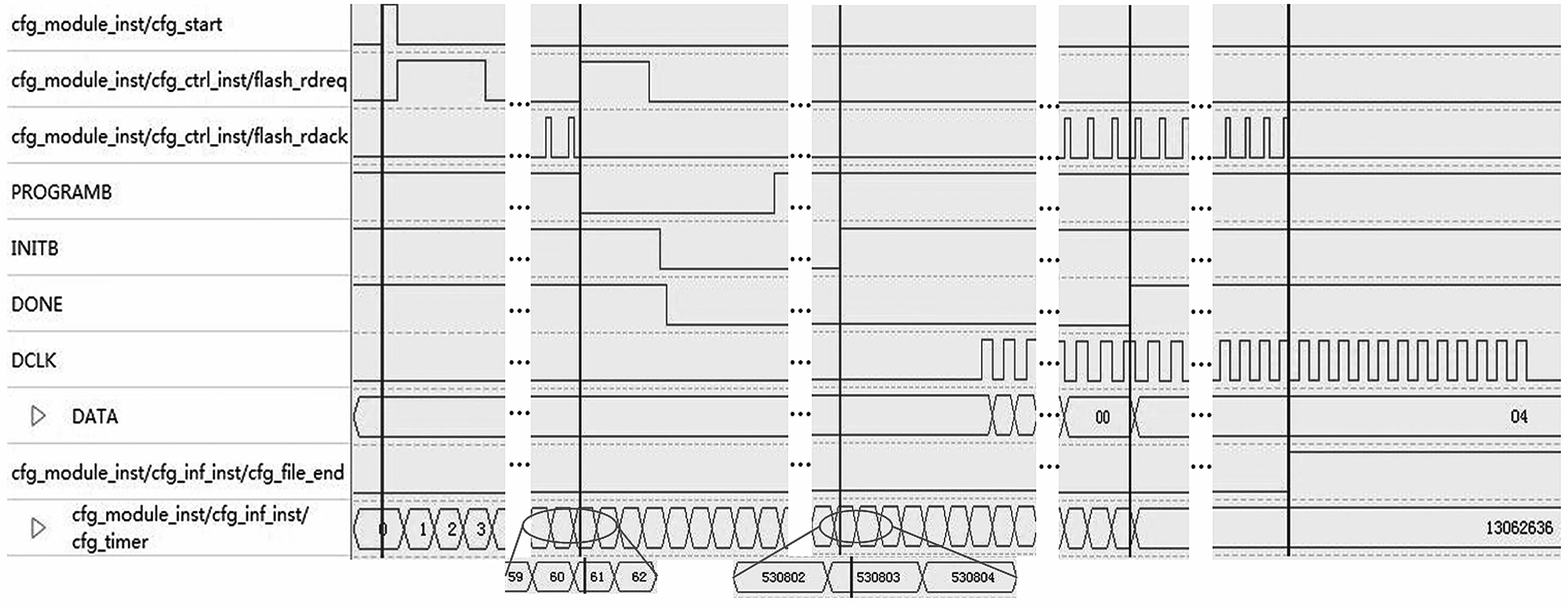

图8 逻辑分析仪捕获的CPLD配置过程波形

CPLD完成一次成功的配置需经历图8中的5个步骤。其中,cfg_timer记录配置FPGA所消耗的时间,波形中显示的是十进制;计数的时钟为25 MHz;CPLD从启动配置到DONE管脚拉高大约需要522 ms;CPU完全能在BOIS阶段扫描到FPGA实现的从设备,满足项目对配置时间的要求。如果提高SPI时钟速率、配置位宽、配置时钟频率和每帧从FLASH读取的数据长度等,配置时间还可进一步缩短。

5 结语

针对CPU+FPGA的应用架构,提出一种基于CPLD+FLASH的FPGA配置方案。该方案的硬件和逻辑设计通用性高,可以实现模块化,便于项目移植且配置速率高,满足系统启动要求。CPU还可以灵活更新配置内容,调试和升级方便。该方案具有可行性,已成功应用于多个实际项目,为工程实践提供了良好的借鉴。