图像处理算法IP核的异构验证框架

赵 陆,文建平*,莫 为,陈仕睿,李项河

(1.西安科技大学机械工程学院,陕西 西安 710054;2.陕西科技控股集团有限责任公司,陕西 西安 710000;3.西安西微智能科技有限公司,陕西 西安 710000)

1 引 言

数字图像处理从日常生活到工业生产的各个领域,都扮演着重要的角色[1]。由于图像分辨率的提升和图像处理算法的复杂化,传统的串行处理器已难以满足图像处理的实时性需求。随着芯片制作工艺的不断提高,单一芯片能够承载更多的功能,以预处理和特征提取为任务的图像处理算法或机器视觉算法经过优化后,移植为具有一定功能的电路模块(Intellectual Property core,IP核),集成在片上系统(SoC)或应用在现场可编程门阵列(FPGA)成为解决实时图像处理任务的一个新的研究方向[2-3]。

随着SoC和FPGA设计规模的不断增大,IP核的独立正确性成为了系统正常工作的基本保证。在芯片设计的整体流程中,验证占据了70%的工作量[4-5],如何对IP核进行实时、有效的验证成为硬件设计的关键。使用EDA仿真软件对设计进行动态模拟是最为广泛的功能验证方法,经过设计人员的不断完善,已发展出了成熟的验证方法学(UVM)[6-7]。虽然具有良好内部信号可见性、实时调试性和可重用性,但使用EDA软件进行仿真时,大量的验证激励会使得验证周期长达数日。为了克服软件仿真验证周期长的问题,FPGA原型验证成为最有效的解决方法之一。文献[8]使用FPGA对LSD直线检测算法IP核进行功能验证。文献[9]使用FPGA针对Canny算子IP核构建了功能原型。但由于FPGA原型验证需要围绕待验证的设计,有针对性地构建测试框架,给设计人员带来了极大的不便。为了解决该问题,研究人员尝试使用软硬件结合的方式,在保证FPGA仿真效率优势的同时,增加验证框架的复用性。文献[10]使用SoC器件的硬核处理器作为激励的发生单元和验证覆盖率分析单元,避免因修改激励而使得FPGA全局重新配置,但在图像处理算法IP核的验证任务中,测试激励是类型各异的视频流,无法通过硬核处理器产生。文献[11]提出了一种基于软硬件协同仿真的IP核验证平台,平台由PC端的Leon3 SoC模拟环境和FPGA端基于Microblade软核搭建的SoPC仿真环境组成,两者通过以太网进行链接,但受限于软核的处理速度,PC端和FPGA端的通信速率无法承担测试视频流的传输。文献[12]开发的框架提供了一个验证覆盖库,通过验证覆盖和待测IP的组合,实现FPGA的完整配置。该覆盖库减轻了为特定设计搭建验证框架的压力,但为保证验证覆盖的可重用性,覆盖只针对通用接口构建了基础结构,缺少对图像数据的兼容性。文献[13]构建了FPGA与主机的信息交换系统,提出了使用FPGA联合上位机软件进行数字电路测试和验证的思路,但文中只验证了系统收发信息的有效性,没有针对复用性对软硬件进行协同设计。本文基于FPGA原型验证技术,使用集成ARM(Advamced RISC Machine)和FPGA的异构平台联合上位机软件,针对图像处理算法IP核构建验证框架。通过软硬件的协同设计保证了验证框架对不同图像处理算法IP核的验证兼容性和实时性,并通过部分重配置技术快速更替待验证算法IP核,提高了验证框架的稳定行和敏捷性。

2 图像处理算法IP核验证方法

图像处理算法向数字电路移植的过程中,首先采用C或者python等高级语言构建图像处理算法模型,然后使用RTL代码对构建的模型进行描述和移植,C/Python模型被用作IP开发的理想参考模型[14]。在使用FPGA对图像处理算法IP核的功能进行验证时,由于图像处理算法的特殊性,存在着以下难点:

(1)激励图像的分辨率和位深度具有多样性,对FPGA硬件架构的兼容性提出了较高的要求。

(2)图像处理算法的应用场景及目标具有很大的差异性,相应的测试图像呈现多样性,无法通过SoC中的硬核处理器自发产生激励图像。

(3)图像处理算法IP核的更改会导致整个框架的重配置,降低了图像处理算法IP核的迭代速度。

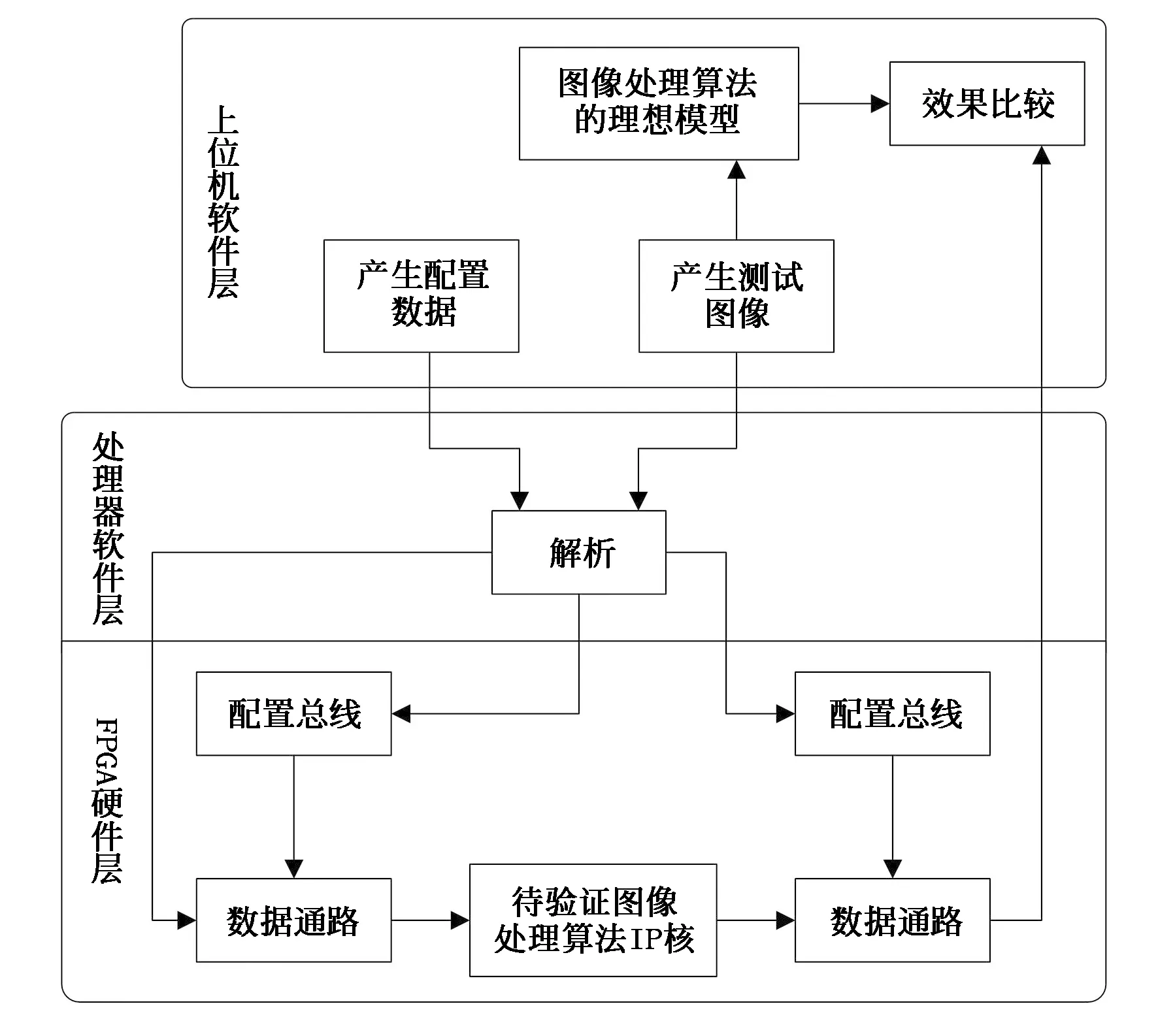

针对以上存在的难点,本文提出了如图1所示的验证方法。首先在FPGA硬件层中针对图像处理算法IP核的输入和输出预先搭建了兼容多类型图像数据的传输通路,再由上位机MATLAB软件发送,处理器软件层解析的配置数据经由配置总线实现数据通路的动态配置,进而保证了验证框架的泛用性;上位机MATLAB软件根据待验证算法IP核的需求产生测试视频流,一方面发送给由高级语言构建的图像处理算法理想模型,另一方面由处理器软件层解析后,经由配置后的数据通路发送到待验证的算法IP核中,通过比较二者的测试响应实现IP核的功能验证;待验证算法IP核作为部分重配置模块,在形成完整构型时避免了配置总线与数据通路的重配置,在保证框架稳定性的同时,加快了待验证IP核的部署速度。

图1 图像处理算法IP核验证思想Fig.1 Verification idea of IP core for image processing algorithm

3 验证框架设计

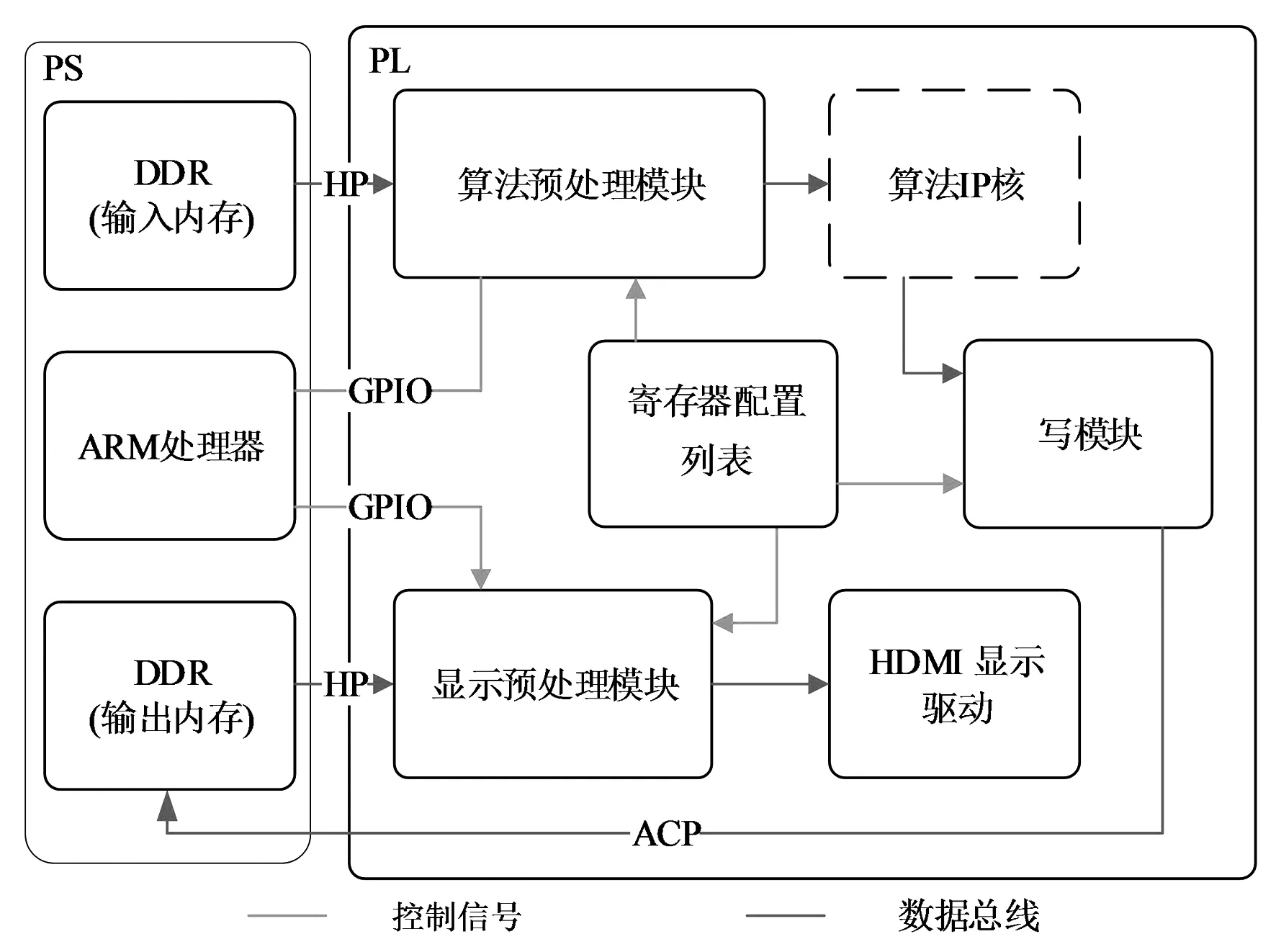

验证框架由集成处理器系统(Processing System,PS)和可编程逻辑(Programmable Logic,PL)的SoC联合上位机软件构成。PS包括ARM处理器、内存控制器、千兆以太网控制器、USB控制器等。PL拥有标准FPGA的结构,二者通过从低速到高速的一系列接口进行通信。如图2所示,上位机使用MATLAB软件产生测试图及相应配置数据。PS端与上位机建立以太网通信,并进行数据的解析和调度。PL端对接收的图像数据进行处理、计算和显示。该框架能够兼容以8,16,24 bit位深度图像为对象的算法IP核的验证工作,并具有良好的扩展性。

图2 系统架构Fig.2 System framework

3.1 PS端软件开发

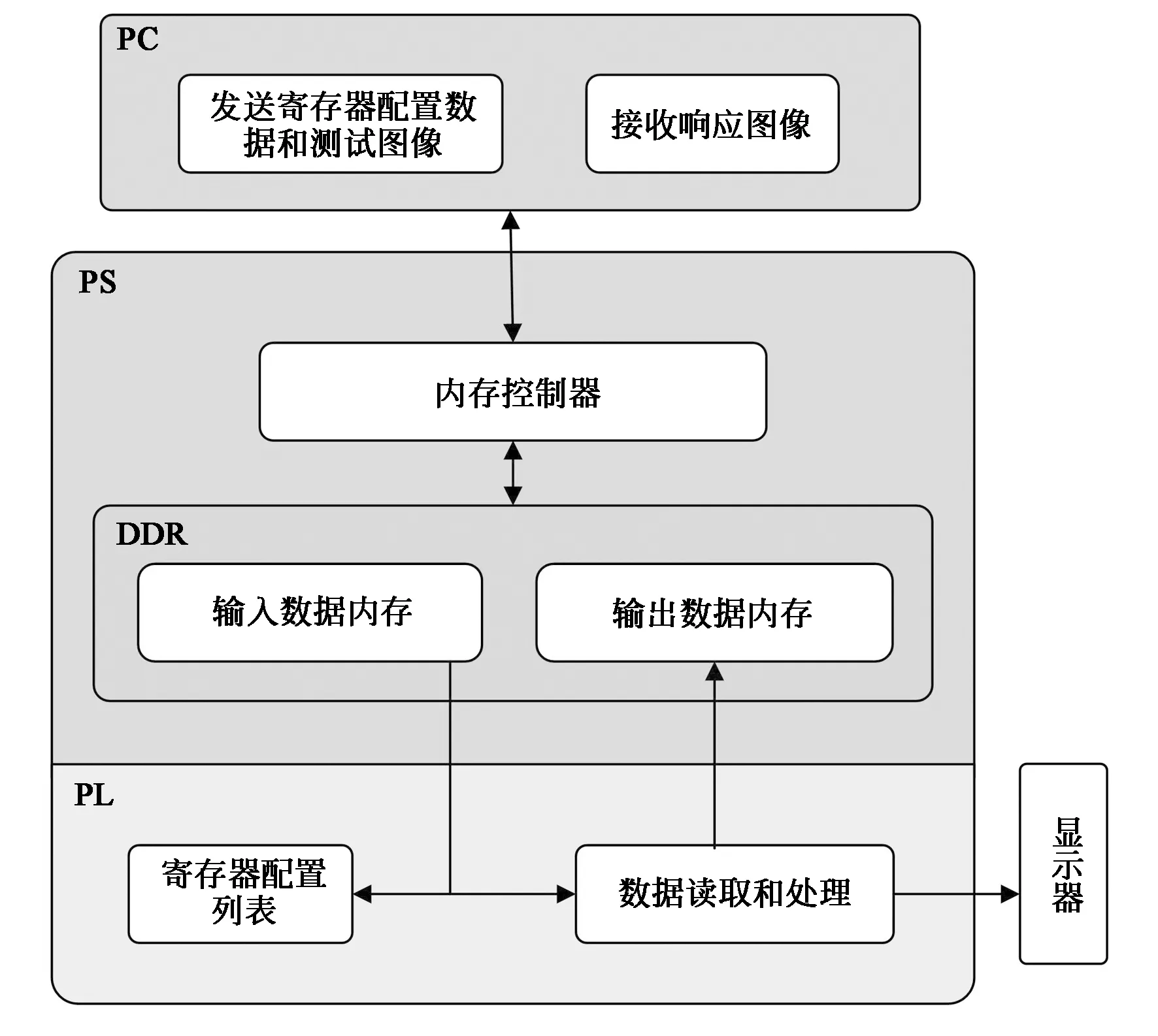

由自身特性决定,FPGA对并行数据具有很好的处理实时性,而不善于处理串行指令,虽然可以通过在FPGA内部搭建软核的方法实现软件编程,但软核会占据较多的逻辑资源并且处理性能有限。ARM硬核处理器则很好地弥补了FPGA在事务管理方面的不足。本设计采用PS完成与上位机的通信、数据的交互、任务的调度等,其整体架构如图3所示。

图3 PS端软件处理流程图Fig.3 PS software processes flowcharts

由于视频流的传输需要较大的带宽,在上位机和验证框架之间建立TCP/IP协议栈,实现千兆以太网通信,保证验证框架对视频流处理的实时性。为降低协议对RAM资源的占用并增强验证框架的泛用性,采用Light Wight IP协议中的Socket API进行网络开发,上位机使用MATLAB软件与验证框架进行连接。在图像传输之前,需要对处理框架进行配置以兼容各种类型和大小的图像数据,如图3所示。

配置数据包由上位机发送给PS端,PS端进行解析后,通过GP口配置PL端寄存器,实现硬件架构对于不同类型和分辨率图像的兼容处理。在该框架中,PL端拥有256个可配置寄存器,对应地址范围0~255,其中地址0~5对应的寄存器为基础寄存器,该部分寄存器必须在发送测试图像之前进行配置;地址6~255是预留地址段,可进行拓展配置。基础寄存器的配置数据如表1所示。

表1 寄存器配置数据Tab.1 Register configuration data

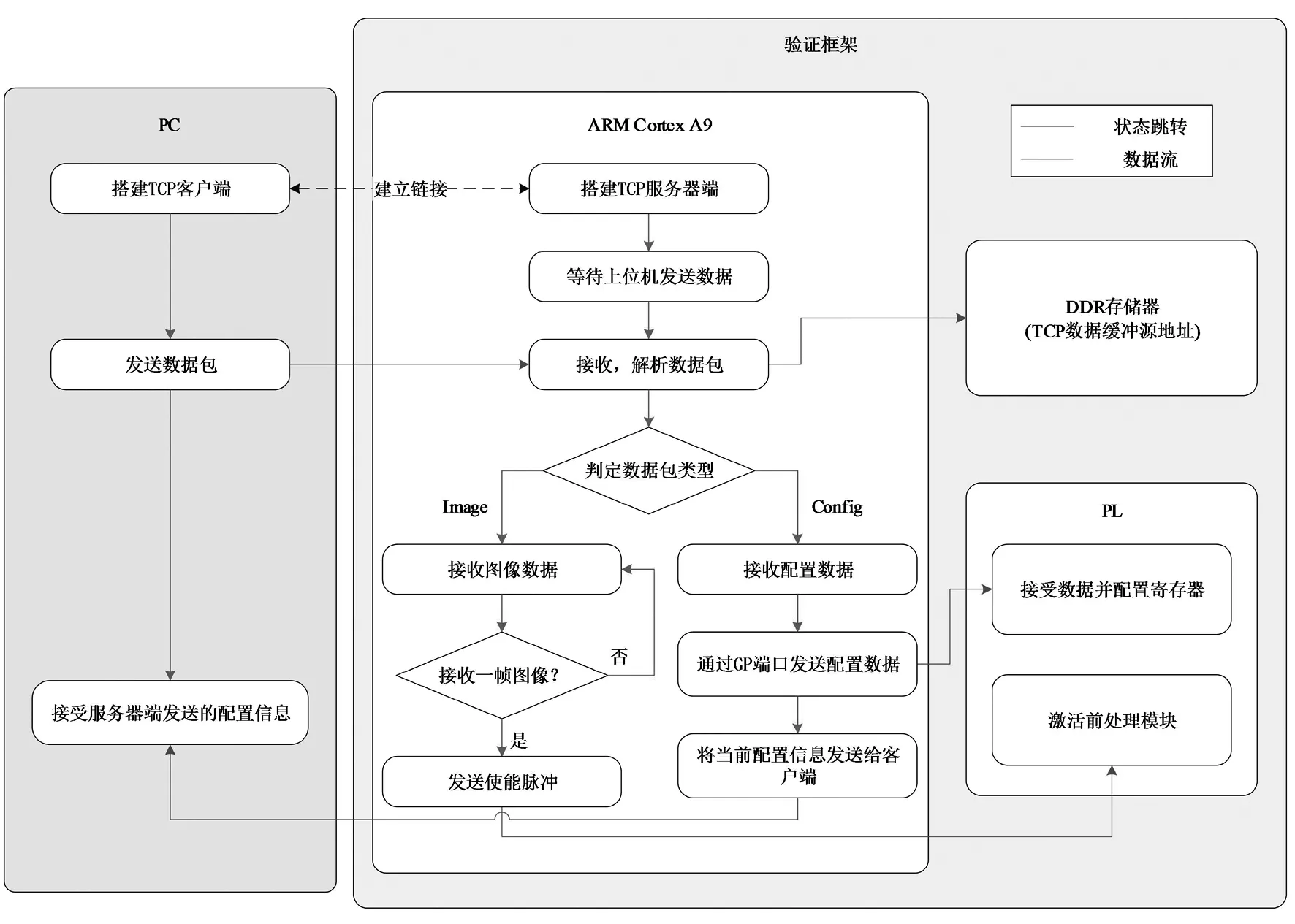

3.2 PL端逻辑设计

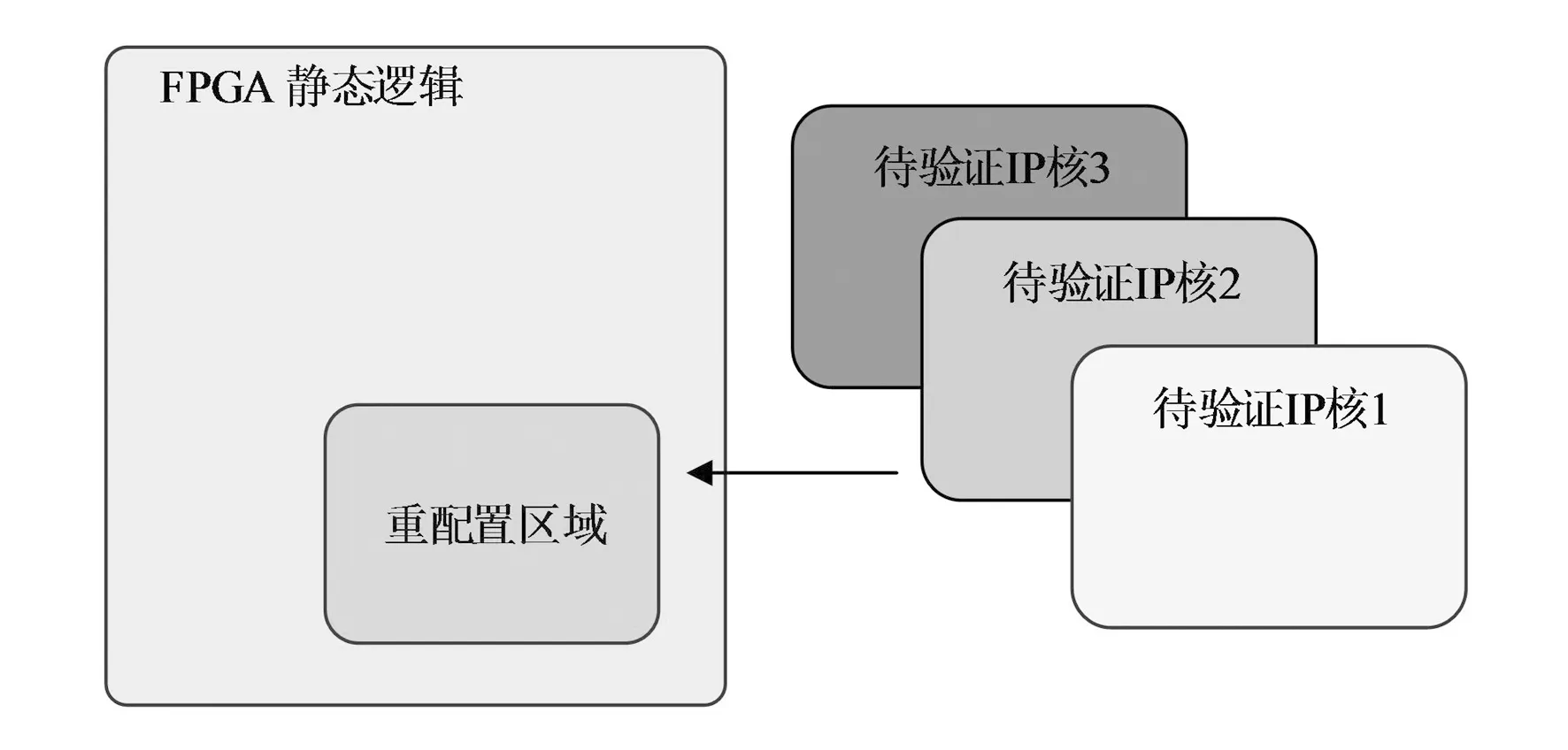

由于算法IP核验证任务的特殊性,在实际应用中需要分时对待验证的IP核进行替换,为加快图像处理算法IP核部署速度,提高FPGA中硬件逻辑的稳定性,使用部分重配置技术将PL的逻辑资源分为静态区域和部分重配置区域。如图4所示,待验证IP核作为部分重配置模块,能够在锁定FPGA静态逻辑的同时实现更替,既避免了待验证IP核的部署对静态逻辑时序的影响,又加快了算法IP核在FPGA上的部署速度[15]。

图4 部分重配置Fig.4 Partial reconfiguration

静态逻辑的任务是为图像处理算法IP核搭建具有高度泛用性的数据输入和输出通道,并将处理结果发送给显示器。如图5所示,静态逻辑由预处理模块、寄存器配置列表、写模块和HDMI驱动模块组成。当PS端收到图像数据包并完成解析后,通过通用输入输出接口(General-purpose input/output,GPIO)发送脉冲激活算法预处理模块与显示预处理模块,然后,算法预处理模块通过高性能接口(High Performance,HP)将内存中输入地址的图像数据读出进行格式化,并输出给算法IP核计算,计算后的结果发送到写模块中,利用加速器一致性接口(Accelerator Coherency Port,ACP)将处理结果写入内存的输出地址中。输出地址中的数据通过显示预处理模块和高清多媒体接口(HDMI)显示驱动模块输出给显示器。

图5 PL整体架构Fig.5 Overall structure of PL

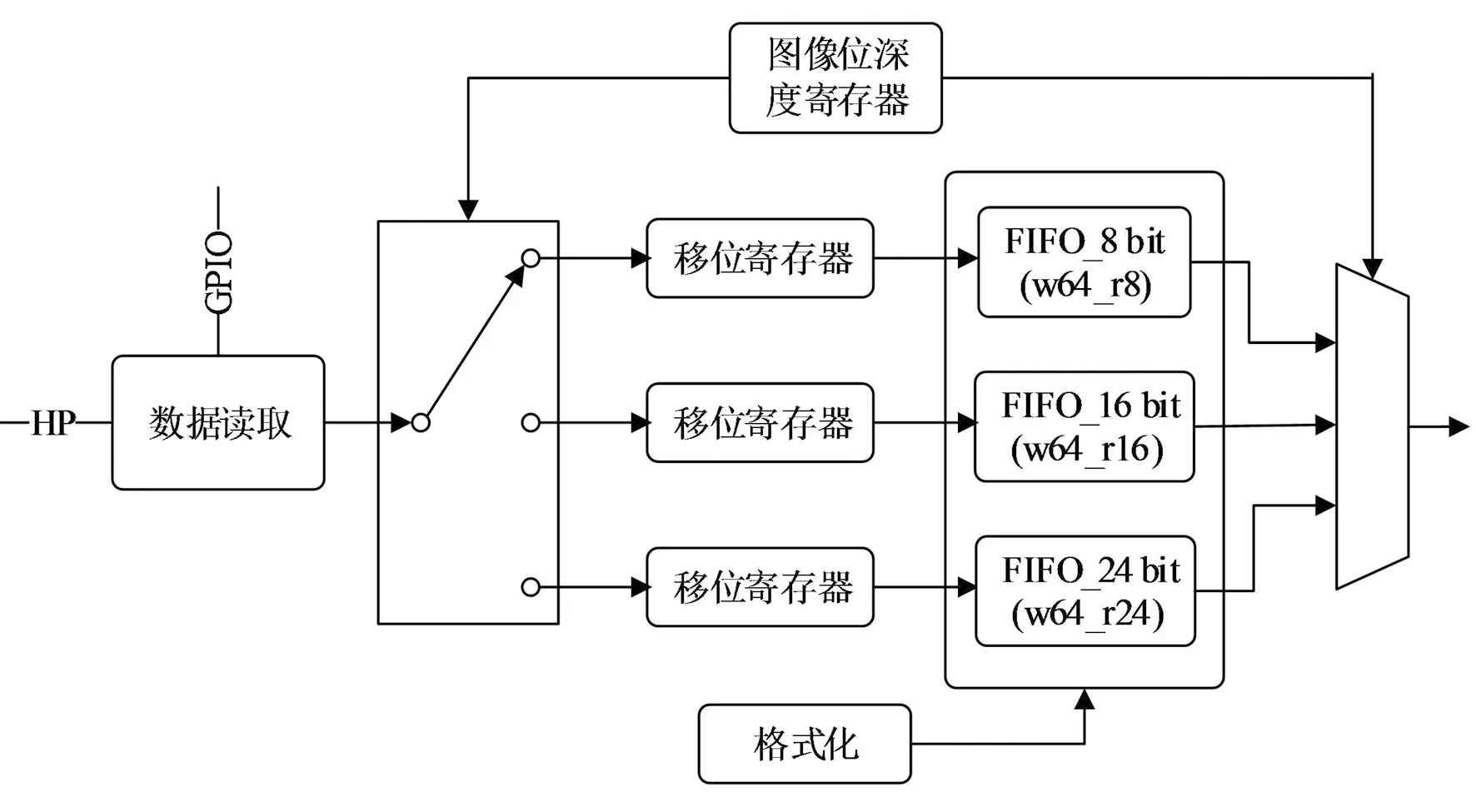

预处理模块负责将内存中的数据读出,并赋予一定特征,使其能够符合后续模块对输入数据的要求。分别布置在待验证算法IP核和HDMI显示驱动模块之前。预处理模块分为两部分:数据读取和格式化。如图6所示,PS通过GPIO向该模块发送启动脉冲后,内存中的数据通过HP口读出到预处理模块中。为保证一次突发传递的像素数量为整数,应将兼容图像位深度的公倍数设为突发数据位宽。读出的数据通过异步FIFO进行缓存和位宽转换,由于不同位深度的图像数据对位宽转换的要求各有不同,基于逻辑资源换取兼容性的思想,使用多个FIFO对数据进行缓存和位宽转换,再通过用户配置的图像位深度寄存器对电路进行选通。

图6 预处理模块Fig.6 Preprocessing module

在传输过程中,图像数据仅保留亮度或颜色数据,行场同步信息丢失。由于算法模块和显示驱动模块对时序的要求不同,所以两个预处理模块在格式化上的需求有所不同。

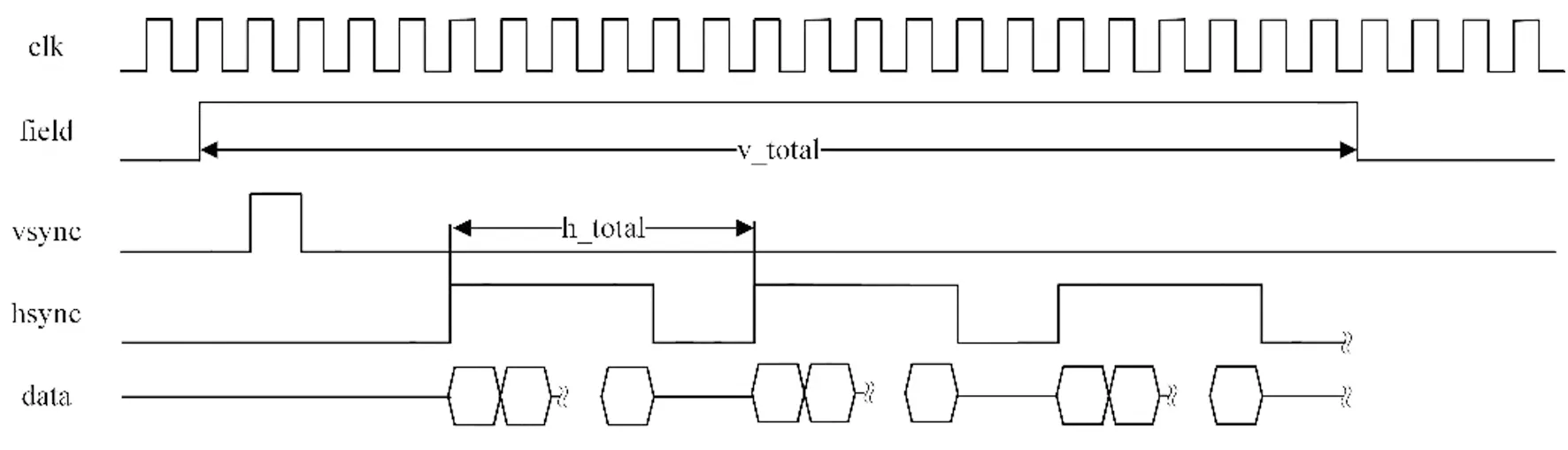

(a)算法模块对图像数据的时序参数没有严格要求,只需按照一定的规律对连续数据进行分割。时序参数如图7所示,以实际的图像大小为基础,将连续数据分割为图像数据。

图7 格式化的时序参数Fig.7 Timing parameters of formatting

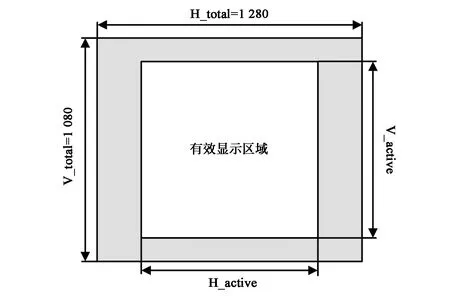

(b)由于显示驱动模块对图像的时序参数要求严格,而不同分辨率具有不同的同步信号参数,为显示分辨率各异的图像,将显示区域划分为有效显示区和无效显示区。如图8所示,有效区域位于显示区域的中央,无效区域像素点的值置为0,为显示区域中除有效区域的部分。在本实验中,采用1 280×1 080向下兼容的显示方案。

图8 显示区域划分Fig.8 Display area division

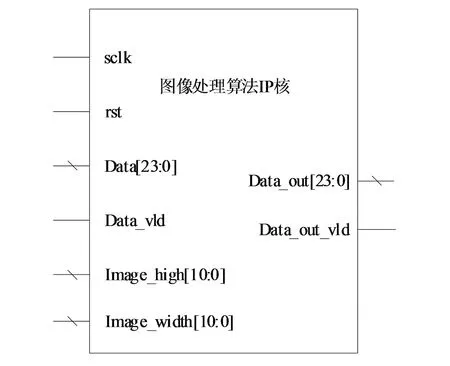

为保证对8,16,24 bit位深度图像的兼容处理,规定部分重配置模块接口一致,对算法IP核接口的设定如图9所示。数据总线设定为24 bit,图像高度和宽度设定为11 bit。在部分重配置中手工布局是不可或缺的[16],布局约束(Pblock)的设置直接影响着部分重配置模块能否成功地部署在重配置分区中。在验证框架中,由于不同算法IP核所需的逻辑资源有所区别,所以Pblock需要使用者根据需要进行约束。

图9 部分重配置模块Fig.9 Partial reconfiguration

4 案例分析

基于Xilinx Zynq-7000系列SoC,在Vivado18.2开发套件下,对本文提出的验证框架进行实验验证。为证明所述验证框架的有效性和兼容性,测试验证周期和待验证IP核的部署速度,本文以3种图像处理算法IP核为例,采用多类型、多分辨率的视频流作为测试激励,由上位机通过以太网发送给测试框架。

4.1 案例算法简述

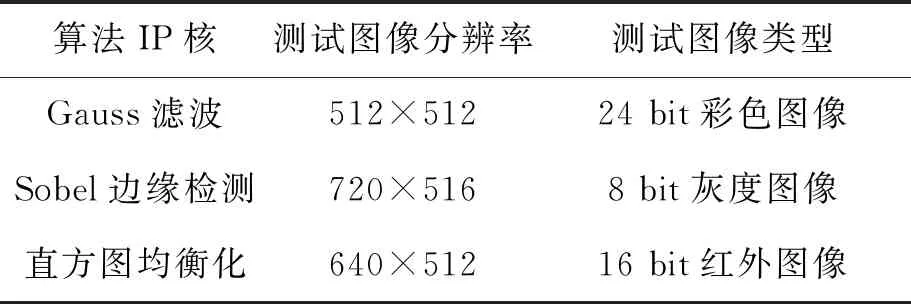

待验证的算法IP核及相应的测试视频如表2所示。

表2 测试图像分辨率及类型Tab.2 Type and resolution of test image

RGB图像的GAUSS滤波:高斯滤波是一种线性平滑滤波,作为低通滤波器使用时,可以将低频能量滤去,起到图像平滑作用[17]。本案例中对彩色图像的RGB通道分别进行高斯平滑操作。

灰度图像的Sobel边缘检测:Sobel是最常用的边缘检测算子,通过计算图像灰度函数的一阶梯度近似值实现图像边缘的增强[18]。

基于直方图均衡化的红外图像可视化:由于红外信号的动态范围较宽,需要高比特的模数转换器去采集。但是大部分模拟和数字视频接口都要求输入数据为8 bit,所以高动态范围的红外图像需要经过压缩才能够正常显示。直方图均衡化(HE)将红外图像的直方图均匀映射至256级,提升了显示图像的对比度。

4.2 验证框架验证效率

验证框架的实时验证效率由图像处理算法IP核的带宽、存储器与FPGA之间的读写速率和上位机与验证框架的通信速率决定。验证框架中各模块的传输带宽(Bandwidth,BW)如式(1)所示,其中C为模块的工作时钟频率,W为传输的数据位宽。相较于16 bit和24 bit图像,8 bit图像的算法IP核具有最低的带宽,该框架中工作时钟为100 MHz,则最低传输速率为800 Mbit/s。存储器与FPGA之间使用HP口实现数据交互,读写的工作时钟为250 MHz,数据位宽为48 bit,通信带宽为12 Gbit/s。

KBW=C×W,

(1)

上位机中的MATLAB软件与验证框架建立千兆以太网通信,其平均传输速度为502 Mbit/s。

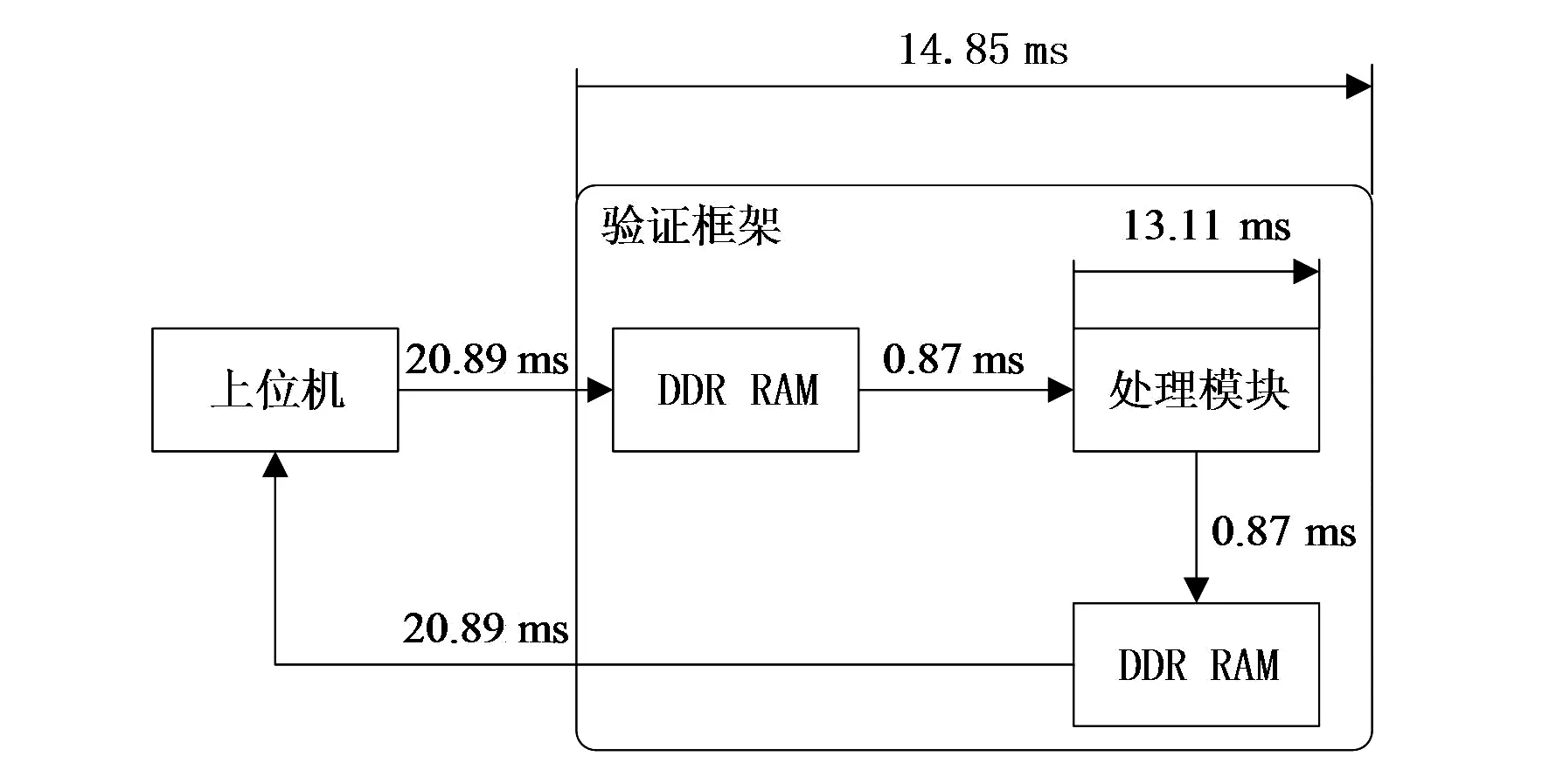

以分辨率为720 P(宽1 280 bit,高720 bit)位宽为8 bit的测试图像为例,分析数据环路的处理时效性。图10为测试图像处理过程的时间消耗,由式(1)得验证框架的处理延迟为14.85 ms,上位机与验证框架的通信延迟为20.89 ms,综合上述分析,验证效率的瓶颈在于上位机与验证框架的以太网通信速率。

图10 证框架处理时效Fig.10 Processing time of verification framework

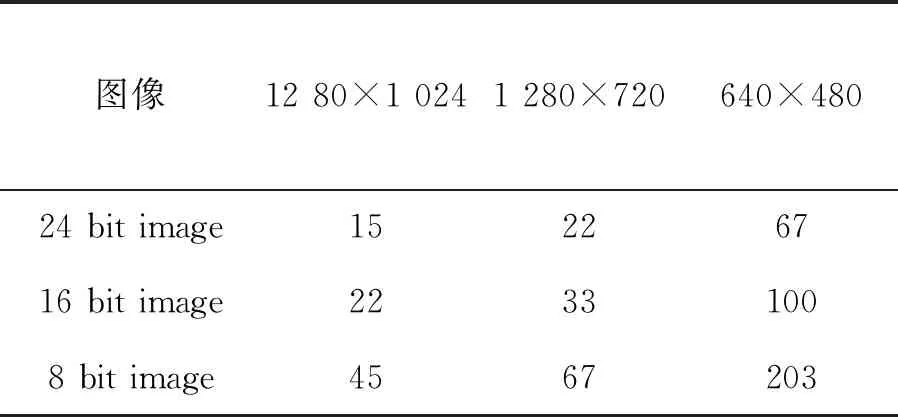

根据以太网的通信速率计算出不同位深度和分辨率图像下的验证效率如表3所示,能够达到图像处理算法IP核在实际应用场景中的使用帧率。

表3 不同测试图像的验证速率Tab.3 Image verification rate of different test images (FPS)

4.3 部分重配置应用与分析

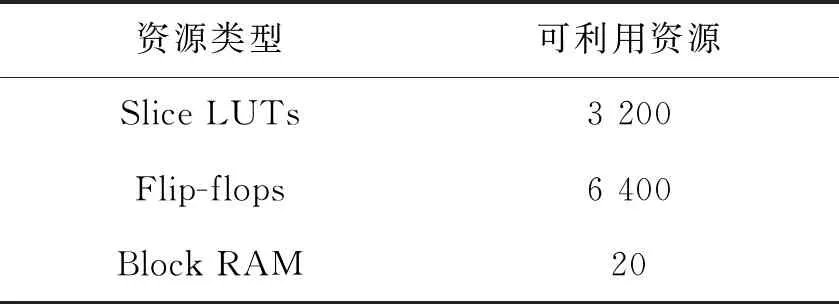

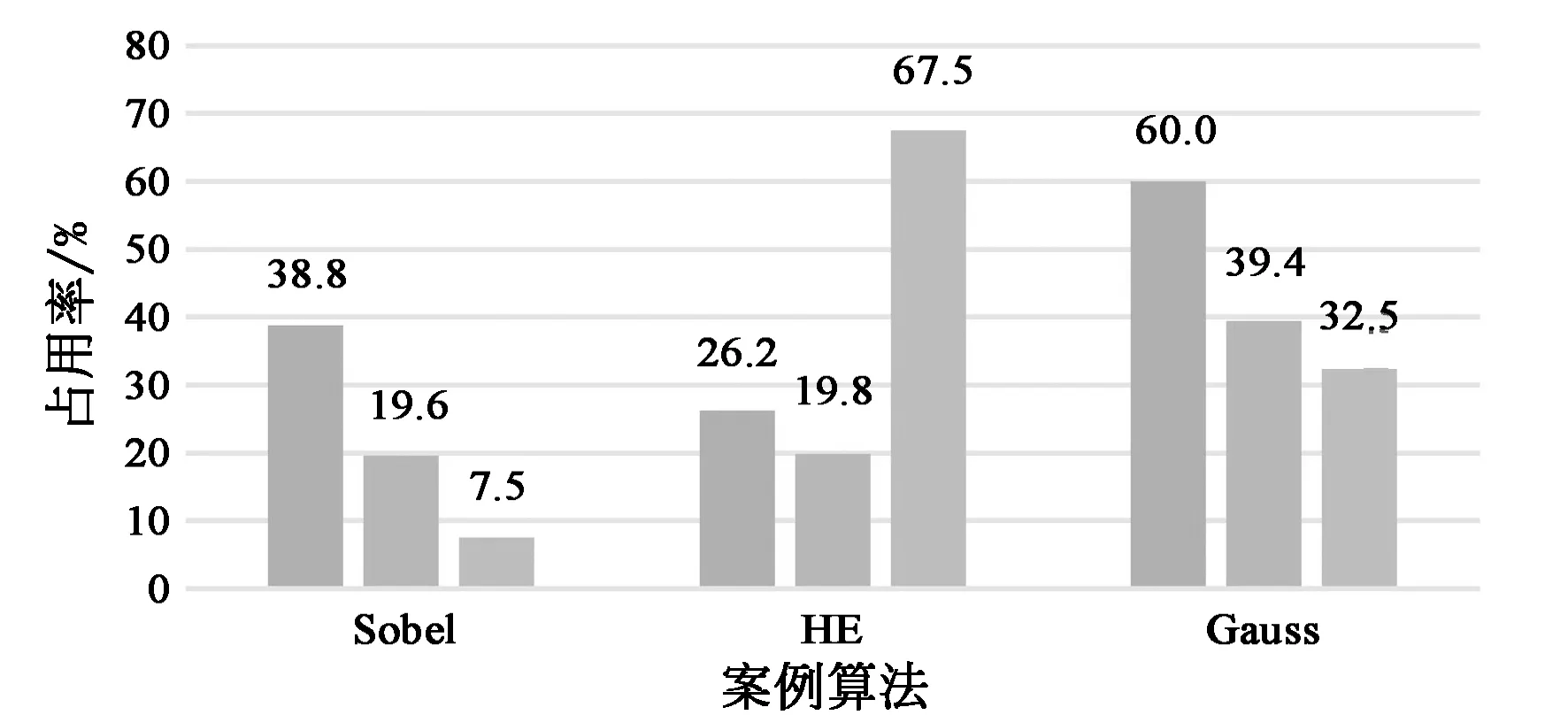

为避免重复划分可重构区域,Pblock中的资源应满足3种算法的逻辑需求[19]。根据待验证算法IP核综合后的逻辑资源需求,在FPGA中对重配置区域进行划分,本案例中Pblock中的物理资源如表4所示。待验证IP核在Pblock中的逻辑占比见图11(a),Pblock的划分以Gauss滤波中所需的Block Ram资源以及HE所需的Slice LUTs和Flip-flops资源为标准,并且为了方便静态区域和重配置区域之间的布线,Pblock预留了一定的逻辑资源。

表4 Pblock中的逻辑资源Tab.4 Logical resource in Pblock

部分重配置模块占用的逻辑资源在整体构型中的百分比如图11(b)所示,其中,静态逻辑使用了整体构型90%左右的LUTs、Register和绝大多数的Block RAM。

(a)IP核在Pblock中的资源占比(a)Resource ratio of IP core in Pblock

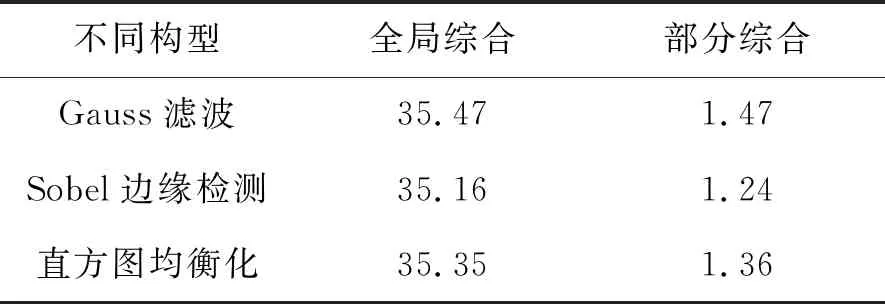

由于静态逻辑占据了整体构型逻辑量的90%左右,所以避免静态区域的重配置一方面降低算法IP核在验证框架上的部署周期,另一方面保证了静态逻辑的功能稳定性。该实验中,综合工程使用的CPU类型为4核I5-4210H,对不同算法IP核构型采用全局综合消耗的时间与部分综合所消耗的时间如表5所示,综合速度提升了25倍左右。

表5 不同构型的综合时间Tab.5 Synthesis time of different configurations min

4.4 测试结果与讨论

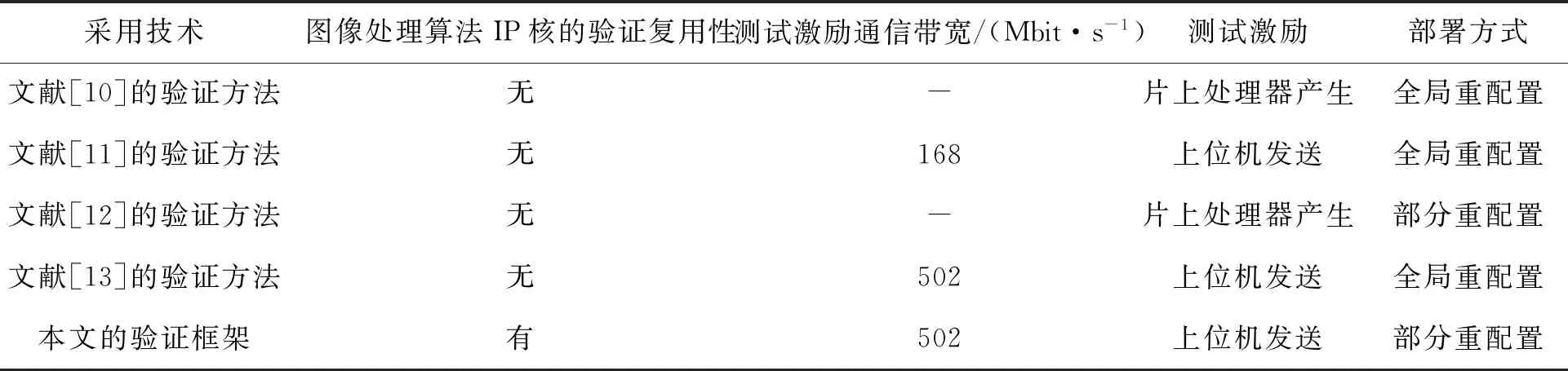

在本实验中,将3种不同的算法IP核部署在验证平台中,上位机针对待验证算法IP核发送位深度和分辨率各异的测试视频,证明了本文所设计的框架具有兼容3种位深度图像的数据通路,进而对框架的可重用性进行了验证。测试激励通过上位机发送,更符合图像处理算法IP核的实际使用要求。对实时验证效率和算法IP核的部署时长进行了分析,验证框架的验证效率达到图像处理算法IP核的使用帧率,部分重配置技术在提高框架稳定性的同时,缩短了算法IP核的部署时长,着重降低了不同构型综合的时间周期。表6为本文提出的方法与相关工作的对比。本文所设计的框架针对性地为图像处理算法IP核构建了可动态配置的数据通路,具有验证可重用性。文献[12]针对通用数据接口(AXI,FIFO)设计的验证覆盖库无法兼容类型各异的图像数据,文献[10]需要设计人员针对待验证的硬件设计开发协议桥,文献[11]与[13]只针对特定任务在FPGA中为待测设计构建了测试架构。上述方法面向图像处理算法IP核不具有可重用性。文献[10]和文献[12]使用硬核处理器产生测试激励的方法虽具有较高的传输带宽,但针对不同算法IP核构建测试视频流会增加处理器系统的软件开发难度,降低图像处理算法IP核的验证效率。本文与文献[11]、[13]采用上位机软件发生测试激励,具有较好的操作性和灵活性,其中文献[11]受限于软核的处理速度,通信速率较低。本文与文献[12]采用部分重配置的方法提高了框架的稳定性,避免了因时序问题引起的验证错误,加速了待验证算法IP核的部署速度。

表6 本文提出的方法与其他文献的结果对比Tab.6 Performance comparison of different methods

5 结 论

针对图像处理算法IP核验证效率和复用性难以统一的问题,本研究基于FPGA原型验证技术,使用ARM+FPGA异构平台,联合上位机软件以实时性与可重用性为目标构建了图像处理算法IP核验证框架。验证框架对于以8,16,24 bit位深度图像为处理对象和结果的算法IP核具有可重用性;上位机通过千兆以太网发送测试视频,更符合算法IP核的实际应用场景;部分重配置使待验证IP核的部署速度相对全局重配置提高了25倍。本文提出的方法为图像处理算法IP核的验证提供了一种统一架构。