基于FPGA 的频谱分析仪设计

张亚周,张家运,孙艳丽

(1.海军航空大学 航空基础学院,山东 烟台 264001;2.海军航空大学 学员4 队,山东 烟台 264001)

频谱分析仪是测量高频信号常用的仪表,主要测试失真、交调、寄生、噪声边带等参数[1-3]。当前实现方式主要有3 种:1)采用通用数字信号处理芯片实现;2)采用专用TFT 芯片和数字信号处理芯片相结合;3)采用FPGA 实现[3-4]。采用数字信号处理芯片,通常对速度要求较高,或受数字滤波器影响无法实现高频率和高速率[5-6]。而FPGA 具有逻辑时序控制以及强大运算能力,能够解决上述问题[7-8]。文中设计的模拟式频谱分析仪以FPGA 为核心,主要包括振荡器、混频、滤波以及显示部分。其中本振源模块主要采用MHC830 芯片设计锁相环的信号发生器;混频模块利用AD835 乘法器将输入信号与本振信号进行混频得到中频信号;混频后的中频信号经过信号处理模块以中心频率为10 MHz 进行滤波;频谱图显示模块对输出信号进行编码以及在显示器上显示。这种方法的优点是扫频范围大,硬件成本低廉,主要用于测量稳态信号的频率幅度。

1 锁相环本振源工作原理

锁相环电路主要包括晶振、鉴相器、分频器、压控振荡器、低通滤波器,并留有数据控制接口[9-10]。晶振产生由自身决定的固定频率(Fref)信号,经分频器进行R分频后输入到鉴相器,在鉴相器中将该信号与压控振荡器输出频率(Fout)信号进行N分频后的信号进行比较,将比较的相位差以模拟信号方式输出,并通过LFP 滤波加到压控振荡器的调制端,从而控制鉴相器两输入频率相等。电路的计算公式:

输出信号频率与N和R密切相关,因此设置合适的参数即可将锁相环电路作为本振源。

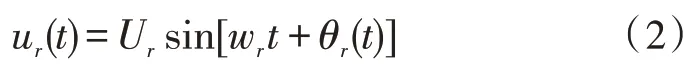

设输入信号为:

式(2)中,Ur、wr分别为输入信号的幅值和频率,θr(t)是以载波相位为基准的瞬时相位,如果载波信号是未调载波,则θr(t)=θr,为常数。

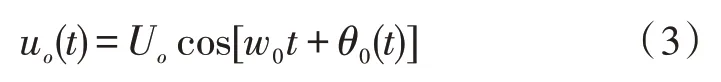

设输出信号为:

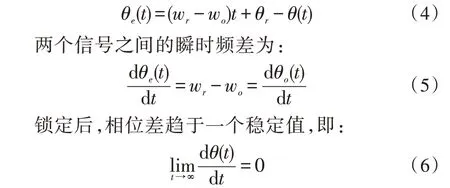

式中,uo、w0分别为输出信号的幅值和压控振荡器输出频率,θ0(t)是输出信号的瞬时相位,其初始值是常数,在VCO 受到控制时就与时间相关。两个信号的瞬时差为:

此时,输出信号的频率已经偏移原来的自由振荡频率w0,偏移量表示为:

其输出信号的工作频率为:

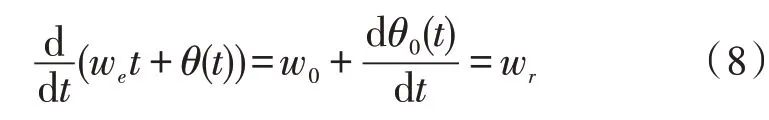

由式(8)可见,基于锁相环的跟踪特性,输出信号频率等于输入信号频率,从而达到同步且相位差恒定。

2 超外差频谱仪工作原理

超外差就是将由本地振荡器产生的信号与输入混频,从而将输入信号的频率设置为某设定的频率(由差频的作用产生),然后再进行放大和检波。

2.1 混频器工作原理

混频就是制造—个振荡电波(即本振源),使该信号与外来已调波同时送到非线性器件进行混合,由于晶体管的非线性特性,使得输出产生一个新的频率信号[11]。外差作用产生出来的差频,习惯上采用易于控制的一种频率,它比高频较低,但比音频高,这就是常说的中间频率,简称中频。混频器产生的中频信号等于两输入信号频率之和、差或其他组合的变化频率,通常由非线性元件和选频回路构成[12-13]。将混频器输出的中频信号通过中频放大器放大后,进行峰值检波。混频的作用就是将已调波的频谱不失真地由高频搬移到中频的位置上。该设计中综合考虑到功耗、失真、误差、电路的增益、设计及调试等因素,选取TI 公司生产的模拟乘法器(AD835)混频。

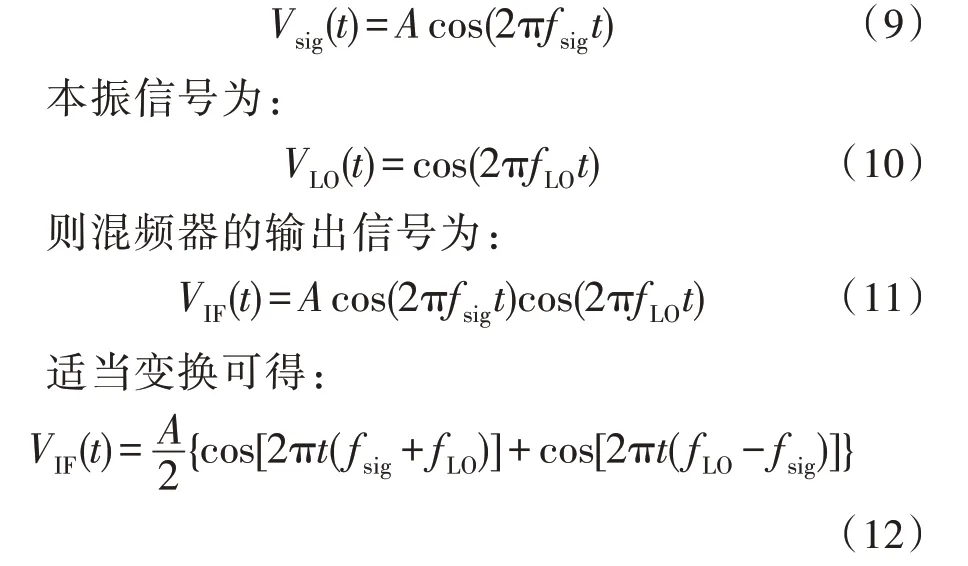

在理想情况下,假定输入信号为:

式中,fsig为输入信号频率,fLO为本振信号频率。可知混频器输出频率是本振信号和输入信号频率之和与之差,实现频谱搬移。

2.2 包络检波器原理

包络检波器是一种基于滤波检波的振动信号处理方法[14-16],它可以对输入信号进行处理,把中频信号转换成视频信号,以便显示并测量输出信号。包络检波通常是先采用二极管进行单向过滤,然后再进行低通滤波,如果不采用二极管而直接进行低通滤波,则会抵消正、负包络线,从而无法检出低频信号。ADL5513 是一款解调包络(对数)检波器,响应时间短、稳定性好、功耗小、测量精确度高、误差小,故本次设计选取ADL5513 作为检波器。

3 电路的设计

3.1 硬件系统框图

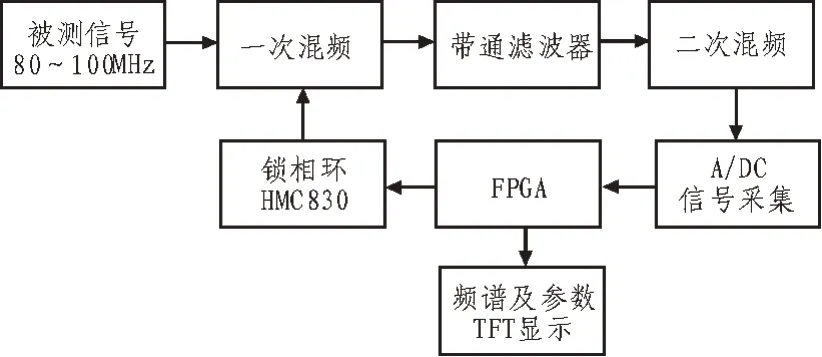

为了实现在80~110 MHz 频率范围,时间1~5 s之间的不同扫频速度和步进100 kHz 的频谱分辨率,系统采用了一次下混频、滤波结构和模拟滤波法,选取HMC830 作为锁相环芯片充当本振源,选用了AD835 模拟乘法器混频和ADL5513 对数检波器检波,并选取了AD 采样电路。系统框图如图1 所示。

图1 硬件系统框图

3.2 锁相环本振源及相位锁定电路设计

HMC830LP6GE 具有精度高、宽带宽的优点,文中设计使用该锁相环芯片充当本振源,它集成了小数分频的VCO、PFD、分频器,芯片内部集成可控信号输出功能,满足输出电压10~100 mV 的要求,同时该芯片提供了相位锁定指示,通过FPGA 及相关信号处理即可。

3.3 一次/二次混频器设计

AD835是一款性能优异的模拟乘法器,带宽可以达到250 MHz,满足该设计最大110 MHz 输入信号的要求。若是一次混频后,差频为10.7 MHz,对后端电路处理带来难度,因此采用10.235 MHz 的频率源对信号进行下变频处理,将信号频率变到465 kHz。

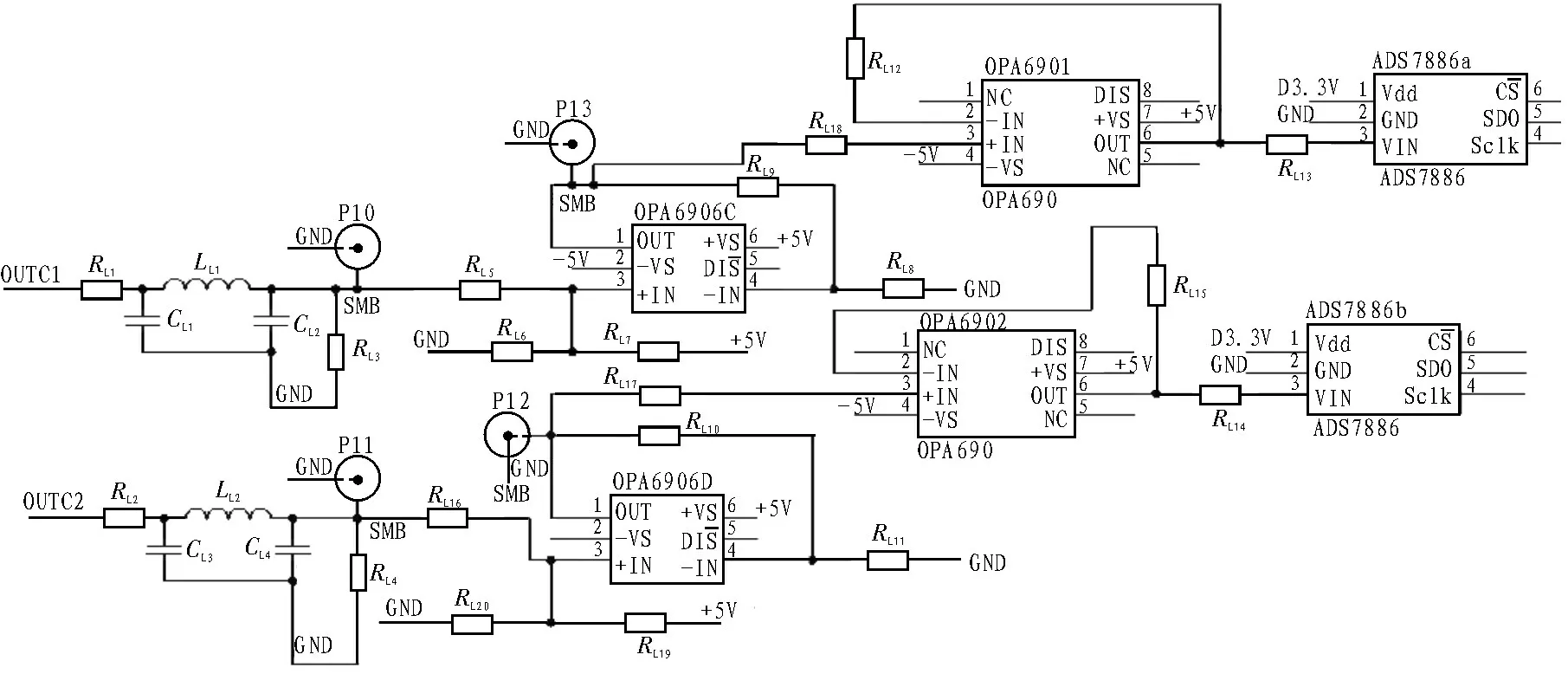

实际测试过程中发现随输入频率变化,AD835输出信号幅度会出现一定程度的衰减,为了保证混频器正常工作,使用OPA690 作为基础芯片设计制作了增益调理模块。经测试,在80~110 MHz 的频率带宽下,幅度和相位不会出现明显失真,符合系统对混频器的要求,加入增益放大模块后电路可以正常工作。

3.4 AD608电路设计

AD608 内部包含混频器、限幅器,具有接收信号强度指示功能。此次设计,使用该芯片及其外围电路作为辅助验证系统,电路原理以及电路设计图如图2 所示。

图2 AD608电路设计图

4 程序设计

4.1 程序设计思路

超外差频谱分析仪调节本振源的频率步进输出,同时采集不同频点信号的幅度,将两者记录后得到幅度随频率变化的曲线,即为频谱分析的结果。该设计中利用FPGA 调节HMC830 本振源的频率,同时对中频A/DC 采集的信号强度进行记录,最后在TFT 彩色屏上显示被测信号的频谱。

4.2 信号频谱显示及杂散计算

需要显示的频谱图由201 个频率点组成,对应VGA 显示屏的201 列,同时将信号强度分别放置到不同行使用不同颜色显示。

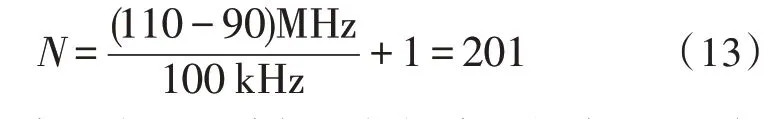

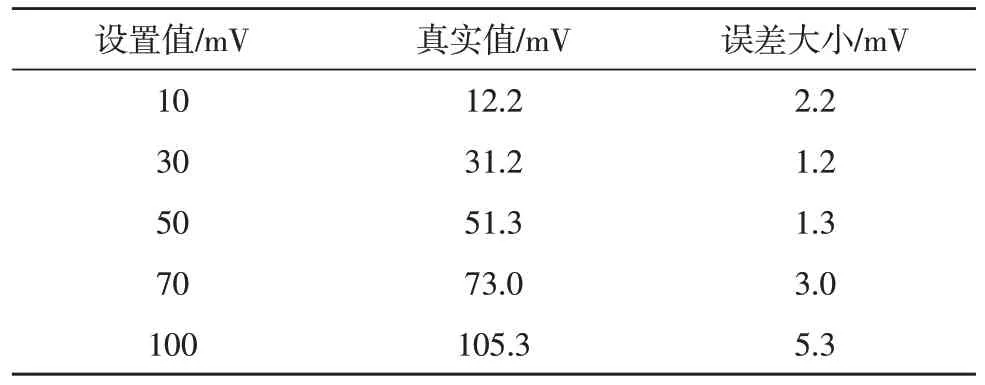

当频谱分辨率为100 kHz 时,频率范围为90~110 MHz,则频率调节点个数为:

设主频分量为A0,则大于主频分量幅度2%的杂散频率个数S的计算方法为:

5 测试结果及分析

5.1 锁相环本振源测试结果分析

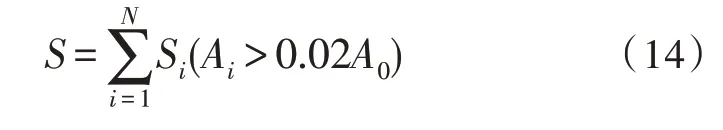

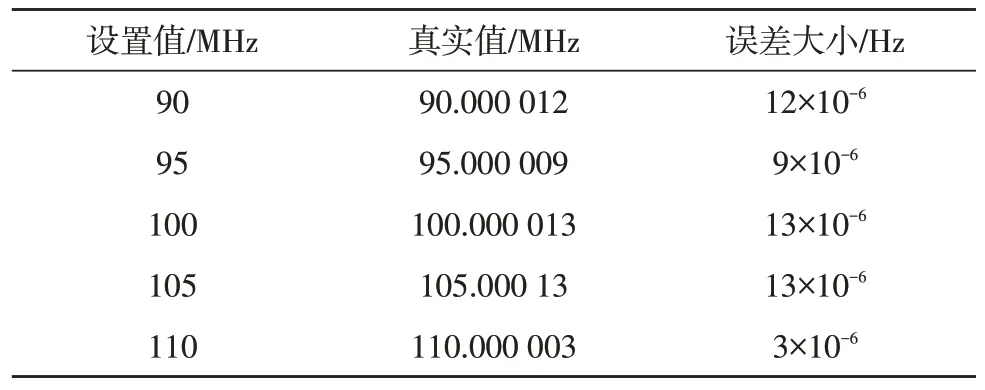

频率测试和幅度测试结果分别如表1、表2 所示。由表1 和表2 可以看出,在所选测量点处,频率测试误差均小于13×10-6MHz,而幅度测试误差小于5.3 mV,可以满足信号的测试要求。

表1 频率测试

表2 幅度测试

5.2 频谱分析仪测试结果分析

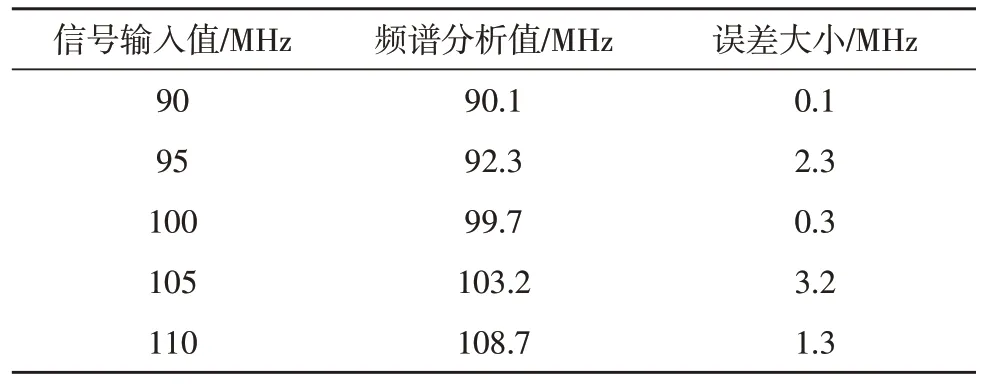

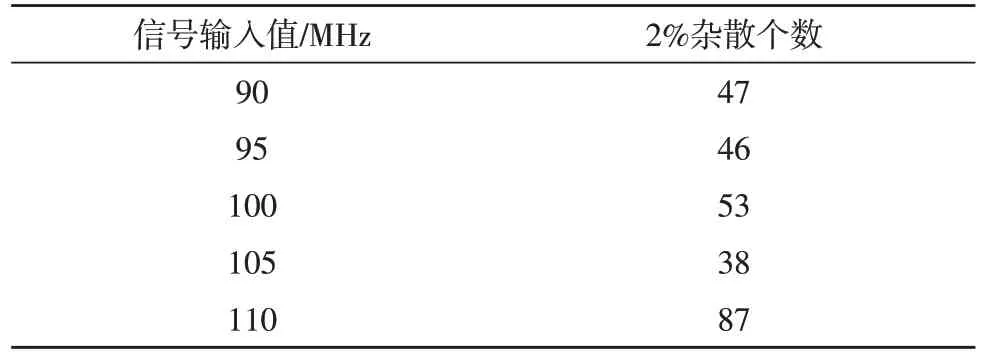

频率分析和杂散测试结果分别如表3、表4 所示。由表3 和表4 可以看出,频率分析的相对误差均小于3.1%,且可以准确测试杂散频率个数,测试性能良好。

表3 频率分析

表4 杂散测试

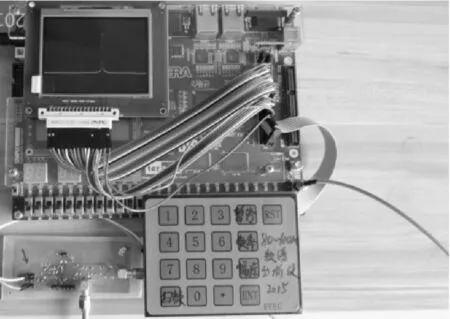

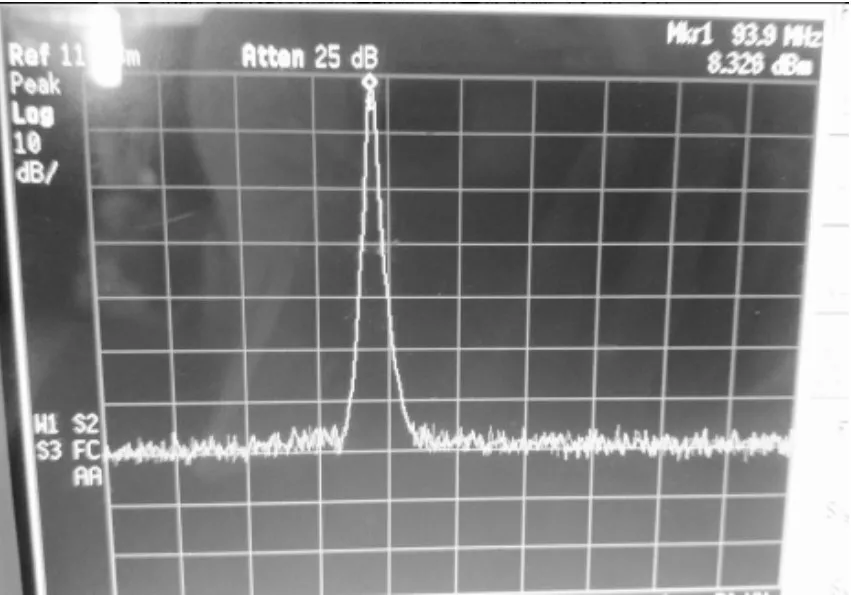

设计作品实物图和示波器显示锁相环输出调试图分别如图3、图4 所示。

图3 实物图

图4 锁相环输出调试图

6 结论

该系统根据设计要求基于超外差式原理,并结合高速可编程逻辑器件FPGA 设计而成。通过测试与分析,系统整体指标良好,可在80~110 MHz 频段内扫描并显示信号频谱和对应幅度最大的信号频率,输出电压幅度为10~100 mV分辨率达到了100 kHz,还能够测试在全频段内的杂散率个数。并且在整个频率范围内可自动扫描,扫描时间在1~5 s 之间可调,具有良好的人机接口,操作非常方便,整机便于携带,解决了传统示波器价格昂贵问题,适合高校的课程设计或电子创新实践活动。