一种应用于流水线ADC采样保持电路的设计

周佳宁,李荣宽

(电子科技大学电工学院,成都 611731)

1 引言

采样保持电路是实际应用中的重要单元电路之一[1],对于高速流水线模数转换器(Pipeline ADC)更是不可或缺的。采样保持电路位于流水线模数转换器的前端,其信号精度和建立速度直接影响整个流水线ADC的分辨率和转换速率[2]。

本文设计的采样保持电路采用全差分电容翻转型结构,能减小其噪声和功耗。通过下极板采样技术和适当的时序控制,极大地减小与输入信号相关的沟道电荷注入和时钟馈通误差;采用一种改进的栅压自举开关,减小采样保持电路的非线性失真;设计增益增强型折叠式共源共栅运算放大器,减少由有限增益和不完全建立带来的误差。该采样保持电路在JAZZ 5V、0.6μm BiCMOS工艺下,当采样频率为10MHz、输入信号频率为1MHz时,仿真得到其无杂散动态范围为107.8dB、信号噪声失真比为87.8dB、总谐波失真比为-105.2dB,满足12位、10MS/s流水线ADC的精度要求。

2 采样保持电路结构

采样保持电路由开关电容电路实现,主要有两种常用的结构[2],分别为电荷转移型(Charge-Transferring)和电容翻转型(Flip - Around)。

电容翻转型采样保持电路的反馈系数为采样电容与连接在运放输入节点的总电容之比。若忽略运放的输入寄生电容,此时反馈系数约等于1。因此,在相同的闭环带宽(即3-dB带宽)的情况下,相比电荷转移型结构,其单位增益带宽可以减小一半,这就意味着能大幅度地降低功耗。同时,更大的反馈系数也减小了接近一半的噪声[3]。

由于低噪声、低功耗和节省面积等方面的优势,流水线ADC前端采用电容翻转型采样保持电路,其结构如图1所示。在采样周期,开关S1、S2、S3和S4闭合,电容Cs1、Cs2的上极板连接在信号输入端,其下极板连接在运放的输入端。在保持周期,开关S9和S10闭合,电容Cs1、Cs2与信号输入端断开,同时连接在运放输出端。无论共模电荷还是差模电荷都将被转移到输出端。

图1 电容翻转型采样保持电路原理图

虽然共模反馈电路将输出共模强制为一定的值,但是放大器的输入共模电平将随着输入信号共模电平与放大器的输出共模电平的差值而变化。因此,运算放大器必须具有处理很大的输入共模变化的能力。

开关的电荷注入和时钟馈通效应导致的误差,可以通过两种方法减小[3],一是全差分电路的下极板采样技术,二是控制开关的关断时序,即开关S3、S4在S1、S2之前断开。

电容并不引起噪声,但是对电路噪声有着直接的影响。开关的导通电阻引入了热噪声,当开关断开时,这个噪声的瞬时值保存在电容上:

其中K为波尔兹曼常量、T为绝对温度。

由式(1)可知,采样电容值越小,热噪声就越大,则电路的信噪比(SNR)就会降低;反之,则电路的功耗及芯片面积均会增大。所以采样电容值需要在信噪比、功耗、速度和芯片面积之间进行折中。

3 栅压自举开关

在高速应用中,电路的性能与开关有着密切的关系。以NMOS开关为例,导通电阻如式(2)所示:

μn、Cox是均与工艺相关的参数,分别为电子的迁移率和栅氧化层厚度,W/L是开关管的宽长比。

由文献[4]可知,与采样保持电路性能相关的是采样开关的电阻和线性度,其中电阻值的大小决定电路的工作速度,而电阻的线性度决定其能达到的精度。

采样开关S1、S2采用栅压自举电路,能有效地提高电路的线性度,减少与信号相关的电荷注入误差。图2所示的栅压自举开关是文献[5]中提出栅压自举开关的改进。

图2 栅压自举开关电路图

图2所示为一种简化的栅压自举开关电路,仅需要一个电容,节省了芯片的面积。引入了并联的晶体管M11,能有效减小自举开关的导通电阻,其宽长比约为M10的1/100。当时钟信号Clk为低电平时,晶体管M7和M8导通,因此晶体管M10和M11关断。同时,电容C被充电至电源电压Vdd;当Clk为高电平时,晶体管M2导通,拉低了M6的栅极电压,使电容C的电荷对晶体管M10的栅极充电并使得晶体管M9和M10导通。此时,晶体管M10的栅源电压(VGS)独立于输入信号,其值约等于电源电压Vdd。

4 运放优化设计

运算放大器是采样保持电路的核心部分,决定了该电路的精度和建立时间[6,7],同时也消耗了绝大部分的功耗。

12位、10MS/s 流水线ADC要求运放的增益误差εgain和线性建立误差εsettle均小于1/2LSB[8],可得关于运算放大器的直流增益(A0)和单位增益带宽(GBW)表达式:

式(3)和(4)中,FS为采样频率、f是采样保持电路的反馈系数,且f≈1。其中式(3)中的线性建立时间约为周期的1/3,这是考虑了转换速率(SR)的影响。

由式(3)和(4)计算可得,运放所需要的直流增益(A0)和单位增益带宽(GBW)分别为78dB和43MHz。实际运算放大器直流增益和单位增益带宽设计时应该留有足够大的裕量。

从增益、带宽、共模输入范围和功耗等方面综合考虑,运放采用PMOS作输入对的折叠式共源共栅结构。为了进一步增加运算放大器的直流增益,采用增益提高结构(Gain-Boosted)和BiCMOS工艺中的NPN管,原理图如图3所示。

图3中,辅助运算放大器引入了新的零极点,可能会导致不稳定。假定f1是主运算放大器的单位增益带宽,f2是辅助运算放大器的单位增益带宽,f3是主运算放大器的第二个极点频率,它们之间应该满足式(5)的关系[9~10]:

式(5)的上限是为了保证运放的稳定性,下限是为了避免增加输出信号的稳定时间。主运算放大器和辅助运算放大器的电流比可设定为10:1。考虑到功耗和增益,差分运算放大器的共模负反馈用对称的开关电容电路(SC-CMFB)实现。

图3 增益增强型折叠式共源共栅运放原理图

5 仿真结果及版图

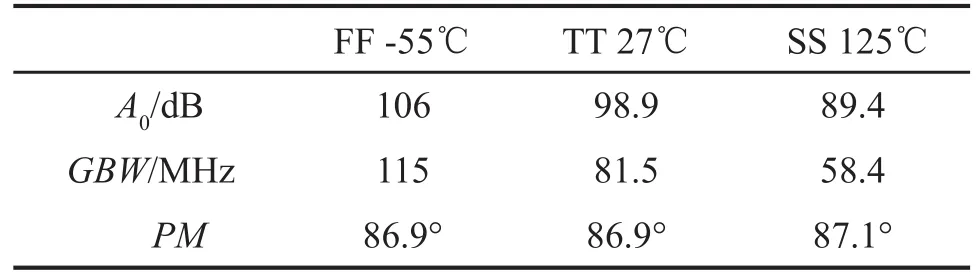

在JAZZ 5V、0.6μm BiCMOS工艺条件下,通过Spectre仿真得到运算放大器的幅频特性曲线如图4所示。

图 4 运算放大器的幅频特性曲线

工艺角TT和温度27℃下,仿真结果显示运放的直流增益为98.9dB,单位增益带宽为81.5MHz,相位裕度为86.9°,满足设计要求。噪声分析可知,运放的等效输入噪声为

表1 不同工艺角和温度下运放幅频特性比较

在不同的工艺角和温度下,运放的直流增益(A0)、单位增益带宽(GBW)和相位裕度(PM)仿真得到结果如表1所示。在工艺角和温度分别为SS和125℃的情况下,运放的增益和单位增益带宽有一定程度的减小,但仍然满足由式(3)和(4)计算所需的要求。

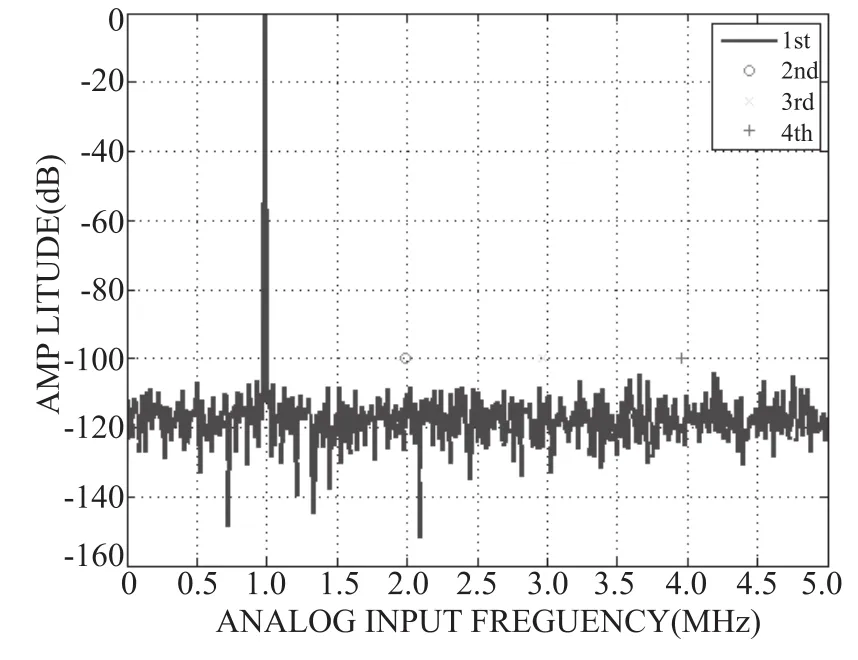

在采样频率为10MHz、输入信号频率为1MHz时,采样保持电路的差分输出结果经过快速傅里叶变换(FFT),得到如图5所示的频谱。

图5 ADC输出信号的频谱

通过计算可得,该采样保持电路的信噪比(SNR)、无杂散动态范围(SFDR)和总谐波失真比(THD)分别为81.2dB、107.8dB和 -105.2dB。采样保持电路性能在不同的工艺角和温度下有着很大的变化,结果如表2所示。

表2 不同工艺角和温度对电路性能的影响

图6 系统整体电路版图

从表2可以看出,在工艺角和温度分别为SS和125℃的情况下,采样保持电路的性能最差,这是由于运放的特性此时有了较大幅度的衰减。此时,SNR仍然达到77.5dB,可以达到12.6位的精度。

图6为包括流水线ADC在内的系统整体版图,其中采样保持电路为图中边框所标示部分,版图面积为0.4mm×0.8mm,该部分的功耗为11mW。

6 结论

本文设计了一个应用于12bit、10MHz低功耗的流水线ADC的高性能采样保持电路。采用了全差分电容翻转型结构来实现,运用了下极板采样和适当的时序控制,减小了噪声、功耗和电荷注入误差等。设计了增益增强型折叠式共源共栅BiCMOS运算放大器,获得了较高的直流增益和带宽,使其在较低的功耗下达到较好的性能,增加了一种改善线性度的栅压自举开关。在5V、0.6μm BiCMOS工艺中,当输入信号频率为1MHz和采样频率为10MHz时,能够达到87.8dB的信噪比、107.8dB无杂散动态范围和-105.2dB总谐波失真比。不同工艺角和温度情况下的仿真结果表明该电路符合流水线ADC的要求,且其版图面积和功耗分别为0.4mm×0.8mm 和11mW。

[1] K. R. Stafford, R.A. Blanchard, P.R. Gray. A complete monolithic sample/hold amplifier[J].IEEE J. Solid-State Circuits, 1974, 9(6): 381-387.

[2] D.A. Johns, K. Martin. Analog Integrated Circuit Design[M]. Toronto: John Wiley & Sons, 1997: 334-365.

[3] A. Boni, A. Pierazzi, C. Morandi. A 10-b 185-MS/s trackand-hold in 0.35-μm CMOS[J]. IEEE J. Solid-State Circuits, 2001, 36:195-203.

[4] 杨斌,殷秀梅,杨华中. 一种高速高精度采样/保持电路[J]. 半导体学报,2007,28(10):1642-1646.

[5] A.M. Abo, P.R. Gray. A 1.5V, 10 bits, 14.3-MS/s CMOS pipeline analog-to-digital converter[J]. IEEE J. Solid-State Circuits, 1999, 34:599-606.

[6] F. Centurelli, P. Monsurrò, S. Pennisi, et al. Design Solutions for Sample-and-Hold Circuits in CMOS Nanometer Technologies[J]. IEEE TRANSACTIONS ON CIRCUITS AND SYSTEMS—II: EXPRESS BRIEFS,2009, 56(6):459-463.

[7] L. Dai, R. Harjani. CMOS Switched Op-Amp-Based Sample-and-Hold Circuit[J]. IEEE Journal of Solid-State Circuits, 2000, 35(1):109-113.

[8] He-Gong Wei, U-Fat Chio, Yan Zhu. A Rapid Power-Switchable Track-and-Hold Amplifier in 90nm CMOS [J]. IEEE Transactions on circuits and systems—II: EXPRESS BRIEFS, 2010, 57(1):16 -20.

[9] Tsung-Sum Lee, Chi-Chang Lu. A 250MHz 11 bit 22mW CMOS low-hold-pedestal fully differential sampleand-hold circuit[J]. Analog Integr Circ Sig Process, 2009,58:105-113.

[10] Razavi, B. Design of a 100MHz 10mW 3V sample- and hold amplifier in digital bipolar technology[J]. IEEE Journal of Solid-State Circuits,1995, 30: 724-730.