Lx5280模拟器移植设计及实施

夏兴昇

(江苏经贸职业技术学院 江苏 南京 211168)

在分析模拟器基本原理,剖析GNU模拟器源程序,及分析了Lx5280新增部分的基础上,开始对模拟器进行移植,下面是移植设计及实施。

1 移植设计

1.1 Lx5280增加的结构和指令总结

经过第三章Lx5280结构分析,总结出Lx5280在结构上增加有:

(1)采取超标量流水线结构

(2)增加 Circular Buffers

(3)增加 Zero Overhead Loop 功能

(4)增加了一个用于乘除的DMAC单元

(5)增加了8个高优先级中断

增加的指令有六大类:

(1)双字读写指令

LT、ST

从存储器读写双字(64位)到一对偶数开始的通用寄存器中。

(2)Circular Buffers 存取操作指令(指令含”P”)

LBP[.Cn]、 LBPU[.Cn]、LHP[.Cn]、 LHPU[.Cn]、 LWP[.Cn]、LTP[.Cn]、 SBP[.Cn]、SHP[.Cn]、 SWP[.Cn]、STP[.Cn]

(3)对新增寄存器操作指令

MFRU、 MTRU 读 写 cbe[0-2]、cbs[0-2]、lpc0、lps0、lpe0、mmd

MFRK、MTRK 读写Lexra-Cop0kernal寄存器(目前保留)

MFLXC0 、MTLXC0 读 写 ESTATUS、ECAUSE、INTVEC

(4)DMAC 操作指令

CMULTA

DIVA(U)

MULTA(U)、MULTA2、MADDA(U)、MADDA2[.S]

MSUBA(U)、MSUBA2[.S]、MULNA2 、

SUBMA[.s]、ADDMA[.s]

MTA2[.G]、MFA、MFA2

RNDA2

(5)算数操作指令、

ADDR、SUBR、SLTR、SLLV、SRLV、SRAV、MIN、MAX、ABSR、MUX、CLS、BITREV

(6)条件转移指令

CMVEQZ[.H][.L]、CMVNEZ[.H][.L]

1.2 移植设计分析

下面按照配置文件修改,对新增结构支持,对新增指令支持的顺序进行分析。

1.2.1 要求产生的模拟器为支持Lx5280的模拟器,将配置时的target定为lx5280。这就需要对configure文件进行修改,以支持target=lx5280。对于mips和lx5280在基本配置上都一样,只是他们的指令集不同(mips用MIPS1指令集,lx5280用lx5280指令集),所以在非指令集配置中含有mips选项的就增加lx5280选项,而对于指令集配置要对lx5280单独配置。

1.2.2 对于新增超标量流水线结构,如前面所述,它不影响程序的执行,而且模拟它并不能提高模拟器的速度,所以不移植。

1.2.3 对于 Circular Buffers。 它包含 cbs[0-2]、cbe[0-2]六个32位寄存器,增加到原来的寄存器组registers中即可,相关指令会根据其内容进行操作。

1.2.4 对于 Zero Overhead Loop 功能。 它包含 lps0、lpe0、lpc0三个32位寄存器。同样增加到原来的寄存器组registers中。可但它的行为并不是靠指令驱动的,而是在每条指令执行期间都会发生,并且是靠硬件完成的,判断PC值是否和它的寄存器值相匹配。可以在每条指令行为函数中加上,但这很冗长。我的解决方法是在指令生成程序igen的源程序gen-semantics.c文件中加上其行为。编译后用它处理*.igen文件,产生的semantic.c文件中每条指令都会包含Zero Overhead Loop的行为。

1.2.5 对于 DMAC 单元,包含 m0l、m0h、m1l、m1h、m2l、m2h、m3l、m3h八个40位累加器和一个mmd 32位寄存器。mmd寄存器可以添加到原来的寄存器组registers中,但m0l、m0h、m1l、m1h、m2l、m2h、m3l、m3h 八个累加器是 40 位的,registers寄存器数组是32位的,模仿原浮点寄存器结构,另外增加一个mul[8]数组。DMAC相关指令会对其操作

1.2.6 对于新增中断。 包含 estatus、ecause、intvec 三个 32 位寄存器。如前所述,由于本模拟器并不模拟cpu引脚,就在registers中添加estatus、ecause、intvec三个32位寄存器。如果需要模拟引脚,可添加一个模拟cpu端口的外部设备。

1.2.7 对于新增指令,虽然指令较多,但模拟都是写一个指令行为函数和它的指令编码结构(供生成解码表)。把它们添加到一个指令生成文件radiax.igen中。在mips.igen中添加一条包含命令 (include radiax.igen)。 由于支持的 target是lx5280,对原来mips1的指令在mips.igen中增加对lx5280的支持。

1.2.8 另外,在源码分析中可以看到寄存器宽度和对寄存器读写对新增寄存器也有影响,对新增寄存器宽度加以修改,在寄存器读写函数中对累加器操作要重新定位到mul[]数组。

以上是对所有新增结构和指令的分析处理,把它们总结合并后按照以下顺序移植

1.3 移植顺序

1.3.1 配置文件修改

a、修改mips下的配置文件 sim/mips/configure和 sim/mips/configure.in

b、修改模拟器总的配置文件sim/configure和sim/configure.in

1.3.2 添加新增寄存器

为了是模拟器支持对新增寄存器操作,作如下顺序修改

a、添加寄存器到数组

b、修改寄存器长度寄存器

c、修改寄存器读写操作函数

1.3.3 添加新增指令

a、修改原有mips.igen文件

b、新增radiax.igen指令文件

作了以上移植分析设计后,开始移植代码。下面是具体实现。

2 配置文件的修改

在程序编译前,用configure来指定target。为了支持Lx5280,需对configure进行修改。对于mips和lx5280在基本配置上都一样,只是他们的指令集不同(mips用MIPS1指令集,lx5280用lx5280指令集),所以在非指令集配置中含有mips选项的就增加lx5280选项,而对于指令集配置要对lx5280单独配置。修改如下:

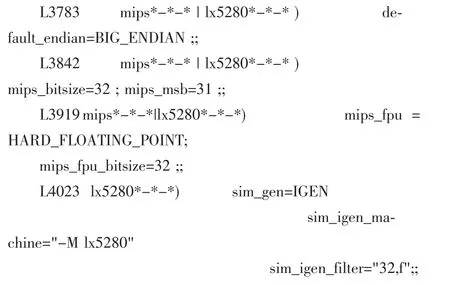

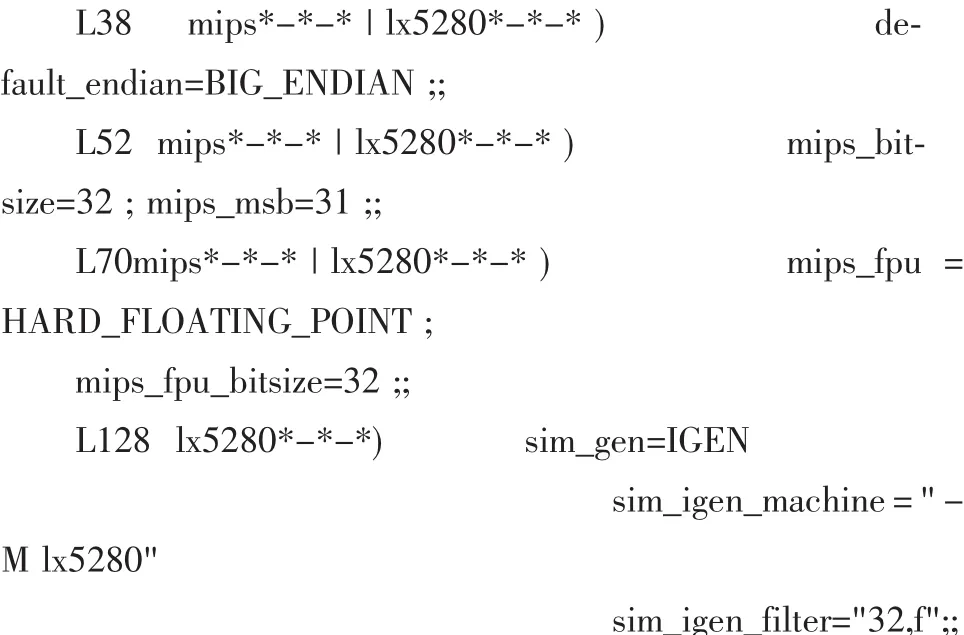

2.1 对 sim/mips/configure的修改

L1435 mips*-*-*|lx5280*-*-*)

2.2 对 sim/mips/configure.in的修改

L74 mips*-*-*|lx5280*-*-*)

2.3 对 sim/configure的修改

2.4 对 sim/configure.in的修改

3 添加新增Register及修改相关操作

Lx5280新增寄存器有

cbs0、cbs1、cbs2、cbe0、cbe1、cbe2、lps0、lpe0、lpc0、mmd、estatus、ecause、intvec、(32 位,13 个,用原有 registers数组,增加数组元素)

m0l、m0h、m1l、m1h、m2l、m2h、m3l、m3h(64 位模拟 40 位寄存器,8个,用新增mul数组)

对寄存器操作有:

写寄存器操作sim_store_register()

读寄存器操作sim_fetch_register()

对他们修改如下:

3.1 增加寄存器

按寄存器位宽度把增加寄存器分成32位(13个)和40位(8个)两组,一共21个新增寄存器。作的修改为

3.1.1 修改总寄存器数,原有寄存器LAST_EMBED_REGNUM是89,现在把它增加21个为110。这样寄存器数组定义也由registers[89+1]变成registers[110+1]。新增寄存器编号从90-110。

3.1.2 由于REGISTERS数组宽度是按通用寄存器宽度定义的(32位),而8个累加器寄存器是40位的,就必须另外增加一个累加器的数组mul[],由于数据类型没有40位整数,定义mul[]的长度是64位,在寄存器操作时会对它们作40的溢出处理。这8个累加器在REGISTERS[]的位置仍然保留,以保证寄存器序号的唯一性。

对源程序修改如下:

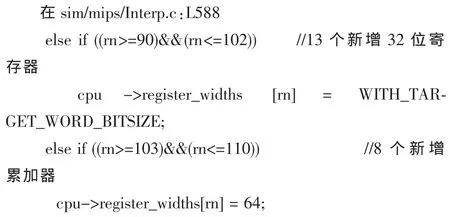

3.2 设置新增寄存器宽度

在读写寄存器的时候,模拟器会检验读写数据宽度是否和寄存器宽度相同,如果不同则返回失败(寄存器宽度存放在register_widths[]数组中),所以要对新增寄存器的宽度进行修改,修改如下

3.3 修改读写寄存器函数的实现

写寄存器操作函数sim_store_register()

读寄存器操作函数sim_fetch_register()

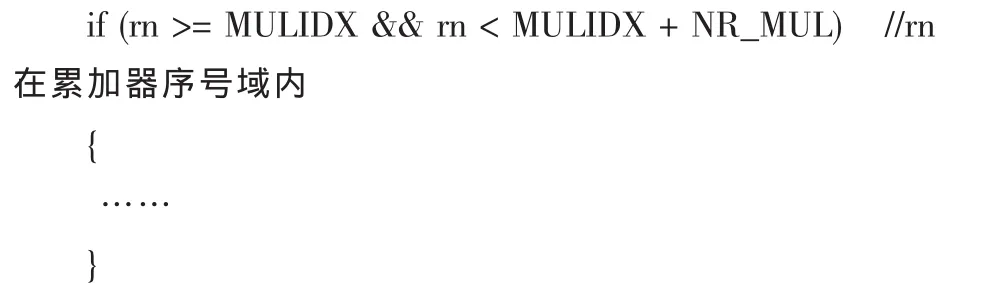

在这两个函数中会根据寄存器序号及读写宽度决定读写位置及返回值,缺省是对registers读写,由于新增的8个累加器在mul[]数组,对它们的读写要指向mul[]数组,修改如下:

3.3.1 写寄存器 sim_store_register () 在 sim/mips/interp.c L977

3.3.2 读寄存器 sim_fetch_register 在 sim/mips/interp.c L882

4 添加Radiax指令集

为了使igen文件模块化,且易于维护,在这里新增了radiax.igen指令文件,保存新增指令,关于新增指令的igen格式详见3.8节指令生成

由于代码量太大,这里列举部分例子,详见mips.igen、lx5280.igen、radiax.h 文件

4.1 修改原有 Mips.igen

4.1.1 增加 lx5280 model,igen 会将其加入 model列表

L46 :model::lx5280:lx5280:

4.1.2 由于新增指令在radiax.igen文件中, 这里也要把它包含进来。

L4000 :include::radiax.igen

4.1.3 lx5280指令集包含MIPSI指令集和RADIAX指令集。对原有MIPS1指令增加对lx5280 mode的支持。

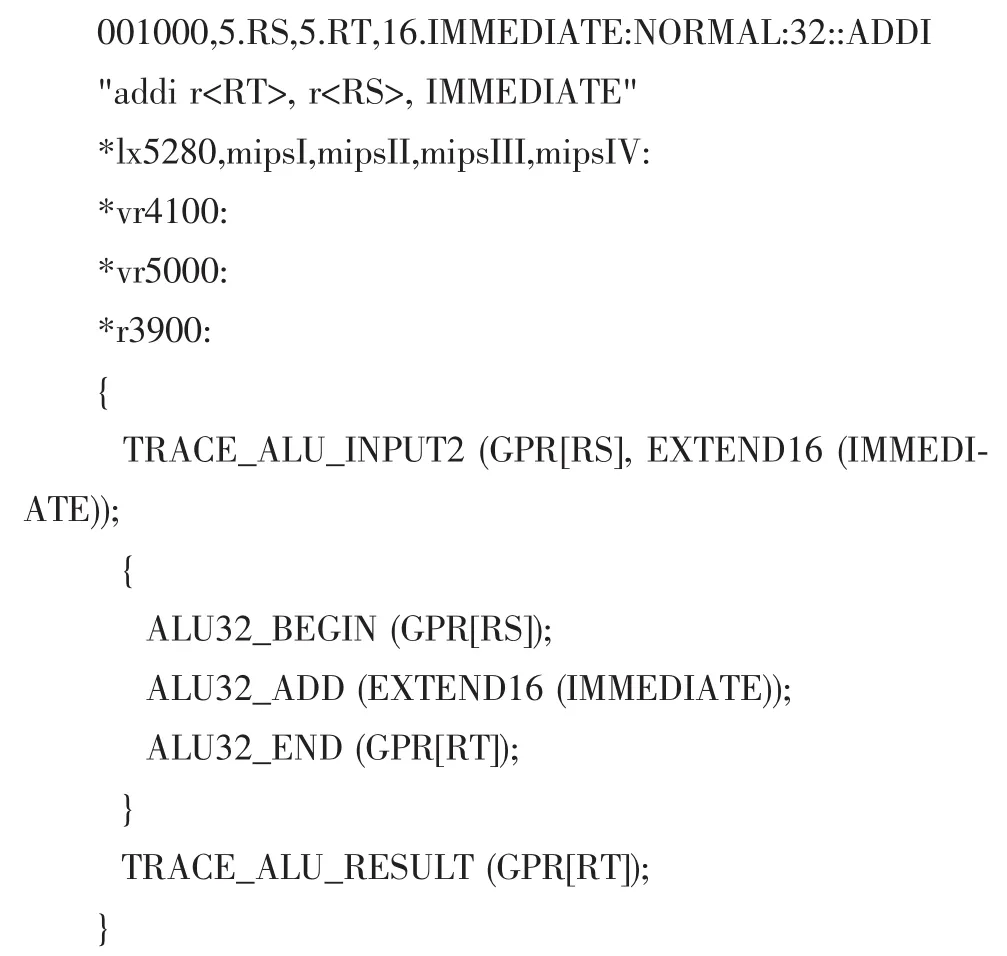

例如带立即数加法指令(粗体为添加内容):

4.2 增加 radiax.igen

4.2.1 把所有 Radiax指令按 igen指令格式添加到 radiax.igen文件

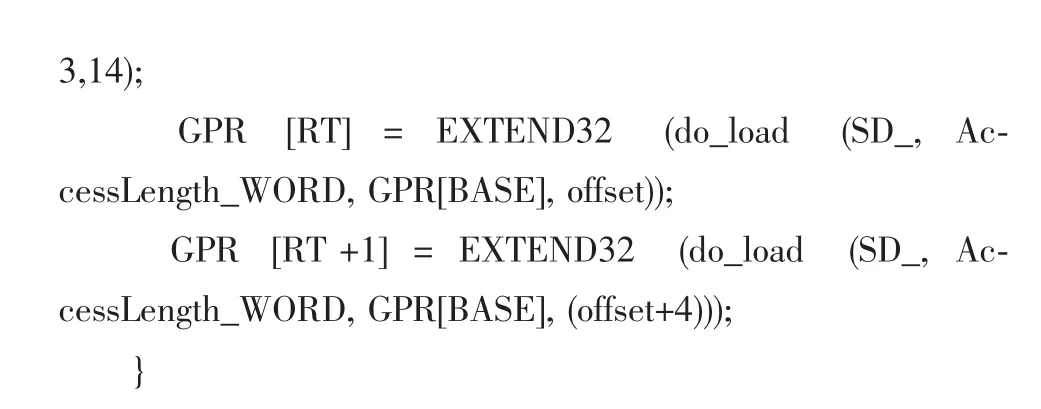

例如读双字操作指令的igen形式:

4.2.2 在radiax.igen需要用到的一些宏定义,把它们写入radiax.h,并包含到sim-main.h中

#include"radiax.h"

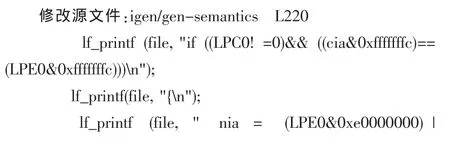

5 对Zero Overhead Loop支持

Zero Overhead Loop结构参见4.2.1节 Lx5280新增结构。它的LPC0、LPS0、LPE0三个寄存器在5.2.1节增加寄存器已添加。但它的行为并不是靠指令驱动的,而是在每条指令执行期间都会发生,并且是靠硬件完成的。按移植设计,在指令生成程序gen-semantics中加上其行为。编译后用它处理*.igen文件,产生的semantic.c文件中每条指令都会包含Zero Overhead Loop的行为。

具体实施如下:

6 移植正确性测试

在移植之后产生的针对Lx5280的模拟器是否符合需求,我采用联合测试的方法,和汇编器as、调试器insight(gdb窗口形式)共同测试。综合考虑对新增寄存器和对新增指令的测试,由于添加的寄存器和指令结合紧密,我采用对Lx5280各个新增功能分模块测试。

被测指令程序的装载,我通过两种方式:

6.1 通过汇编程序汇编指令后通过insight装入。

6.2 在Lx5280汇编没有移植好前通过手动汇编方式。在insight寄存器窗口给寄存器赋值及指令memory窗口在当前指令地址处写入手动汇编指令的的机器指令码。这种方式也适用于在汇编、调试、模拟器联合调试时确认错误范围。同时可以增加测试的灵活性

采用单步测试方法,测试结果通过insight寄存器窗口和memory窗口观察。

经调试、修改后的模拟器通过了上述详细测试,证明模拟器能够可靠使用,表明移植成功,实现了项目目标。