用于时间延迟积分型图像传感器的流水采样列级运放共享累加器*

夏 雨,姚素英,聂凯明,徐江涛

(天津大学电子信息工程学院,天津 300072)

用于时间延迟积分型图像传感器的流水采样列级运放共享累加器*

夏 雨,姚素英,聂凯明,徐江涛*

(天津大学电子信息工程学院,天津 300072)

提出了一种适用于TDI-CIS(时间延迟积分CMOS图像传感器)的模拟域流水采样列级运放共享累加器结构。提出的这种模拟累加器结构应用流水采样结构在不改变运放速率的前提下,将累加器的速率提升为传统累加器的2倍;采用积分电容列运放共享技术将n级TDI-CIS所需的运放个数减少至采用传统累加器所需个数的1/n。分析了流水采样累加器结构的原理以及输出噪声。使用标准0.18 μm CMOS工艺进行了电路设计。仿真结果显示,提出的模拟累加器结构功耗为0.29 mW,采样率为2 Msample/s。结果表明流水采样列级运放共享累加器结构在保持低电路面积和功耗的同时,可将TDI-CIS最大可达到的行频增加一倍,更适于高速扫描的应用环境。

CMOS图像传感器;时间延迟积分;模拟累加器;流水采样;运放共享

时间延迟积分(TDI)型图像传感器的工作过程主要是通过线阵图像传感器以扫描的方式拍摄,同时将图像传感器对移动物体中同一目标的多次曝光结果进行累加,等效延长光信号积分时间[1],大幅提高光能吸收,以获得较高的信噪比(SNR)和灵敏度。其广泛应用于高速低光照的拍摄环境[2]。CMOS技术因低功耗、低成本、高集成度等特点,在逐步取代CCD技术在TDI图像传感器中的应用[3]。国内外已经有一定数量CMOS TDI图像传感器方案面世,但均有一定程度的缺陷。美国Cypress公司在2006年提出了一种25级的采用模拟域累加器的CMOS TDI图像传感器[4]。但是在这种图像传感器中,每一级时间延迟积分均需要一个独立的运放以及相应的累加电容,从而导致这种图像传感器需要很大的功耗和面积。台湾国立清华大学在2012年提出了基于四管像素和相邻像素信号传输方式的8级TDI-CIS[5]。但是,在这种结构中,相邻像素之间共享两个晶体管,从而增加了像素设计的难度。

在本课题组之前的工作中[6],为减小功耗和面积,提出了一种采用列级运放共享的模拟域累加器的32级CMOS TDI图像传感器。之后,为减少因运放共享产生的非累加状态积分电容寄生效应对于累加结果的影响,提出了一种去耦合补偿电容结构[7]。但是有限的运放速度和列级运放共享方案限制了图像传感器的行频,从而限制了TDI图像传感器的扫描速度。为解决这一问题,本文提出了适用于TDI-CIS的模拟域流水采样列运放共享累加器结构。相对于文献[7]中的累加器,这种结构可以在不改变运放速度,且不增加电路面积的情况下,将TDI-CMOS图像传感器的读出速率增大一倍,从而提升了TDI-CMOS图像传感器的最大扫描速度。

1 传统模拟域累加器

(1)

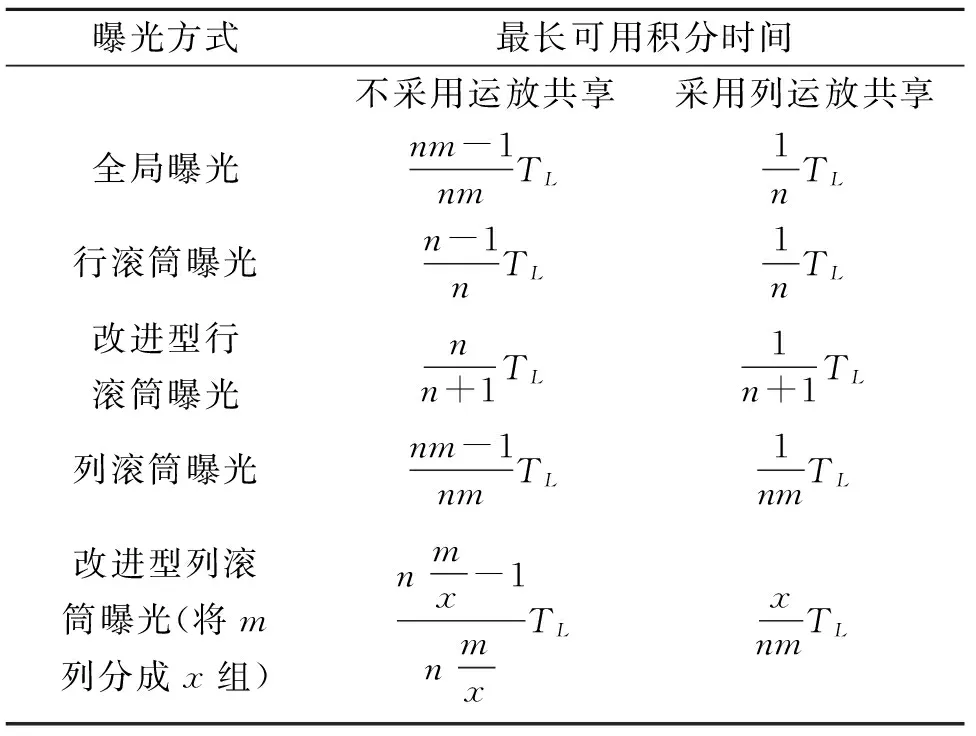

为获得更高的信噪比以提升TDI图像的质量,需要尽可能的提升TDI电路的级数。对于TDI像素阵列信号的不同的曝光方式和读出方案[8],每个像素信号的读出周期不同。以一个渡越时间(图像传感器相对于被拍摄物移动一个像素距离的时间)为TL的n行m列TDI图像像传感器为例,对于不同的曝光方式[9]和读出方案,其阵列中每个像素信号的最长可用的积分时间如表1所示。

表1 不同曝光方式下最长积分时间

同时,根据上文的讨论可知,为减少电路面积和功耗,对于TDI像素阵列的读出电路,通常采取运放共享技术。以n级累加器行滚筒曝光列级读出方案为例,在保持TDI图像传感器的渡越时间不变的情况下,运放的工作频率需要变为原来的n倍。因此运放有限的工作频率制约了TDI的设计级数的提升,也制约了图像传感器在更高速领域的应用。为了解决这一问题,提出了适用于TDI-CIS的模拟域流水采样列运放共享累加器结构。

以一级TDI-CIS为例,传统的累加器电路结构如图1所示。其中,Vin表示像素输出的电压信号,Vout表示累加器输出的累加完成电压信号,Vref表示累加器中的参考电压信号,CS为采样电容,CH为积分电容,clk1、clk2为控制电路中开关的两相不交叠时钟,OPA表示电路中所使用的运算放大器。

图1 传统模拟域累加器电路结构

传统的累加器时序如图2所示,其中的Tnonoverlap表示两相不交叠时间,Tclk表示clk1(clk2)的时钟周期。

图2 传统累加器时序

图2中符号①所示的状态为传统累加器结构的采样态:clk1为高电平,其所控制的开关闭合;clk2为低电平,其所控制的开关断开。传统累加器的采样状态电路结构如图3所示。

图3 传统累加器采样态

运放的正输入端接入参考电压,用Vin+表示运放正输入端的电压,则Vin+=Vref。

同时,根据运放的虚短路特性,用Vin-表示运放负输入端的电压,则有Vin-=Vin+=Vref。

存储在采样电容CS上的电荷QCS为

QCS=(Vin-Vin-)CS=(Vin-Vref)CS

(2)

此时运放输出端的电压Vout为

Vout=Vin-=Vref

(3)

图2中符号②所示的状态为传统累加器结构的保持态:clk1为低电平,其所控制的开关断开;clk2为高电平,其所控制的开关闭合。传统累加器的保持状态电路结构如图4所示。

图4 传统累加器保持态

(4)

(5)

上一次积分保持态时,存储在积分电容CH上的电荷为QCH,累加器的输出电压为Vout,n-1,则

QCH=(Vout,n-1-Vin-)CH

(6)

由于运放输入端没有电荷通路,根据电荷守恒原理,有

(7)

根据式(2)、式(4)~式(7),可以得出

(8)

这就是传统累加器的累加原理。每个时钟周期Tclk内,传统累加器完成一次积分过程。

2 流水采样模拟域累加器

2.1 结构原理

流水采样的累加器结构在传统累加器的结构基础上进行了改进,具体电路结构如图5所示。其中,Vin1、Vin2表示累加次序相邻的两像素输出的电压信号,Vout表示累加器输出的累加完成电压信号,Vref表示累加器中的参考电压信号,CS1、CS2为两个交替工作的采样电容,CH为积分电容,clk1、clk2为控制电路中开关的两相不交叠时钟,clk3为复位时钟,OPA表示电路中所使用的运算放大器。

图5 流水采样累加器电路结构

流水采样的累加器时序如图6所示,其中的Tnonoverlap表示两相不交叠时间,Tclk表示clk1(clk2)的时钟周期。clk3仅在开始时为高电平以使积分电容CH复位,清空其中所带的电荷。

图6 流水采样累加器时序

图6中符号①所示的状态为流水采样的累加器结构的复位状态:clk1、clk2为低电平,其所控制的开关断开;clk3为高电平,其所控制的开关闭合。流水采样累加器结构的复位状态电路结构如图7所示。

图7 流水采样累加器结构的复位态

图8 CS1采样CS2保持状态

运放的输出端与运放的负输入端短接,同时积分电容CH的两端也短接在一起,积分电容CH中的电荷为QCH,1,则

QCH,1=0

(9)

图6中符号②所示的状态为流水采样的累加器结构的CS1采样CS2保持状态:clk2、clk3为低电平,其所控制的开关断开;clk1为高电平,其所控制的开关闭合。流水采样的累加器结构的CS1采样CS2保持状态电路结构如图8所示。

采样电容CS1中的电荷为QCS1,sample,则

QCS1,sample=(Vin1-Vref)CS1

(10)

积分电容CH中的电荷为QCH,n-1,累加器的输出电压为Vout,n-1;用Vin+表示运放正输入端的电压,用Vin-表示运放负输入端的电压,根据运放的虚短路特性则

QCH,n-1=(Vout,n-1-Vin-)CH=(Vout,n-1-Vin+)CH

=(Vout,n-1-Vref)CH

(11)

图6中符号③所示的状态为流水采样的累加器结构的CS2采样CS1保持状态:clk1、clk3为低电平,其所控制的开关断开;clk2为高电平,其所控制的开关闭合。流水采样的累加器结构的CS2采样CS1保持状态电路结构如图9所示。

图9 CS2采样CS1保持状态

采样电容CS1中的电荷为QCS1,hold,用Vin+表示运放正输入端的电压,用Vin-表示运放负输入端的电压,根据运放的虚短路特性

QCS1,hold=(Vin+-Vin-)CS1=0

(12)

积分电容CH中的电荷为QCH,n,累加器的输出电压为Vout,n,则

QCH,n=(Vout,n-Vin-)CH=(Vout,n-Vref)CH

(13)

由于运放输入端没有电荷通路,根据电荷守恒原理,有

QCS1,sample+QCH,n-1=QCS1,hold+QCH,n

(14)

根据式(10)~式(14),可以得出

(15)

对于行滚筒曝光方式的图像传感器,一般采用四管有源像素[10-11],如图10所示。

图10 四管有源像素

当RST与Sel均为高,TX为低时,Vpixel为输出的复位信号Vrst,当TX与Sel均为高,RST为低时,Vpixel为像素输出的曝光信号Vsig。

将Vrst信号代替累加器参考信号Vref输入累加器运放正输入端,将Vsig信号代替累加器输入信号Vin1(Vin2)输入累加器,则式(15)可以写为

(16)

式(16)展示了流水采样累加器进行像素信号累加且同时进行像素曝光信号与像素复位信号相关双采样的原理。

由于采样电容CS1与CS2交替工作,故每个时钟周期内,流水采样累加器可以完成两次式(16)所示的累加过程。对于相同的运放工作频率,即图2和图6中的Tclk相同,流水采样累加器的累加频率是传统累加器的累加频率的一倍。

将此流水采样累加器结构应用于TDI-CIS。以行滚筒曝光方式的n级TDI-CIS为例,相应累加器电路结构如图11所示。此结构不仅实现了积分电容(CH1到CHn)列运放共享,还实现了流水采样(CS1与CS2轮流采样)。流水采样积分电容列运放共享累加器结构在减少电路面积和功耗的同时,提升了累加速度。

图11 n级流水采样列运放共享累加器电路结构

2.2 噪声分析

本文提出的模拟域累加器电路中只含有MOS器件。MOS器件的本征噪声主要包括热噪声和1/f噪声。其中1/f噪声相比较小,因此可以忽略。在开关电容电路中,信号的建立时间通常是由运算放大器的带宽决定的,而并不由开关的导通电阻大小决定,因此开关电容电路的噪声是由运算放大器决定的。对于一个经过噪声优化设计的运算放大器来说,其等效输入噪声的功率谱密度S(f),可以近似表示为[12]:

(17)

式中:k是波尔兹曼常数,T是热力学温度,gm是运算放大器输入管的跨导。

(18)

式中:β是开关电容电路的反馈系数,CLtot是运算放大器的等效总负载电容。

由于流水采样电路中两个采样电容交替工作,考虑噪声影响时,其两个工作状态均可以等效为传统累加器的保持态。本文中所有电容大小均相同,电容值大小用C代表。其采样电容不接入运放,存储在采样电容中的噪声为

(19)

根据式(18),可得流水采样电容工作时,积分电容中采集到的噪声为:

(20)

对于n级模拟域累加器其采集到的总热噪声大小为:

(21)

当只考虑热噪声情况下,对于四级模拟域累加器在2 V输出摆幅下,模拟域累加器中电容选取1pF大小即可达到81.6dB的SNR,可满足系统10位精度的要求。

2.3 功耗与面积分析

本文设计的流水采样列运放共享累加器中使用单端输出折叠式共源共栅运放。

设此运放所需功耗为POPA,所占面积为SOPA,积分电容CH面积为SCH,采样电容面积为SCS,则用于行滚筒曝光n级TDI-CIS流水采样列运放共享累加器所需的功耗P1约为:

P1=POPA

(22)

所需要的面积约为

S1=SOPA+nSCH+2SCS

(23)

传统累加器所需的功耗P2约为

P2=nPOPA

(24)

由式(22)和式(24)可知,流水采样列运放共享累加器所需要的功耗为传统累加器所需功耗的1/n。

传统累加器所需的面积S2约为

S2=nSOPA+nSCH+nSCS

(25)

由式(23)和式(25)可知,流水采样累加器比传统累加器节省了n个运放和(n-2)个采样电容的面积。

3 仿真结果

本文使用标准0.18μmCMOS工艺进行了电路设计。仿真结果显示,文中提出的四级流水采样列运放共享模拟累加器结构功耗为0.29mW,相对于传统累加器减少了0.87mW;其采样率为2Msample/s,相对于传统累加器采样率1Msample/s,提升了一倍。

分别采用流水采样累加器和传统采样累加器的一级TDI-CIS瞬态仿真结果如图12所示。图12中,Vout<0>表示流水采样累加器的瞬态仿真结果;Vout<1>表示传统累加器的瞬态仿真结果;clk1(clk2)的时钟周期Tclk=2μ,clk1(clk2、clk3)脉宽为980ns,两相不交叠时间Tnonoverlap=20ns。

图12 一级流水采样累加器和传统采样累加器的仿真结果对比

图13 四级TDI-CIS流水采样累加器和传统采样累加器的仿真结果对比

从图12中可以看出,在相同的运放工作速度下,相较于传统累加器,流水采样累加器的累加速率提升了一倍。

分别采用流水采样累加器和传统采样累加器的行滚筒曝光方式的四级TDI-CIS瞬态仿真结果如图13所示。图13中,Vout<0>表示四级积分电容列运放共享流水采样累加器的瞬态仿真结果;Vout<1>表示四级积分电容列运放共享传统累加器的瞬态仿真结果。

从图13中可以看出,在相同的运放工作速度下,完成四级像素信号积分,流水采样累加器所需要的时间Tintegration,1仅为传统累加器所需时间Tintegration,2的一半。从而证明对于相同曝光方式、相同读出方案和级数,采用流水采样累加器的TDI-CIS最大可达到的行频相较于采用传统累加器的TDI-CIS最大可达到的行频增加了一倍,进而使得TDI-CIS最高扫描速度提升了一倍。

对于图11所示的电路引入随机噪声,仿真结果如图14所示。图14显示了与理想情况相比,引入的随机噪声导致了累加效果及信噪比的下降,且随着累加级数的上升,下降的情况愈明显。

图14 四级TDI-CIS流水采样累加器理想情况与引入噪声的仿真结果对比

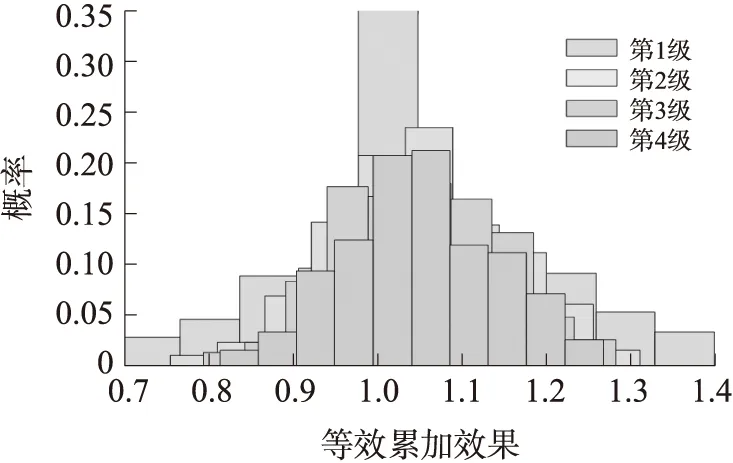

对于图11所示的电路进行工艺偏差和失配的蒙特卡洛仿真,仿真400次,得到等效累加效果与概率的关系,如图15所示。其中不同级数等效累加效果表示累加器不同级数下的蒙特卡洛仿真值与理想值之比。概率表示分布在相应区间上的仿真结果个数与总的仿真次数400之比。从图15可得,随着累加级数的增加,流水采样列运放共享累加电路对于工艺偏差及失配的容忍度提高。

图15 四级TDI-CIS流水采样累加器蒙特卡洛分布

4 结论

本文提出了一种适用于TDI-CIS的流水采样列运放共享累加器结构。理论分析与仿真结果表明,采取运放共享技术减少了电路面积和功耗;采用流水采样结构解决了运放有限的工作频率制约累加速率的问题。通过仿真结果验证了,采用积分电容列运放共享将n级TDI-CIS所需的运放个数减少至采用传统累加器所需个数的1/n;采用流水采样累加器结构的TDI-CIS的读出速度比传统模拟域累加器的读出速度提高了一倍,从而使得采用相同曝光方式和读出方案的TDI-CIS最大可达到的行频增加了一倍。结果表明本结构可以提升TDI-CIS最高扫描速度或提升TDI的设计级数,适用于高速拍摄的环境。

[1]Farrier M G,Dyck R H. A Large Area TDI Image Sensor for Low Light Level Imaging[J]. Solid-State Circuits,IEEE Journal of,1980,15(4):753-758.

[2]Barbe D F. Time Delay and Integration Image Sensors[J]. Solid State Imaging,1976:659-671.

[3]Gamal A El,Eltoukhy H. CMOS Image Sensors[J]. IEEE Circuits Devices Mag,2005,21(3):6-20.

[4]Lepage G,Dantes D,Diels W. CMOS Long Linear Array for Space Application[C]//Electronic Imaging 2006. International Society for Optics and Photonics,2006:606807-606807-8.

[5]Chang J H,Cheng K W,Hsieh C C,et al. Linear CMOS Image Sensor with Time-Delay Integration and Interlaced Super-Resolution Pixel[J]. Sensors,2012 IEEE,2012:1-4,28-31.

[6]Nie K,Yao S,Xu J,et al. Thirty Two-Stage CMOS TDI Image Sensor with on-Chip Analog Accumulator[J]. Very Large Scale Integration(VLSI)Systems,IEEE Transactions on,2014,22(4):951-956.

[7]Nie K,Yao S,Xu J,et al. A 128-Stage Analog Accumulator for CMOS TDI Image Sensor[J]. IEEE Trans Circuit and System-Ⅰ:Regular Papers. July 2014,61(7):1952-1961.

[8]Lepage G,Bogaerts J,Meynants G. Time-Delay-Integration Architectures in CMOS Image Sensors[J]. IEEE Trans Electron Devices,2009,56(11):2524-2533.

[9]李晓晨,姚素英,黄碧珍,等. 一种应用于高动态范围CMOS图像传感器的曝光控制技术[J]. 传感技术学报,2013,26(3):328-332.

[10]Place S,Carrere J P,Allegret S,et al. Rad Tolerant CMOS Image Sensor Based on Hole Collection 4T Pixel Pinned Photodiode[J]. Nuclear Science,IEEE Transactions,2012,59(6):2888-2893.

[11]孙权,姚素英,徐江涛,等. 四管像素满阱容量影响因素研究[J]. 传感技术学报,2013,26(6):815-819.

[12]Gao C,Yao S,Xu J,et al. Analysis of Noise of Current Accumulator in Time-Delay-Integration CMOS Image Sensor[C]//Electron Devices and Solid-State Circuits(EDSSC),2011 International Conference,2011:17-18.

[13]Xie B,Zhao L,Fu Y. An LWIR Imaging System with Low Noise Characteristic Based on CMOS TDI Detector[C]//Signal Processing(ICSP),2010 IEEE 10th International Conference. 2010:413,416,24-28.

A Pipelined Sampling Accumulator with Opamp Sharing Technique Fit for CMOS TDI Image Sensor*

XIAYu,YAOSuying,NIEKaiming,XUJiangtao*

(School of Electronic Information Engineering,Tianjin University,Tianjin 300072,China)

A novel pipelined sampling accumulator structure with opamp sharing technique is presented,which is fit for CMOS TDI(time-delay-integration)image sensor. The sampling speed of the analog accumulator can be doubled with only 1 opamp instead of n opamps for ann-stage accumulator. This structure decreases chip area and power dissipation and increases accumulating speed as well. This paper illustrates the topology of the proposed structure and analyzes the output noise. The proposed circuit is designed in a 0.18 μm CMOS process. Simulation results show that the power dissipation of the proposed circuit is 0.29 mW under 3.3 V voltage supply,and the sampling rate of the accumulator is 2 Msample/s. It proves that the proposed accumulator structure is suitable to the application at high scanning speed.

CMOS image sensor;TDI;analog accumulator;pipelined sampling;opamp sharing

夏 雨(1990-),女,天津大学硕士研究生,主要从事模拟集成电路的设计;

姚素英(1947-),女,教授,博士生导师。天津大学微电子学与固体电子学国家重点学科学术带头人,享受国务院政府特殊津贴专家;

徐江涛(1979-),男,副教授,硕士生导师,主要从事CMOS图像传感器和图像处理芯片研究,在相关领域主持国家自然科学基金、教育部博士点基金等项目;

聂凯明(1986-),男,博士后,主要从事CMOS图像传感器芯片研究。

项目来源:国家自然科学基金项目(61036004);天津市应用基础与前沿技术研究计划项目(13JCQNJC00600)

2014-11-04 修改日期:2014-12-11

C:7230

10.3969/j.issn.1004-1699.2015.03.013

TN366

A

1004-1699(2015)03-0367-07