C*Core芯片SCI串口波特率容限优化

张传演,卓秀然,孟召伟,钱 丹,李红斌,蔡 伟

(1.中国人民解放军73022部队 浙江 杭州 310024;2.福建省气象服务中心 福建 福州 350001)

串口(SCI)是微控制器(MCU)与外围设备等进行异步串行通信的接口[1]。C*Core系列芯片中含2个相同且独立SCI,采用异步方式传送数据,但数据接受/发送速率 (波特率)统一,SCI模块中有一个波特率发生器,产生波特率时钟。

SCI接受器与发生器利用波特率发生器设定速率,但设定值与实际值之间具有误差,称为容限误差。一定范围的容限值,不影响SCI数据传输的正确性。但随着波特率、芯片主频大小变化,容限值会超出允许误差范围,造成SCI传输和接受的数据不匹配现象。确定设定波特率、主频与波特率容限值之间关系,研究与解决传输与接受双方数据不匹配问题成为C*Core芯片工程应用中十分重要的工作。

1 C*Core芯片SCI波特率容限问题

1.1 SCI波特率的发生

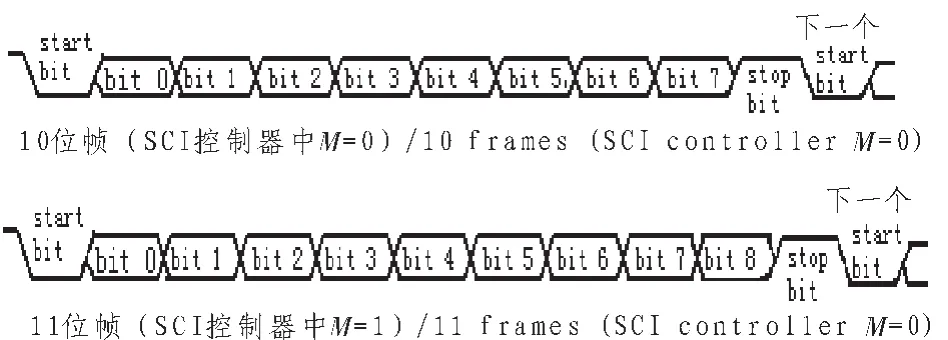

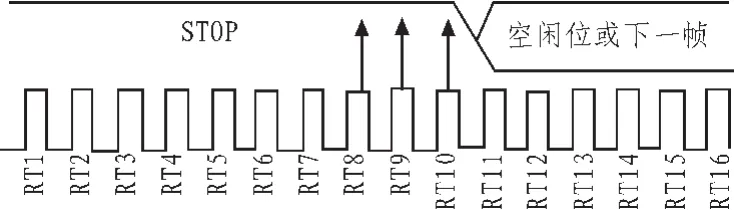

SCI使用标准的异步串行传送数据格式发送和接受串行数据[2],串行数据格式如图1所示,图中含两种帧,分别为10位和11位,帧的传输种类由SCI控制寄存器中的M位决定:M=1,帧长 11 位;M=0,帧长 10 位。

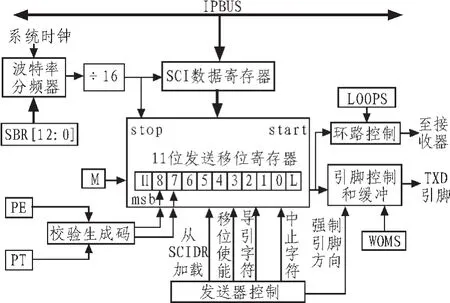

SCI异步传送帧数据时,要求SCI对方按统一波特率接受/发送数据,确保数据传输速率相等。为了统一波特率,SCI发送器及接收器中都含有一个波特率发生器如图2所示。

图1 SCI数据格式Fig.1 SCI data format

图2 SCI发送器框图Fig.2 SCI transmitter block diagram

波特率发生器是一个13位的分频器,由波特率寄存器(SCIBD)设置分频因子(SBR[12:0])对系统时钟分频[3]。 SCI波特率可由式(1)计算得出:

通过上式可知,波特率发生器输出的时钟经16分频后得到发送时钟,但可直接作为接受器时钟。SCI发送与接受端通过编程SBR[12:0]统一波特率。

1.2 SCI波特率容限

分频因子SBR[12:0]由下列公式确定:SCI标准波特率被系统固定,如:4 800、9 600、115 200等。设定好分频因子后,再由式(1)得SCI波特率。在C*Core芯片中,数据格式不支持浮点数,SCI波特率与分频因子SBR[12:0]都只为整数,公式计算过程中产生的小数被规整,进而产生规整误差,两次规整累积误差导致接受端与发送端波特率之间误差。例如,设系统时钟40 M,标准波特率115 200位/秒,则 SBR[12:0]=21,SCI波特率计算值为:119 047,与标准波特率115 200相差3.3%。SCI容限误差可分为两种情况。

1.2.1 慢数据的容限

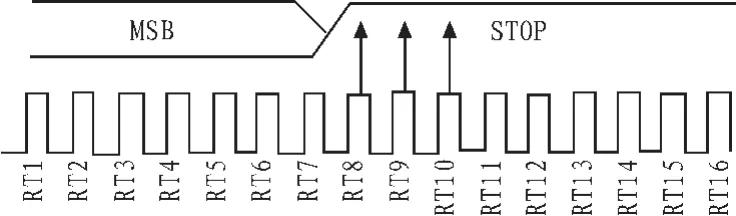

对于被接受数据的位速率慢于接收器波特率的情况,图3显示了在不发生噪声错误和帧错前提下,被接收数据最慢情况[4]。RT为数据采样点。

图3 慢数据和快接收波特率的情况Fig.3 Slow and fast data baud rate

对于M=0,帧长度为10位,接收器完成停止位采样花费的时间为:

9位×16RT周期/位+10RT周期=154RT周期

而在此时间点上发送设备RT计数数值为:

9位×16RT周期/位+3RT周期=147RT周期

在不出现错误的情况下接收器和发送方之间波特率相差的最大百分比为:

对于M=1,帧长度为11,接收器完成停止位采样花费的时间为:

10位×16RT周期/位+10RT周期=170RT周期

而在此时间点上发送设备对自己的RT计数数值为:

10位×16RT周期/位+3RT周期=163RT周期

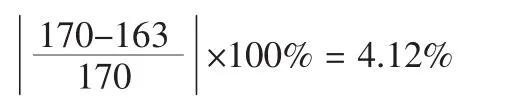

令这两个时间相等,可推出,在不出现错误的情况下接收器和发送方之间波特率相差的最大百分比为:

1.2.2 快数据的容限

对于被接受数据的位速率快于接收器波特率的情况,图4显示了在不发生噪声错误和帧错前提下,被接受数据最快情况。

图4 快数据和慢接受波特率的情况Fig.4 Fast and slow data baud rate

对于M=0,帧长度为10位,接收器完成停止位采样花费的时间为:

9位×16RT周期/位+10RT周期=154RT周期

而在此时间点上发送设备对自己的RT计数数值为:

10位×16RT周期/位=160RT周期

在不出现错误的情况下接收器和发送方之间波特率相差的最大百分比为:

对于M=1,帧长度为11同理可推出,波特率相差的最大百分比为:

1.3 C*Core芯片SCI波特率容限分析

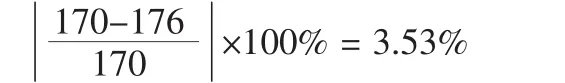

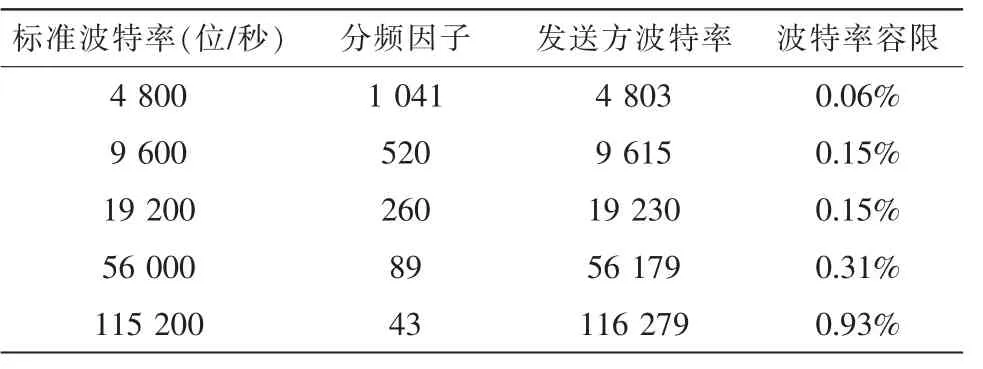

由波特率计算公式可推出各主频下不同标准波特率对应的发送器与接受器波特率容限误差最大百分比。表1为fsys=5 M时,选取的5种标准波特率对应的波特率容限。其中分频因子由式(2)计算得出,发送方波特率由式1得出。

表1 fsys=5 M各波特率容限Tab.1 fsys=5 M baud rate tolerance

由表知在标准波特率为56 000和115 200时,波特率容限分别达到了11.6%和35.6%超过波特率容限允许值,传输时会出现数据不匹配现象,发送8个八位数据,只接收到7个八位数据,实验现象如图5所示。图中左边为波特率设置等。

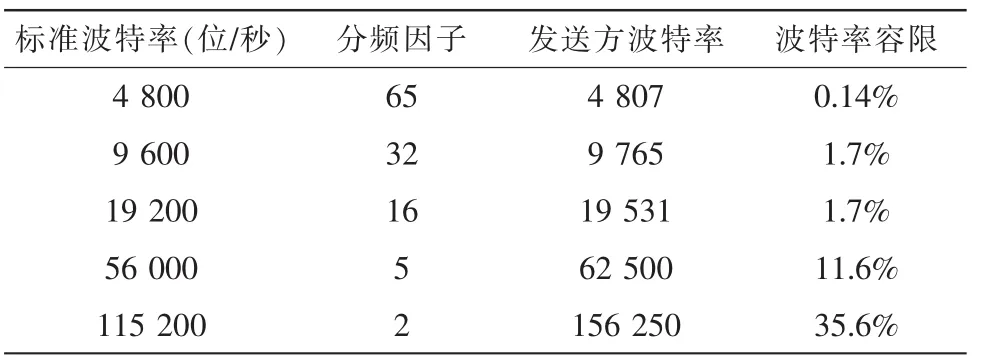

图5中发送端波特率统一设为115 200,接收端由于容限误差过大造成丢帧现象,丢失率:12.5%,在波特率为56 000时,同样出现了丢帧现象。表2为fsys=20 M时,选取的5种标准波特率对应的波特率容限。

波特率为115 200时,容限达到了8.5%超过最大允许波特率容限,实际传输时经检测出现误帧现象,现象如图6所示。

图 7 中,发送器发送固定数组 a[4]={0x00,0xfe,0xea,0x32},接收器所获数据不符,出现了误帧现象。

表3显示主频为80 M时,5种标准波特率对应的波特率容限。

表2 fsys=20 M各波特率容限Tab.2 fsys=20 M baud rate tolerance

图6 串口接收数据显示Fig.6 Serial port to receive data in table

表3 fsys=80 M各波特率容限Tab.3 fsys=80 M baud rate tolerance

对比以上4表,可发现容限值随主频与标准波特率变化而变化,主频越小、标准波特率越大可促使容限值增大。当主频高于一定值时,即使标准波特率设置较大,容限值依然较小。例如fsys=80 M时,波特率为115 200,容限值较小。

2 C*Core芯片SCI波特率容限优化

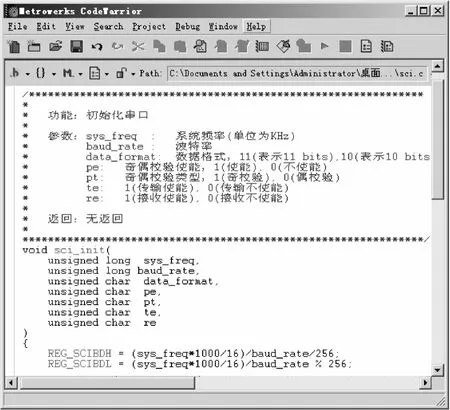

C*Core模块容限误差主要来自小数规整误差。优化的核心是减少此误差。图7显示了SCI模块串口初始化部分配置程序,作用是通过设置的标准波特率计算分频因子[5]。

图7 串口初始化分频因子计算Fig.7 Serial frequency factor calculated initialization

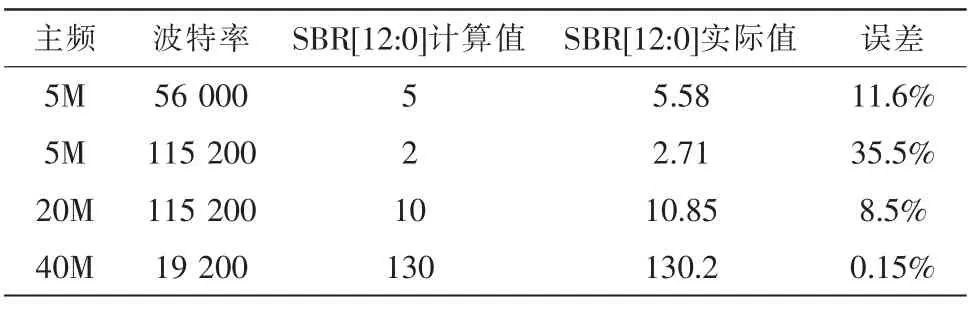

分频因子SBR[12:0]为13位,计算时需分别计算高5位REG_SCIBDH[4:0]和低八位 REG_SCIBDL[7:0][6]。表 4 为运行初始化程序后,计算分频因子值与实际值对比。

表4 分频因子与实际值对比Tab.4 Frequency factor compared with the actual value

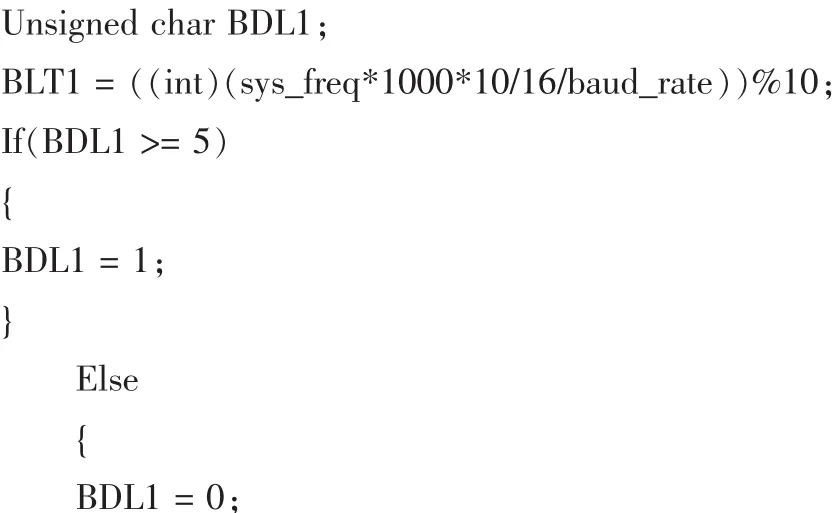

通过上表可知,分频因子实际值小数被向下规整,导致小数部分向下规整误差较大,其他频率下不同标准波特率的各计算值类似。优化算法的核心思想是在计算分频因子的过程中,实现分频因子小数正确规整,缩小分频因子的计算值与实际值误差,达到正常误差范围。在图7基础之上,下列显示了串口初始化程序分频因子计算优化程序。

优化程序中定义了临时变量BDL1,首先判断SBR[12:0]实际值小数部分是否大于0.5,若大于BDL1赋值为1加到SBR[12:0]低八位上,完成进 1 功能;反之,BDL1 赋值为 0,不操作,完成舍四功能。

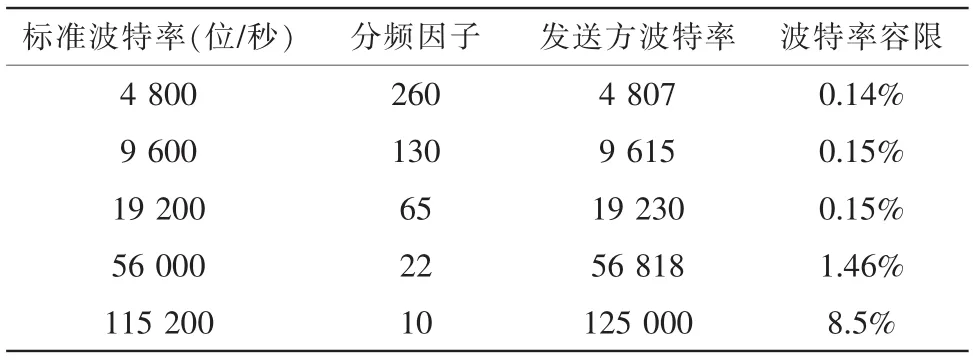

表5为运行优化后的串口初始程序后,计算分频因子值与实际值对比。

表5 优化后分频因子与实际值对比Tab.5 Optimized frequency factor compared with the actual value

对比表5与表4,分频因子的误差被显著减小,这促使C*Core芯片中SCI模块容限误差显著减小。表6列举若干优化前后波特率误差对比情况。

表6 优化前后波特率容限对比Tab.6 Baud rate tolerance compared before and after optimization

优化后的容限不影响发送方与接受器之间数据的传输准确性。 在实验过程中,发送数组 a[0:4]={0x00,0xfe,0xea,0x32},主频 20M,标准波特率为 115 200位/秒 ,利用 SCI串口连续发送了4组共16字节的数据给接收端,没有发现丢帧、误帧现象。此外,SCI模块进行了3 200组每组1.1 M随机数采集实验,整个过程中没有出现丢帧和误帧现象。

3 结束语

文中研究C*Core芯片中SCI模块发送器与接受器之间波特率误差即波特率容限问题。通过分析与总结芯片频率、标准波特率与波特率容限误差规律,设计了优化串口初始化程序优化程序。通过大量数据实验证明,优化后的串口初始化程序运行后,发送端与接受端数据传输没有出现任何丢帧与误帧现象。此外,此优化程序也适应于不支持浮点计算的嵌入式芯片。

[1]王宜怀,刘晓升.嵌入式应用基础基础教程[M].北京:清华大学出版社,2005.

[2]马鸣锦,蒋烈辉,杜威,等.基于M*CORE微控制器的嵌入式系统[M].北京:国防工业出版版社,2003.

[3]王宜怀,朱巧明,郑茳.C*Core与M*Core的嵌入式系统[M].北京:清华大学出版社,2006.

[4]苏州国芯科技有限公司.CCM3118DQ Advance Information Rev[R].苏州:国芯公司,2003.

[5]Metrowerks CodeWarriorIDE UserGuide [EB/OL].2000[2010-11-20].http://read.pudn.com/downloads14/ebook/55460/ADS_CodeWarrior_IDEGuide.pdf.

[6]Motorola.MMC2107 Technical Data MMC2107/DRev.2[EB/OL].Seattle:Motorola inc,2000[2011-9-2].http://www.motorolasolutions.com/CN-ZH/Home.