基于锁相环的正弦信号发生器设计

陈帅锋,侯晓伟

(1.中国平煤神马集团 中南矿用产品检测检验有限公司,河南 平顶山 467000;2.西北工业大学 电子信息学院,陕西 西安 710072)

正弦信号发生器是电子实验室常用的设备,其频率和振幅稳定性是关键的性能指标,其中尤以频率的准确性和稳定性最为重要[1-2]。

目前,广泛使用的是标准产品,但能够用数控方式进行频率设定、间隔步进和稳频输出的很少,且价格昂贵。所以,研究低成本、小体积、便携式的正弦信号发生器具有一定的实际意义,可广泛地应用于检测、实验室研究、通信等领域[3]。

信号发生器的核心技术是频率合成技术,主要方法有:直接模拟频率合成、锁相环频率合成(PLL)、直接数字合成(DDS)[3-4]。 模拟频率直接合成的信号发生器电路复杂,缺乏灵活性、稳定性较低[5-6];PLL技术比较成熟,具有频率稳定度高、准确性好、价格低等特点,但输出信号频率只能以间隔步进调整[7-9];DDS是开环系统,无反馈环节,其合成频率的时间快,频率稳定度高,但电路复杂、成本高[4]。基于此,文中设计了一种基于锁相环的正弦信号发生器。

1 系统结构

该正弦信号发生器主要有以下几个模块组成:RC正弦波振荡器、整形电路、R分频电路、锁相环(包括鉴相器、环路滤波器、压控振荡器、可变分频器)和输出匹配电路。总体图如图1所示。

图1 正弦信号发生器组成框图Fig.1 Schematic of sine-wave generator

该设计是用较为简单的RC正弦波振荡器产生所要求的正弦波,用整形电路进行适当整形,再用R分频电路给出符合要求的一定频率的信号送入锁相环。锁相环是用ADI公司生产的ADF4106芯片及外围电路组成的。从锁相环出来的信号再经过匹配输出电路的整形、滤波等操作,实现最终的信号要求。

2 主要电路设计

2.1 RC正弦波振荡器

如图2所示,采用的RC正弦波振荡器是线性电子电路课程中使用的较为普遍的一个电路。它由LM741放大器、滑动变阻器、电阻、电容等基本元件构成。

2.2 整形电路

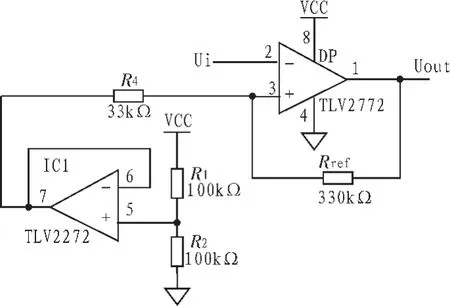

该设计是用两个运放TLV2272和TLV2772和一些电阻所构成的单电源施密特触发器整形电路,如图3所示。

图2 RC正弦波振荡器Fig.2 Oscillator of RC sine-wave

图3 单电源施密特触发器整形电路Fig.3 Schmitt toggle shaping circuit of single powe

2.3 R分频电路

如图4所示,R分频电路使是用555定时器构成的的任意分频电路,分频系数R可以达到10以上。这里555定时器以一个单稳电路,单稳延迟时间为:

Td≈1.1R2C2。假设输入频率 fin的周期为 T,要求作R分频的话,那么 Td应满足:(R-1)T<Td<RT。 要获得所需要的频率,可以选择合适的Td、R2、C2值,实现所需要的输出频率。

图4 555定时器构成的任意R分频电路Fig.4 Arbitrary R frequency dividing circuit consist of 555 timer

2.4 锁相环电路

锁相的意义是相位同步的自动控制,能够完成两个电信号相位同步的自动控制闭环系统叫做锁相环,简称PLL。它广泛应用于广播通信、频率合成、自动控制及时钟同步等技术领域。锁相环主要由相位比较器(PD)、低通滤波器(LF)、压控振荡器(VCO)3部分组成,如图5所示。

压控振荡器的输出Uo接至相位比较器的一个输入端,其输出频率的高低由低通滤波器上建立起来的平均电压Ud大小决定。施加于相位比较器另一个输入端的外部输入信号Ui与来自压控振荡器的输出信号Uo相比较,比较结果产生的误差输出电压UΨ正比于Ui和Uo两个信号的相位差,经过低通滤波器滤除高频分量后,得到一个平均值电压Ud。这个平均值电压Ud朝着减小VCO输出频率和输入频率之差的方向变化,直至VCO输出频率和输入信号频率获得一致。这时两个信号的频率相同,两相位差保持恒定(即同步)称作相位相定。

图5 锁相环组成框图Fig.5 Schematic of phase-loop lock

当锁相环入锁时,它还具有“捕捉”信号的能力,VCO可在某一范围内自动跟踪输入信号的变化,如果输入信号频率在锁相环的捕捉范围内发生变化,锁相环能捕捉到输人信号频率,并强迫VCO锁定在这个频率上。锁相环应用非常灵活,如果输入信号频率f1不等于VCO输出信号频率f2,而要求两者保持一定的关系,例如比例关系或差值关系,则可以在外部加入一个运算器,以满足不同工作的需要。 过去的锁相环多采用分立元件和模拟电路构成,现在常使用集成电路的锁相环。

2.4.1 鉴相器的选择

鉴相器是这一种电路,它的输出信号与两个输入信号的相位差成比例。很多种结构的电路都可以完成这种功能。在混合信号锁相环系统中,主要使用4种鉴相器:乘法鉴相器、EXOR鉴相器、JK触发型鉴相器和鉴频/鉴相器。

乘法鉴相器广泛应用于线性锁相环(LPLL)中。在锁相环处于锁定状态时,鉴相器可以表示为一个增益为Kd的零阶模块。EXOR鉴相器的工作原理与线性乘法器类似。DPLL数字锁相环的信号都是二进制信号,例如方波,宜于采用EXOR鉴相器。JK触发型鉴相器:这种类型的JK触发器不同于传统的JK触发器,因为它是边沿触发的。鉴频/鉴相器(PFD):PFD与前面所述的鉴相器有很大不同,它的输出信号不仅与相位误差有关,而且在未达到捕获状态时还与频率误差有关。由于PFD的输出信号在锁相环处于锁定状态时与相位误差有关,在未锁定状态时与频率误差有关,因此,带有PFD的锁相环在任何条件下都能够获得锁定,不管使用什么类型的环路滤波器。基于这个原因,在该设计中,采用PFD作为鉴相器。

2.4.2 环路滤波器的选择

鉴相器的输出信号包含很多分量,在锁相环处于锁定状态时,这些分量的第一项为“直流”分量,而且近似与相位误差成比例,这是所需要的信号分量;剩下的分量都是些高频分量,是多余分量,必须被环路滤波器滤除。由于环路滤波器必须让低频分量通过而抑制高频分量,因此它必须是一个低通滤波器,因此锁相环的滤波器又称为环路低通滤波器。

无源与有源的选择:有源滤波器因为采用放大器而引入噪声,所以采用有源滤波器的PLL产生的相位噪声性能会比采用无源滤波器的PLL输出差,因此在设计中尽量采用无源滤波器。另外,所设计的环路滤波器的带宽不能很大(例如200 Hz),否则构成滤波器的电容会很大,电阻会很小。通常情况下,环路的带宽设置为鉴相频率的1/10或1/20。本设计采用三阶无源滤波器。

2.4.3 受控振荡器的选择

受控振荡器有两种类型:电压控制振荡器(VCO)和电流控制振荡器(CCO)。它们的不同在于,前者输入(控制)信号为电压信号,后者输入(控制)信号为电流。该设计选择VCO。在选择VCO时,尽量选择VCO的输出频率对应的控制电压在可用调谐电压范围的中点。选用低控制电压的VCO可简化PLL设计。在设计锁相环系统时,必须确定VCO的两个参数:中心频率和VCO增益,在实际的VCO电路中,这些参数通过外部元件,如电阻、电容来设置。

2.4.4 分频器的设置

该设计中需要使用分频器来进行分频,以实现所需要的频率。分频器通常由触发器(如RS触发器、JK触发器或是T触发器)级联而成。一个JK触发器可以将加到它的时钟输入端的信号2分频,两个就是4分频,等等。任意值的分频因子(例如分频因子不是2的幂函数)可以通过在计数电路中增加门电路来实现。

2.5 匹配输出电路

在匹配输出电路端,需连接上一个放大器和一个阻抗匹配电路,这样输出信号可以被有效地放大、匹配,易于观察。

3 仿真及输出结果

3.1 RC正弦波振荡器仿真

如图6所示,它使用基于Hspice CMOS电路模拟与设计软件Hspice2003,通过设置RC正弦滤波器电路的电阻电容等参数,所得到的其中的一组仿真波形。

3.2 锁相环仿真

图6 Hspice所产生的两组RC正弦波振荡器仿真波形Fig.6 Two groups of RC sine-wave simulation waveform produced by Hspice

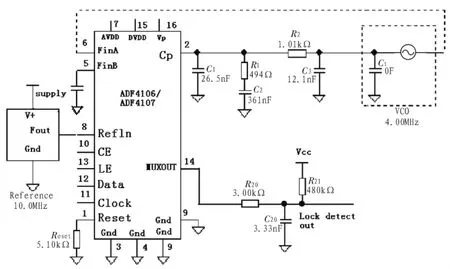

锁相环仿真是采用ADI公司开发的ADIsimPLL软件进行的。ADI所开发的ADF系列锁相环产品所能综合的频率可达8 GHz,几乎可以涵盖目前所有无线通信系统的频段。仿真所采用的芯片为ADF4106/ADF4107,它集鉴相器及分频器双重功能于一身。整个锁相环系统仿真框图还包括参考频率源、三阶无源环路滤波器、压控振荡器和锁定检测输出等部分组成,如图7所示。

仿真条件:1)系统级:最大最小频率分别为 10 MHz和20 MHz,通道间隔为 25 kHz,鉴相器频率为 25 kHz,设计频率为 14.142 14 MHz;2)参考频率为 10 MHz;3)VCO:调整规则(tuning law)为两点法,它是压控振荡器控制电压与输出频率的关系规律,两点法是良好的线性关系规则;4)采用芯片为ADF4106,主要分频器分频系数为8,最大频率为6 GHz;参考分频器最大频率为300 MHz,鉴相器工作形式为电荷泵方式,重置频率为5.1 kHz(最小频率为3 kHz,最大频率为11 kHz);5)环路滤波器:采用的是三阶无源环路滤波器,特殊性能为相位裕度,环路带宽为2.5 kHz,相位裕度为45degree,C1、C2、C3值 分 别 为 26.5 nF、361 nF、12.1 nF,R1、R2分别为 494 Ω、1.01 kΩ;6)锁定检测电路:R20、R21分别为 3 kΩ、480 kΩ,C20为 3.33 nF,Vcc 为 3 V;7)频域:最小与最大频率10 Hz与 1 MHz,分析点频率是 14.15 MHz;8)时域:采用的分析方法为频率改变法(前提是环路锁定在开始频率,且t=0,结束在截止频率上),开始频率为10 MHz,截止时间为2.30 ms,最大时间步长为2 μs。以下分别为频域、时域的仿真结果。

3.2.1 频域仿真

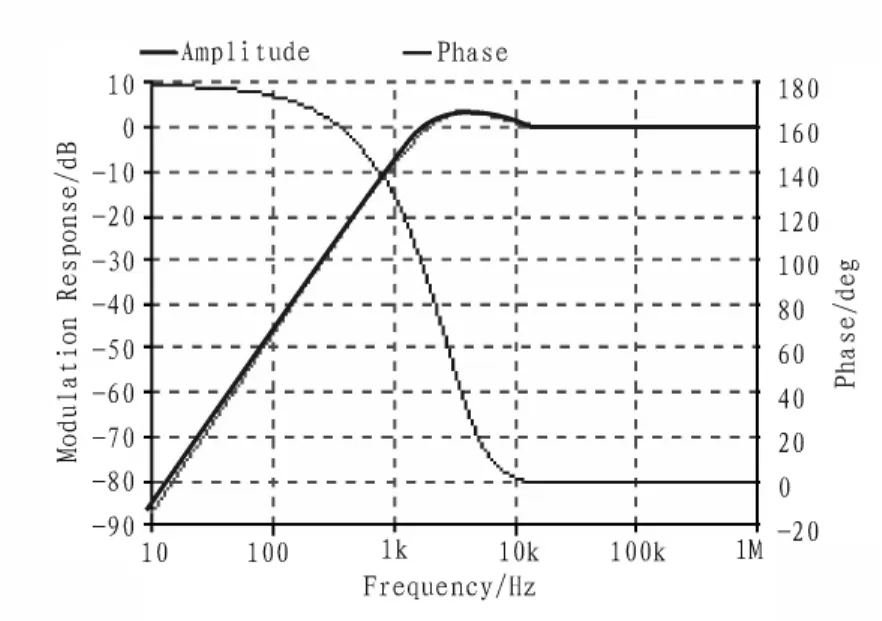

图8~图11分别表示在频域仿真条件下,该锁相环在14.1 MHz时的开环增益、闭环增益、相位噪声和频率调制响应。

3.2.2 时域仿真

图7 芯片ADF4106及外围电路组成的锁相环仿真框图Fig.7 simulation schematic consist of chip ADF4160 and peripheral circuits

图8 在14.1 MHz时的开环增益Fig.8 Open-loop gain at 14.1 MHz

图9 在14.1 MHz时的闭环增Fig.9 Closed-loop gain at 14.1 MHz

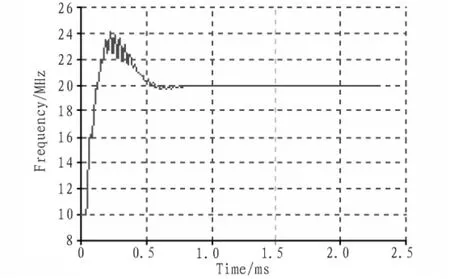

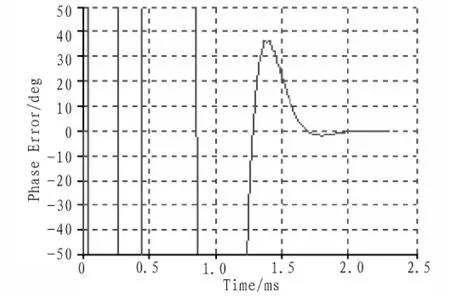

图12~图15分别表示在时域仿真条件下,该锁相环随时间变化的频率变化、输出相位误差、频率误差的绝对值以及锁定检测输出电压。

4 实验结果分析

图10 在14.1 MHz时的相位噪声Fig.10 Phase noise at 14.1 MHz

图11 在14.1MHz的频率调制响应Fig.11 Frequency modulation response at 14.1 MHz

由RC正弦波振荡器输出的正弦波信号,经过整形后可以满足该设计的要求,再经过R分频器分频电路进行分频(分频系数可达10以上),可获得一定范围内的符合要求的信号。锁相环中环路滤波器的设计前提是:VCO的频率为14.142 MHz,Kv为4.00 MHz/V;锁相环的频域仿真是在输出频率为14.15 MHz的条件下进行的;对于相位抖动可采用10~100 kHz的矩形滤波器进行滤波,其相位抖动为0.00degree rms;通道中心频率为 25 kHz,载波频率为 15.0 kHz,功率为-91.4 dBc;锁相环的瞬态分析:频率变化范围为10~20 MHz,仿真时间为2.30 ms;频率锁定:锁定到1 kHz的时间是1.32 ms,锁定到10 Hz的时间是2.06 ms,;相位锁定 (VCO输出相位):锁定到10.0degree的时间是 1.57 ms,锁定到 1degree的时间为1.92 ms,这些说明了该锁相环可以迅速的锁定信号的频率和相位,满足信号发生器稳定性的要求。

图12 随时间变化的频率变化Fig.12 Frequency varying with the time

图13 随时间变化的输出相位误差Fig.13 Output phase error varying with the time

图14 随时间变化的频率误差的绝对值Fig.14 Absolute value of frequenc error varying with the time

图15 随时间变化的锁定检测输出电压Fig.15 Output voltage of lock detector varying with the time

5 结束语

文中设计了一个基于锁相环的正弦信号发生器,包括RC正弦波振荡器、整形电路、分频电路、锁相环、匹配输出电路等部分,给出了较为具体的各模块框图以及仿真结果,并进行了分析。证明了所设计的正弦信号发生器在适用范围、灵敏度、稳定性等指标方面,可以较好的满足要求,扩展了锁相环的应用领域,是一种积极的探索。

[1]Roland E.Best.锁相环设计、仿真与应用[M].李永明,等译.5版.北京:清华大学出版社,2007.

[2]Floyd M.Gardner.锁相环技术 [M].姚剑清,等译.3版.北京:人民邮电出版社,2007.

[3]刘平,来新泉,楼顺天,等.基于锁相环的低频函数发生器[J].电子设计工程,2007(12):36-39.

LIU Ping,LAI Xin-quan,LOU Shun-tian,et al.Low frequency function generator based on phase-locked loop[J].Electronic Design Engineering,2007(12):36-39.

[4]陈鹏.基于DDS的波形发生器设计[J].现代电子技术,2009(9):103-105.CHEN Peng.Design of waveform generator based on the DDS[J].Modern Electronics Technique,2009(9):103-105.

[5]乐翔,秦士,钱强.基于锁相环的调频脉冲发生器[J].清华大学学报:自然科学版,1997,37(10):34-36.

LE Xiang,QIN Shi,QIAN Qiang.Frequency modulation pulse generatorbasedonthephase-lockedloop[J].JournalofTsinghua University:Science and Technology,1997,37(10):34-36.

[6]李伟,高志红.基于锁相环的高稳定高频正弦信号发生器[J].测试技术学报,2005,19(1):75-78.

LI Wei,GAO Zhi-hong.High stability of high frequency sine-wave generator based on phase-locked loop[J].Journal

of Test and Measurement Technology,2005,19(1):75-78.

[7]陈蜀勇.基于PLL的信号发生器的实现[J].微计算机信息,2004,20(11):98-99.

CHEN Shu-yong.An realization for signal generator based on PLL[J].Control and Automation Publication Group,2004, 20(11):98-99.

[8]彭进忠,王军成,莫亭亭,等.基于小数分频的锁相环设计[J].电子与封装,2008,8(9):15-18.

PENG Jin-zhong,WANG Jun-cheng,MO Ting-ting,et al.Fraction-Nphase-locked loop design[J].Electronics&Packaging,2008,8(9):15-18.

[9]张坤,陈义,张子才.基于锁相环的频率合成器的设计[J].现代电子技术,2009(19):110-112.

ZHANG Kun,CHEN Yi,ZHANG Zi-cai.Design of frequency synthesizer based on PLL[J].Modern Electronics Technique,2009(19):110-112.