基于NiosⅡ软核处理器的图像数据缓存系统的设计

孟令军,李鹏飞,安航行,赵 林

(中北大学电子测试技术国家重点实验室仪器科学与动态测试教育部重点实验室,山西 太原 030051)

责任编辑:魏雨博

基于遥测系统的蓬勃发展,尤其是在图像遥测方面的深入研究,当今已经实现了在多个领域的发展与应用。本文设计了一种由全硬件FPGA实现的图像采集系统,以FPGA卓越的并行处理能力为依托,对系统关键模块进行合理的设计,将大量运算采用并行处理的方式实现,不仅可以大幅提高数据处理度,而且可以极大地提高系统的信息处理能力。同时内嵌的Nios II处理器提高了图像处理速度并精简了系统的体积。因此,广泛深化研究基于Nios II的视频图像处理技术,对开发高成效的视频图像采集系统有着广阔而深远的理论与现实意义。

1 系统原理与基本架构

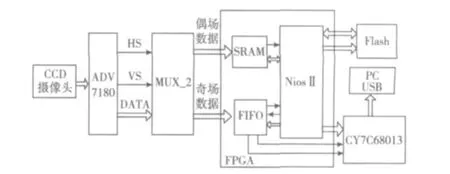

图像采集存储系统的主要功能是完成对单路模拟图像信号的模数转换并对转换后数据进行实时采集、存储,同时系统也可以根据遥测命令将数据通过通信接口上传给PC或者下发给对应的遥测接收设备。系统结构如下图1所示,主要包括4个模块:图像获取模块,主要实现模拟图像的采集,为后端信号转换提供输入;图像信号转换模块(A/D),完成图像信号由模拟到数字的转换、图像信号与其它信号的分离、视频信号的格式转换等,为后端提供可以处理的数字信号;图像数据处理模块,接收前一模块的数字图像信号,对数据进行计算、存储和各种处理等,一般数据接收可以采用单片机、DSP等实现,本文采用FPGA实现;通信模块,实现系统与外界的数据和命令交互,有多种工业接口可以选择。如图1所示,简明地表示出了系统内各模块的关系。

图1 系统结构流程图

2 基于NiosⅡ的嵌入式处理器设计

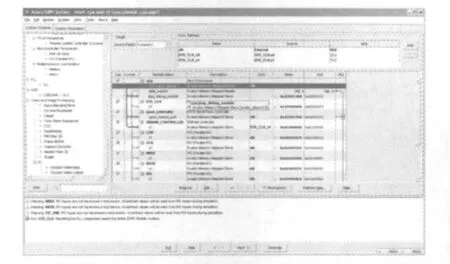

SOPC系统的开发流程主要从硬件开发和软件开发两个方面来进行。硬件开发的主要目的是使用SOPC Builder搭建Nios II系统,然后在Quartos II中经过逻辑综合、布局布线生产硬件结构,它将处理器、存储器、I/O接口等系统设计的功能模块集成到一个PLD上,构成一个可编程的SoC(片上系统);根据设计的需求来开发软件,在Nios II IDE环境中利用C/C++语言和系统自带的API函数编写实现功能的程序,系统软件程序主要在Nios II IDE环境中编写C语言程序实现,主要目的是给VHDL硬件模块提供模块启动、结束等信号,同时进行一些模块的配置和时钟控制,使各模块都能正常工作,最后将硬件与软件一起下载到硬件进行联合调试来验证设计,如图2所示。

图2 构建嵌入式处理器模块(截图)

3 I2C总线的设计

IIC(Inter-Integrated Circuit)或I2C即集成电路总线,是PHILIPS公司开发的两线式串行总线,主要是用来连接整体电路(ICS)或微控制器及其外围设备。它由可同时发送、接收数据的串行总线:数据线SDA和时钟SCL构成。所有接到I2C总线设备上的串行数据SDA都接到总线的SDA上,各设备的时钟线SCL接到总线的SCL上。I2C总线上允许连接多个微处理器以及各种外围设备,如存储器、LED及LCD驱动器、A/D及D/A转换器等,串行的8位双向数据传输位速率在标准模式下可达100 kbit/s快速模式下可达400 kbit/s高速模式下可达4 Mbit/s。它在传送数据过程中共有3种类型信号:开始信号、结束信号和应答信号。在I2C总线传输过程中,将两种特定的情况定义为开始和停止条件(如图3所示):当SCL保持“高”时,SDA由“高”变为“低”为开始条件;当SCL保持“高”且SDA由“低”变为“高”时为停止条件。开始和停止条件均由主控制器产生。

图3 I2C数据传输图

在硬件开发时,需要在软核中添加2个IO模块(如图4),并将其命名为 SCL和 SDA,其中,SCL为output ports only(仅输出),SDA 为 Bidirection(tristate)port(双向),建好以后,如图4所示。

图4 SOPC中构建I/O模块

4 视频处理芯片ADV7180

在系统设计中,采用了可以实现模拟图像信号到数字图像信号转换的是ADI公司推出的一款10位、4倍过采样的视频图像解码器ADV7180,它可实现对多格式模拟视频信号采样分析。ADV7180接口设计极为简单,只需要通过设计简单的数字输出接口ADV7180便可以与各种编解码器、移动视频处理器及ADI公司的数字图像压缩芯片(如ADV212等)实现无缝连接。同时,与其数据同步输出的HS、VS、数据时钟和FIELD信号也可为LCD控制器和其它视频解码芯片提供时序基准,扩展非常方便。由于在设计中不对其寄存器进行读数操作只进行写配置操作,所以,在设计中将其ALSB管脚直接接地。在系统中ADV7180是挂载在I2C总线上的I2C从设备,总线通过从设备地址识别ADV7180进而完成对其进行配置。解码器ADV7180要实现正常转换功能必须与I2C总线的正确配置。系统控制核心Nios II软核在获取启动信号后启动I2C控制器完成芯片配置,启动芯片开始工作。正确配置后启动ADV7180可以自动检测输入的视频信号制式,并将相应的模拟信号转换成对应数字信号输出来,关键处理如何正确配置ADV7180中各寄存器。

5 USB通信模块

根据设计时提出的要求,既要实现设备控制,又要完成高速数据传输,为了满足需要选用了Cypress公司的EZUSB FX2接口芯片CY7C68013。它采用通用可编程接口(GPIF)方式通过FPGA与Flash进行数据操作。数据的读取通过GPIF口来实现,命令的下发通过PE口来实现。PE口是单一功能口,只要在固件架构中的初始化程序中将PE口使能为输出口,在主程序中接收通过上位机下发的命令,然后通过PE口将相应命令值输出,Flash控制器根据接收到的PE口的不同命令对Flash进行不同的操作。GPIF是一个对于FX2端点FIFO的内部主控制器,它代替了外部的“胶合”逻辑电路,在整个数据读取过程中,为了匹配USB2.0于FPGA内部Flash控制器之间的数据传输,硬件扩展了16 kbyte的硬FIFO(IDT7206)来匹配读数时序来完成Flash数据的读取。

6 系统调试结果及分析

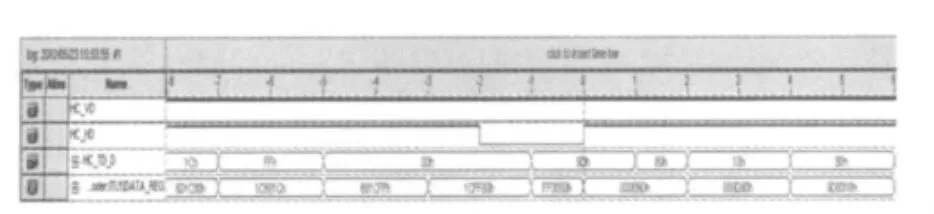

通过Quartus II下的嵌入式逻辑分析仪SignalTap II Logic Analyzer对图像数据上传进行了实时采样的时序分析,图5是8位图像数据和PIC_Decoder模块中数据寄存器DATA_REG关系图。经过上位机软件还原数据后,得到的图片信息清晰无误码率,达到了预设的效果,可进一步完善用于实际应用。

图5 SignalTap处理后的逻辑图(截图)

[1]凌六一,伍龙.基于软件模拟的51单片机IIC总线的实现[J].电子技术,2004(05):13-15.

[2]祝长锋.肖铁军.基于FPGA的视频图像采集系统的设计[J].计算机工程与设计,2008,9(17):4404-4406.

[3]陈国柱,刘涛,李元宗.基于FPGA的图像采集与存储系统的设计[J].机械工程与自动化,2007,8(4):44-45.

[4]张国兵,孟令军,李宝刚.CCD相机高速数据存储系统中的无缝缓存技术[J].水电能源科技,2010,2(2):70-71.