IPMI 在VPX 系统中的应用与设计

朱红育 李 郁 付学斌

(西安电子工程研究所 西安 710100)

0 引言

随着工业控制、信号处理和国防等领域对总线带宽、传输实时性要求的不断提高,传统的VME、CPCI 等并行总线标准逐渐力不从心,VPX 作为一种基于高速串行总线技术的标准已经悄然兴起。除了引入了目前最新串行总线技术以支持更高的背板带宽外,VPX 还引入了智能平台管理接口(IPMI),用以监控系统的运行状态,提供系统的可靠性。本文对智能平台管理接口IPMI 的功能做了详细的介绍,给出了智能平台管理接口在VPX 系统中的实现方法。

1 智能平台管理接口介绍

IPMI (智能平台管理接口)是一种开放标准的硬件管理接口规格,定义了嵌入式管理子系统进行通信的特定方法。用户可以利用IPMI 监视服务器的物理健康特征,如温度、电压、风扇工作状态、电源状态等。

自诞生以来智能平台管理接口IPMI 已经得到了多家供应商的支持,这使得其逐渐成为了一个完整地包括服务器和其他系统(如存储设备、网络和通信设备)的硬件管理规范,在服务器以及基于ATCA(高级通信计算机架构)的电信设备中的到了广泛的应用[1]。

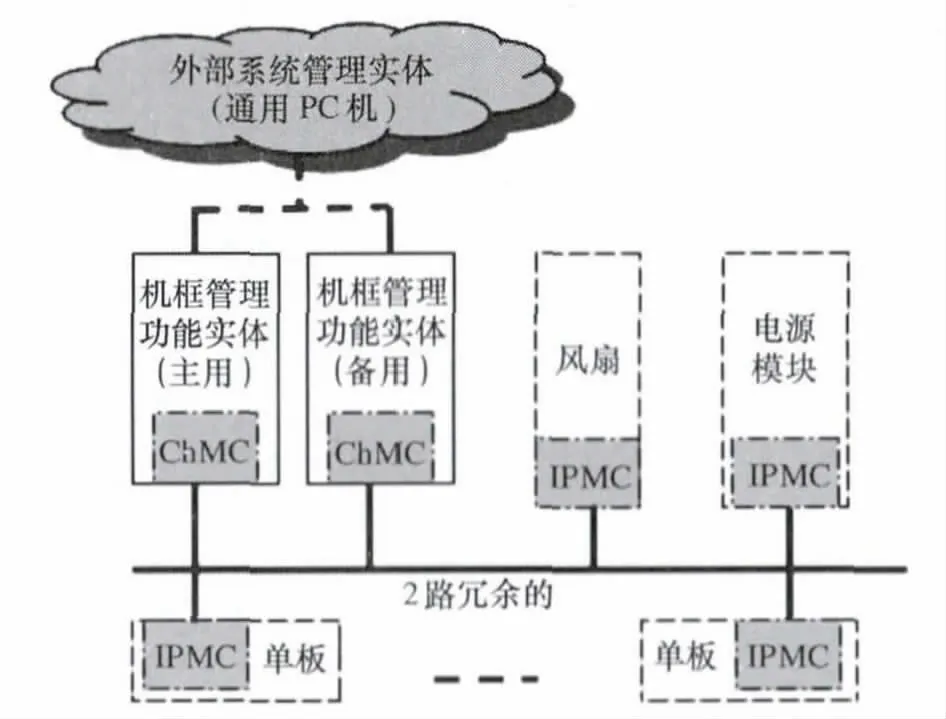

基于IPMI 的智能平台管理系统的主要组件如图1 所示[2]。

a.分布式管理控制器——管理和监控系统中每个FRU(现场可更换单元)的工作状态和故障状态,包括ChMC(机框管理器)和IPMC(板载智能平台管理控制器)。

b.IPMI 其他辅助功能部件——提供在分布式控制单元间以及与系统的总控制单元间的通信、管理和控制功能,如IPMB(智能平台管理总线)接口和IPMI 以太网接口。

c.单板的基于TCP/IP 的高层管理服务,如:远程启动、SNMP(简单网络管理协议)管理、远程磁盘服务和远程管理控制协议(RMCP)[3]。

ChMC 负责系统机框内所有单板的上下电控制、温度和电压监控信息的记录和告警、单板运行状态上报、风冷风扇的转速控制等功能。

IPMC 是FRU 上的管理控制器,主要职责是管理FRU(包括上电、复位、电压温度监控等)、收集FRU 上的关键事件。

IPMC 和ChMC 之间的数据链路是两条IPMB(I2C)总线,采用冗余的双总线乒乓传输架构大大提高了该数据链路的可靠性。

FRU 是现场可更换单元的总称,现场可更换的板卡、冷却风机盘等均可称之为FRU。

图1 IPMI 智能平台管理系统组成框图

IPMI 基本工作原理如下:

IPMI 一般使用独立的电源供电,且先于系统功能电路上电,板载IPMC 上电后,先获取单板位置信息(槽位号),然后通过两条IPMB 总线向ChMC 发送单板信息及上电请求。

ChMC 在对单板信息进行确认后,向各单板依次发送上电命令。

各单板IPMC 接收到上电命令后,控制本板负载进行上电,同时开始监控单板电压、温度并通过专用串行接口从CPU 获取单板工作状态。

当单板电压、温度或工作状态不正常时IPMC发送告警到ChMC。同时响应ChMC 的查询命令,将本板电压、温度及工作状态等信息上报给ChMC。

ChMC 可以通过网络接收来自上位机监控系统的查询请求,并向各单板IPMC 下发温度、电压、工作状态等查询请求,自动向上位机监控系统上报系统告警信息同时记录系统工作日志。

2 IPMI 在VPX 系统中的应用

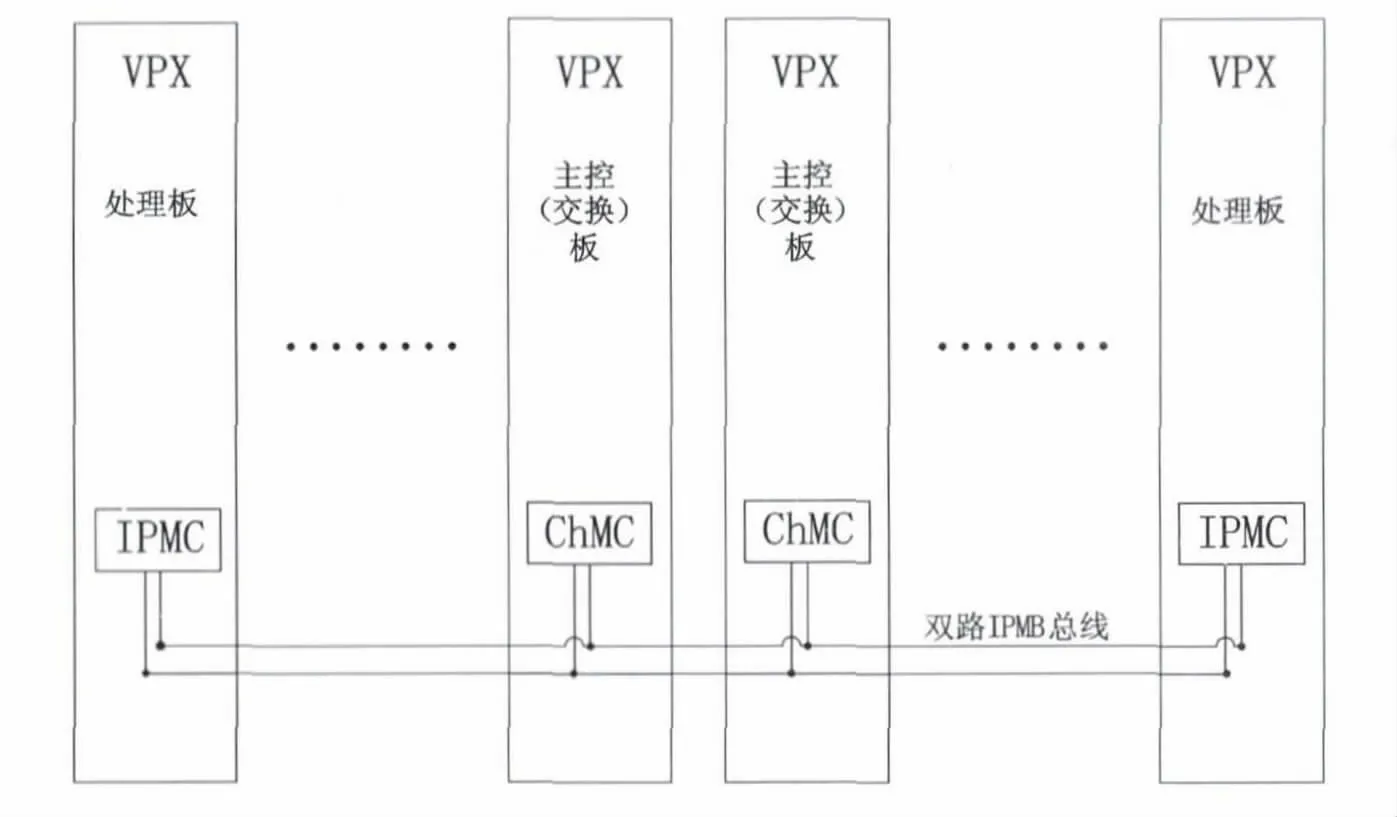

VPX 系统在设计时也引入了IPMI 智能平台管理接口,在P0 端子上预留了SM1——SM4 四个单端信号给两路IPMB 总线使用。

图2 给出了IPMI 在VPX 系统中的应用框图。

图2 IPMI 在VPX 系统中的应用框图

考虑到ChMC 在IPMI 中的重要性,ChMC 设计多采用1 +1 冗余备份机制以提高IPMI 系统的可靠性。两个ChMC 单元上电后通过主备竞争机制确认各自工作状态,同时通过心跳信息相互检测,当发现对端工作异常时向其发送硬复位信号,并自动进行主备切换,确保IPMI 系统能够正常工作。

ChMC 在物理上可以是两块独立的板卡,也可以是系统主控交换板卡上的独立电路(主控交换板卡大都数情况下也采取1 +1 冗余备份的方法提高系统可靠性)。

板载IPMC 是各VPX 单板上的一个独立的电路单元,采用背板3.3V-AUX 进行供电。

2.1 IPMB 总线设计实现

IPMB 总线采用了I2C 通信技术,定义在P0 端子的四个单端信号端子SM1-SM4 上,鉴于I2C 总线的固有特点,虽然采用了冗余的乒乓通信方式,总线锁死的现象仍无法避免,因此设计中需要注意如下方面:

a.总线隔离及热插拔功能实现

依据IPMI 规范,IPMB 总线具有热插拔功能,因此设计选用Linear 公司的LTC4307,该芯片是一颗专用的I2C 双向隔离缓冲器,提供了上升时间加速器从而降低负载过重的总线上升时间,1V 预充电压以降低总线干扰,还具备总线锁死自动检测和恢复功能[4]。

b.总线驱动能力计算

I2C 信号最大的容性负载能力为400pF,因此必须对IPMB 的负载能力进行合理的设计。根据容性负载选择合适的上拉电阻,以保证总线的驱动能力[5]。

对于一个单板来说,容性负载包括以下几个部分:

· 到背板的连接器容性负载:2pF

· 连接器PCB 通孔容性负载:1pF

· 引线和过孔容性负载:9pF

· I2C 驱动器:10pF

此外背板走线的容性负载也需要考虑在内。

在背板上通过计算好的上拉电阻,将IPMB 总线上拉到3.3V-AUX 电源,单板的插拔不会影响到总线的驱动能力。

c.总线锁死预判和处理

I2C 总线的锁死根据原因可分为两种情况,即:从设备未响应导致总线锁死或主设备故障导致总线锁死。

在硬件上每个接入IPMB 总线的节点板卡都设计了LTC4307 隔离缓冲器,当该器件检测SCL 或SDA 信号线保持常低30ms 以上时,会自动将节点板卡从总线上断开,同时向板卡侧发送16 个SCL时钟以及一个Stop 信号,从而使总线恢复正常状态。

在软件上,也应当设计相应的监测和预判机制,以保证IPMB 总线的稳定工作。

IPMC 单元一旦检测到无法从IPMB 总线上获取到心跳信息,立即控制LTC4307 将本板卡从IPMB 总线上断开,记录故障告警信息,再复位I2C控制器,重新打开LTC4307 尝试与ChMC 进行通信,如果依然失败,将板卡从总线上断开,并点亮告警指示灯提示人工干预。

ChMC 单元监测所有板卡的心跳信息(包括冗余ChMC),当检测到某一板卡的IPMB 心跳信息丢失,而其他板卡的心跳信息正常时,确认该板卡拔出或故障,记录并上传告警信息。当检测到所有心跳信息丢失时,确认本板故障,立即控制LTC4307 将本板从IPMB 总线上断开,记录故障告警信息,再复位I2C 控制器,重新打卡LTC4307 尝试与其他板卡进行通信,如果依然失败,将板卡从总线上断开,并点亮告警指示灯提示人工干预。

2.2 机框管理单元ChMC 设计

IPMI 设计的应依据如下原则:

a.低功耗——VPX 系统提供给每槽位IPMI 模块的3.3V-AUX 电源功耗小于1A;

b.硬件一体化设计——节省为系统功能部分电路节省PCB 面积,同时低复杂度的硬件设计降低硬件故障风险;

c.软件设计简单化以降低软件故障风险,保证IPMI 部分软件具有极高的可靠性;

依据上述原则,ChMC 硬件电路应满足如下需求:

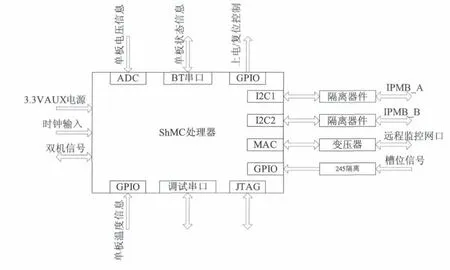

a.具备2 路I2C 接口连接到两路背板IPMB总线。

b.具备2 路UART(通用异步串口)接口,1 路用作和功能单元CPU 进行通信,以获取板卡运行状态信息,1 路用作调试接口。

c.具备多通道ADC 模块,用以对功能电路各供电电源进行监测。

d.具备LAN(以太网)通信接口,用以连接远端PC 接受上位系统管理系统控制。

e.具备丰富的GPIO 资源,用以控制功能电路上下电、复位、槽位信息获取、单板温度监控等功能。

f.具备看门狗电路,以增加系统软件的可靠性。

TI公司的ARM CortexTM-M3处理器LM3S6918,单芯片即可满足上述功能,该处理器运行速率最高可达50M,集成了RTC、看门狗功能,对外接口十分丰富,具备2 路I2C 接口,2 路UART 接口,集成10/100 以太网MAC 和PHY,最多可达38个GPIO,集成8 通道12 位ADC,典型功耗仅为100多毫安。

ChMC 的具体实现框图如图3 所示。

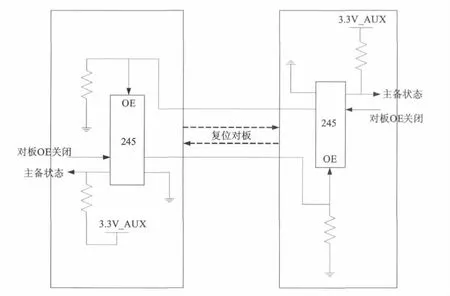

由于ChMC 负责整个机框的管理,所以ChMC应是整个系统中可靠性最高的组件之一。除了在软硬件设计上注重其可靠性设计外,大多数设计中均采用主备冗余设计方案来进一步提高该单元的可靠性。而竞争电路是主备冗余设计中的关键,下面给出一种ChMC 主备竞争电路的实现方法(见图4)。

图3 机框管理单元ChMC 实现框图

图4 ChMC 主备竞争电路

具体工作原理如下:

ChMC 上电工作后,先获取槽位号,接着发出对板OE 关闭信号,然后获取本板主备状态信息。

当两个单板先后(插入机框)上电时,后上电单板上的245 使能信号OE 会被先上电的单板关闭,同时它发出的对板OE 关闭信号被本板245 隔离掉了,因此后上电的单板读取的主备状态为“1”,即备用状态。先上电的单板245 使能端默认有效,读取的主备状态为“0”,即主用状态。

当两个单板已经在机框内并同时上电时,系统设计默认某一槽位为主用ChMC,软件设计时将根据槽位号在输出对板OE 关闭信号时做不同的延迟,默认备用的ChMC 在发出对板OE 关闭信号时会延迟若干微秒,以保证主用ChMC 先工作。

IPMI 正常工作时,主备ChMC 定期互发心跳消息,同时监控各单板IPMC 发出的心跳消息,当备用ChMC 发现无法接收到主用ChMC 心跳消息,而又能监控到各IPMC 心跳消息时,即可确认主用ChMC故障,发出主用ChMC 复位信号,将其复位,主用ChMC 复位后会释放对板OE 关闭信号,同时会接收到备用ChMC 发出的OE 关闭信号,备用ChMC 轮训到主备状态变为“0”时,切换至主用状态,原主用ChMC 则会检测到主备状态指示变为“1”,并据此切换本板至备用状态。

ChMC 复位过程中会自动通过I2C 隔离器件将自己从IPMB 总线上隔离,复位完成后再接入IPMB总线。

主备竞争的信号在VPX 连接器中用户自定义的单端信号上实现。

2.3 板载IPMC 设计

板载IPMC 和上述ChMC 相比较,最大的区别在于IPMI 管理层软件的设计,二者的硬件设计基本相似,具体可参见ChMC 单元进行实现。

板载IPMC 除了监控本板电压、温度信息外,还需要获取本板功能电路的运行状态,将功能电路的故障机告警信息上报到ChMC。功能电路状态的监控一般由本板CPU 进行,通过专用串行串口将监控信息上报给IPMC[6]。当ChMC 作为一个硬件单元集成在某一功能板卡上时,也实现上述功能。从可靠性和成本的角度出发,大多数设计中均依据IPMI规范简化设计,因此IPMC 在设计上不考虑以太网通信的实现,也没有主备冗余设计。

3 结束语

本文针对VPX 系统管理的具体应用,介绍了IPMI 的一些基本功能,着重描述了IPMI 在VPX 系统中的实现示例,该方案以低功耗ARM 处理器为核心,即可以用作ChMC 电路的设计也用作板载IPMC 的设计,仅需要在软件上做相应的改动即可,此外还引入了ChMC 1 +1 冗余设计的概念,具有良好的灵活性和很高的可靠性。

[1]谢勇祥,曲道奎.ATCA 之机箱管理及高可靠性设计与实现[J].微计算机信息,2007,23(2-2) :42-43.

[2]Intelligent Platform Management Interface Specification,V2.0[S].Intel,HP,NEC,Dell,2005.

[3]李威,尚学群,陈建全.ATCA 管理模块模拟器的设计与实现[J].科学技术与工程,2010,10(5) :1271-1274.

[4]李彦英,邹少云.PCA951X 在ATCA 架构上的应用[J].集成电路应用,2005:70-71.

[5]赵辉,董德存.I2C 总线技术及其应用实例[J].微型电脑应用,2005,21(4) :61-63.

[6]李彦,陈德人,梁达明.基于IPMI 的虚拟远程串口终端[J].现代机械,2006,(3) :35-37.