基于ARM的便携式1553B总线测试系统的设计与实现

程 鹏,苗克坚

(西北工业大学 计算机学院,陕西 西安 710072)

随着航空电子系统的发展,多路数据传输数据总线在航空电子系统中起着越来越重要的作用,其主要特点是集中控制、实时性要求高、分布处理[1]。1553B总线以其具有较高的可靠性和灵活性,广泛应用于军事、航空航天系统[2]。传统的1553B测试设备采用普通计算机或工控机作为测试平台,通过PCI总线与被测设备通信,这对测试设备的携带造成极大不便。本文所阐述的测试系统以ARM9作为中央处理器,以DDC的BU-64843T7作为1553B协议芯片,从而实现系统的小型化和便携化,应用FPGA实现ARM时序与1553B时序的转换,并采用Linux操作系统以确保系统稳定可靠。

1 ARM与FPGA数据通信接口设计

1.1 系统硬件介绍

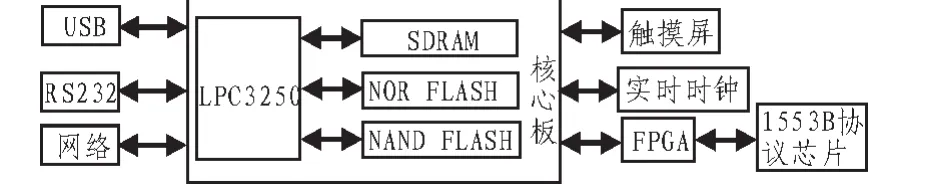

该系统硬件由LPC3250核心板、外扩接口电路、FPGA和1553B协议芯片组成组成。系统架构如图1所示。

图1 系统架构图Fig.1 System architecture

LPC3250微处理器面向低功耗、高性能的应用,采用ARM926EJ-SCPU内核,实现5级流水处理并采用哈佛结构,可工作在266 MHz的频率下,数据处理能力强大。

本系统外扩USB、RS232和网络接口,用于操作系统的烧写和驱动程序、应用程序的调试,并且配备实时时钟,可以掉电保持。为增加其可靠性,本系统在多处增加ESD芯片,以增强系统的抗静电能力。

FPGA采用Altera公司的Cyclone I系列的EP1C6Q240C8芯片,该系列芯片具有20 060个逻辑单元以及288 kb RAM,支持3.3-V LVTTL/CMOSIO标准,可直接与ARM通信,无需进行电平转换。

1553B协议芯片选择DDC公司的BU-64843T8芯片。该芯片是世界上第一个将1553B协议芯片和隔离变压器集成到一体的芯片。因此,在布PCB时,会节省很大空间,从而使系统小巧,方便携带。

1.2 接口电路设计

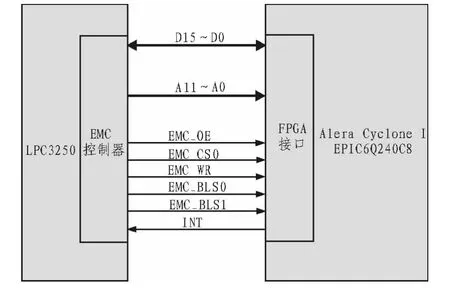

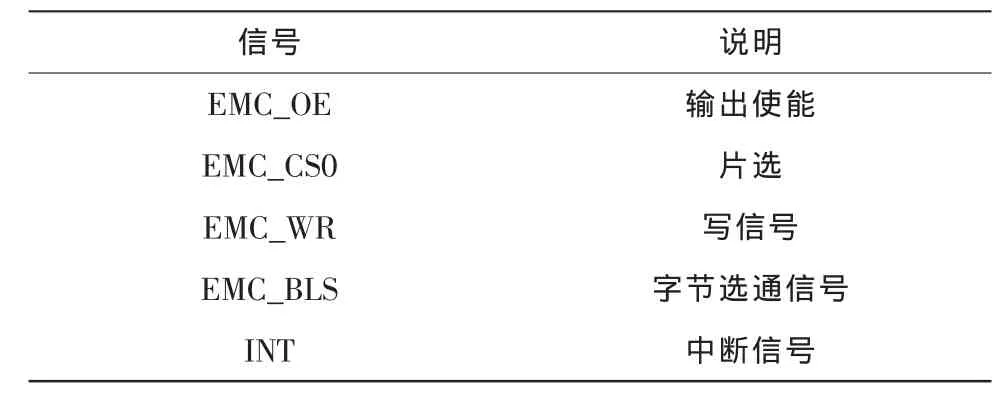

LPC3250包括3个外部存储器接口,分别是NANDFlash控制器、Secure Digital控制器和外部存储器控制器(External memory controller,简称为EMC)。EMC提供了系统总线与片外存储设备之间的接口功能,可实现与SDRAM、DDR SDRAM和SRAM设备的通信。该系统采用EMC的静态RAM接口与FPGA进行通信,该接口具有时序操作简单,接口速度快等特点。利用FPGA模拟静态RAM,并进行时序转换,从而实现ARM对1553B芯片的访问。图2为ARM与FPGA的接口电路图,由于1553B芯片内部RAM为4K*16bit,因此数据线选用16位,地址线选用12位。通过EMC静态存储器控制器的配置寄存器,可将数据总线分别设置为8位、16位、32位。该系统需将配置寄存器的低两位设置为01,即16位总线。其他控制信号说明见表1所示。

图2 ARM与FPGA接口电路Fig.2 Interface circuit of ARM and FPGA

表1 控制信号说明Tab.1 Control signals introduction

1.3 FPGA逻辑设计

若想成功访问1553B设备,必须严格按照1553B时序进行操作,然而EMC的时序与1553B的时序差异很大,因此需要进行时序转换,这通过一片FPGA来实现。BU-64843T8的控制信号主要包括,TRANSPARENT/BUFFERED*、STRBD*、SELECT*、RD/WR*、MEM/REG*、IOEN*、READYD*、ADDR_LAT/MEMOE*,RT_AD_LAT*,INT* 等信号。

TRANSPARENT/BUFFERED*信号用于设定芯片工作在透明模式还是缓冲模式,该系统的1553B不需外扩存储器,工作在缓冲模式下即可,因此MEMOE*等信号可以不做考虑;STRBD*和SELECT*可接到一起,作为芯片的片选信号;RD/WR*为读写信号;MEM/REG*用来区分访问内部4K存储器资源还是寄存器资源;IOEN*有效时,标志芯片正在处理外部的访问;READYD*信号在本系统中十分重要,当ARM写时,READYD*有效表示数据成功写入芯片中,当ARM读时,READYD*有效表示数据线上的数据有效,可以使用;ADDR_LAT为地址锁存信号,对于总线未复用的处理器,该信号置为高;RT_AD_LAT*信号为RT地址锁存信号,该信号出现上升沿,即可将RT地址上的数据锁存到芯片内部,因此RT地址无需一直保持着。INT*信号用于中断ARM,该信号经过FPGA与ARM的GPIO引脚相连 ,相应的GPIO引脚被配置为外部中断引脚。

FPGA的逻辑设计采用锁存的方式,即所有的地址信号、数据信号、读写、片选、EME/REG*信号通过锁存器直接打到总线上,这些信号在ARM访问期间一直有效。因此ARM需要进行多次写操作:先把要写的数据送出,再把要访问的地址和控制信息送出,之后循环读取READYD*信号,直到其有效,再进行下一次读写操作。相关的VHDL代码如下:

PROCESS(RST,CONTR_WORD_LATCH)--锁存控制和地址信号

BEGIN

IF RST='0'THEN

CONTR_REG1<=X"0002";

ELSIF CONTR_WORD_LATCH='1'THEN

CONTR_REG1<=BD;

END IF;

END PROCESS;

PROCESS(RST,WRITE_DATA_LATCH)--锁存数据信号

BEGIN

IF RST='0'THEN

WRITE_DATA_REG<=X"0000";

ELSIF WRITE_DATA_LATCH='1'THEN

WRITE_DATA_REG<=BD;

END IF;

END PROCESS;

A_6484(11 downto 0)<=CONTR_REG1(15 downto 4);--

将地址送到BU-64843T8地址线

MEM_REG<=CONTR_REG1(3); --

将控制信号送到BU-64843T8

RD_WR<=CONTR_REG1(2);

STRBD<=CONTR_REG1(1);

2 1553B驱动程序的开发原理与实现

2.1 文件操作接口

设备驱动程序在Linux内核中扮演着特殊的角色。它们是独立的模块,使某个特定的硬件响应一个定义良好的内部编程接口,用户的操作通过一组标准化的调用执行,而这些调用独立于特定的驱动程序。将这些调用映射到作用于实际硬件的设备特有操作上,则是设备驱动程序的任务。系统软件架构如图3所示。

图3 系统软件架构图Fig.3 System software architecture diagram

Linux驱动程序支持3种类型的设备:字符设备、块设备和网络设备。字符设备是个能够像字节流一样被访问的设备。字符设备驱动程序通常要实现open、close、read、write系统调用。本系统的1553B设备属于字符设备,它的驱动程序主要包括以下几个模块:初始化模块、打开关闭模块、读写模块、中断处理模块。

驱动程序与应用程序的通信主要通过系统函数调用,Linux为所有设备文件提供统一的操作函数接口,我们的驱动程序中只需实现struct file_operations中相应的函数即可,主要包括 ioctl、read、write、open、release、fasync 函数。 具体 C语言代码如下所示:

static const struct file_operations xc1553_fops=

{

.owner =THIS_MODULE,

.ioctl=xc1553_ioctl,//用于自定义IO操作

.open=xc1553_open,//用于响应文件系统的open操作

.write=xc1553_write,//实现写功能

.read=xc1553_read,//实现读功能

.release=xc1553_release,//用于响应文件系统的close操作

.fasync=xc1553_fasync,//用于实现异步通知

};

当用户加载驱动模块时,一系列初始化工作在static int__init xc1553_init(void)函数中完成,包括设备注册,物理地址到虚拟地址的映射,EMC模式的配置,中断处理函数的注册。

当用户卸载驱动模块时,需要在static void__exit xc1553_exit(void)函数中进行驱动模块和设备的卸载,以及中断号的释放。

2.2 中断处理模块的实现

当1553B产生中断时,由xc1553_init函数中注册的中断处理函数进行处理,并且通知上层应用程序进行读写操作。驱动程序与应用程序的通信通过异步通知的方式实现。为了实现异步通知,在驱动程序中需要实现int fasync_helper(int fd,struct file*filp,int mode,struct fasync_struct**fa)和 void kill_fasync(struct fasync_struct**fa,int sig,int band)函数。

fasync_helper函数在xc1553_fasync中实现,作用是为当前进程创建一个fasync_struct结构体,然后挂入目标设备的fasync队列,最后在设备驱动的中断处理程序中,使用kill_fasync函数向该队列发送信号,通知上层应用程序。

xc1553_fasync函数实现如下:

static int xc1553_fasync(int fd,struct file*filp,int on)

{

int retval;

retval=fasync_helper(fd,filp,on,&fasync_queue_1553);

if(retval<0)

{

printk("xc1553_fasync"DEV_NAME"!---failed ");

return retval;

}

else

{

printk("xc1553_fasync"DEV_NAME"!---success ");

}

return 0;

}

中断处理函数实现如下:

static irqreturn_t xc1553_interrupt(int irq,void*dev_id,struct pt_regs*regs)

{

…

if(fasync_queue_1553)

{

//向进程队列发送SIGIO信号

kill_fasync(&fasync_queue_1553,SIGIO,POLL_IN);

printk("success kill fasync! !");

}

else

{

printk("fasync queue is null! ");

}

sic2_er=io_p2v(SIC2_BASE+INTC_MASK);//物理地址到虚拟地址的映射

sic2_rsr=io_p2v(SIC2_BASE+INTC_RAW_STAT);

__raw_writel((1<<15),sic2_rsr);//清中断

__raw_writel((1<<15),sic2_er);//重新使能中断

return 0;

}

3 结束语

1553B总线[7-8]广泛应用于航空领域,基于1553B总线的测控设备普遍体积大,携带不方便,本文所阐述的测试系统完全能够实现传统测控设备的功能,并且极大的缩小了设备的体积,方便携带。经过测试,该系统实时性高、工作稳定,能够满足军工要求。

[1]宾辰忠,苗克坚.基于1553B总线的实时消息流实现与控制[J].计算机测量与控制,2005,13(9):967-969.BIN Chen-zhong,MIAO Ke-jian.Message Stream Research and Implementation in Real-Time Network System Based on 1553B Bus[J].Computer Measurement&Control,2005,13(9):967-969.

[2]吴小强,李庆,张望远.Linux下1553B驱动软件实时性设计与实现[J].计算机测量与控制,2011,19(10):2564-2566.WU Xiao-qiang,LI Qing,ZHANG Wang-yuan.Design and implementation of real-time 1553B driver under Linux[J].Computer Measurement&Control,2011,19(10):2564-2566.

[3]MIL-STD-1553B Digital Internal Time Division Command/Response Multiplex Data Bus[S].USA Military Standard,1978.

[4]高志强,苗克坚,张雯璐.弹载计算机1553B总线测试模块设计[J].计算机测量与控制,2008,16(9):1280-1282.GAO Zhi-qiang,MIAO Ke-jian,ZHANG Wen-lu.Testing Module Design of 1553B Bus in Missile Borne Computer[J].Computer Measurement&Control,2008,16(9):1280-1282.

[5]Corbet J,Rubini A,Kroah-Hartman G,LINUX设备驱动程序[M].第三版.魏永明 耿岳 钟书毅,译.北京:中国电力出版社,2005.

[6]蒋贵全,张辉,王国锋.基于Linux的FPGA数据通信接口驱动设计与实现[J].计算机应用,2009,29(9):2520-2522 JIANG Gui-quan,ZHANG hui,WANG Guo-feng.Design and implementation of FPGA data communication interface driver based on Linux[J].Journal of Computer Applications,2009,29(9):2520-2511.

[7]吴云忠.基于PCI接口的1553B总线控制软件设计[J].现代电子技术,2013(24):47-49.WU Yun-zhong.Design of 1553B bus control software based on PCI interface [J].Modern Electronics Technique,2013(24):47-49.

[8]张启敏,孙剑波,权云涛.1553B总线网络中RT终端系统的软件设计[J].电子科技,2014(3):38-40.ZHANG Qi-min,SUN Jian-bo,QUAN Yun-tao.Design and implementation of RT terminal system software in 1553B bus network[J].Electronic Science and Technology,2014(3):38-40.