数字化时差法超声采集卡设计与实现

李文强,黄 刚,杨 录

(1.中北大学 电子测试技术国家重点实验室,太原 030051; 2.太原工业学院 电子工程系,太原 030008)

数字化时差法超声采集卡设计与实现

李文强1,黄 刚2,杨 录1

(1.中北大学 电子测试技术国家重点实验室,太原 030051; 2.太原工业学院 电子工程系,太原 030008)

为满足工程需要,研制出一种数字化、四通道、时差法超声采集卡。本采集卡中的关键研究方法和结果由三部分组成:首先,数模转换模块选用TLC5620,输出DC电压0~2.5 V可调、精度0.01 V,提供超声接收电路压控放大的压控信号;其次,门控模块选用CPLD的门控模块,门控范围1~127 μs,精度0.5 μs,提供回波的门前沿和门宽控制信号;最后,时间测量模块选用TDC-GP1,测量范围0.1 μs~1.6 ms、分辨率125 ps,实现超声发射与接收信号的时差测量。实测表明:本采集卡能满足透射时差法超声无损检测的要求,并可为其工程应用提供平台。

超声采集卡;CPLD;时差法;门控

透射时差法超声无损检测方法与传统幅值法相比,具有抗噪能力强,电路简单,灵敏度和检测效率高,适用范围广等优点[1],但作为一种新技术,还有一些基础工作需要完成[2],因为现有的超声采集卡不具有以下功能: 皮秒级的时间测量;数字化门控;数字化压控放大所需的直流电压。针对以上问题,研制一种数字化、四通道、时差法超声采集卡,并具有一定的现实意义和工程价值。

1 采集卡系统设计

根据以上分析,设计出一种超声采集卡[3-6],其系统框图如图1所示。图1中,选用ALTERA公司的EPM9560ARC208-10的CPLD为主控器[7],选用Cypress公司的CY7C68013为USB2.0接口芯片,选用ISSI公司的IS64WV10248B为RAM存储芯片,选用ACAM公司的TDC-GP1为时间测量芯片,选用TI公司的TLC5620为DA芯片,触发模块和门控模块由CPLD内部逻辑单元实现。下面将分别介绍采集卡核心模块的软硬件设计。

图1 采集卡系统框图

2 系统设计的关键点

2.1 触发模块

触发模块提供四路脉冲信号给超声发射电路,使探头激发出超声波[8-9]。该四路触发脉冲是矩形波,可并行方式产生也可串行产生,无损检测时多需要串行方式。触发脉冲的高电平时间越长,发射的超声波越强,但控制高压源的功率型场效应管导通时间会越长,而场效应管的使用寿命会越短。触发脉冲的频率越高,检测效率越高,但触发脉冲的频率越高,要求高压源的工作频率越高。根据实际验证,检测对象若为常见金属且其径向尺寸在10 cm以下,触发脉冲的高电平在1~4 μs,频率在10 kHz以下较为合适。图2为8 kHz波形仿真。图中,clk-1M是频率为1 MHz输入脉冲,计数器reg-clk-8k对clk-1M计数,在clk-1M的第1~4前4个周期使输出信号clk-8k保持高电平,在clk-1M的第5~124和0的后121个周期使clk-8k保持低电平,并按此规律循环,从而保证clk-8k频率为8 kHz的脉冲信号。对clk-8k信号进行4分频,得到高电平持续时间为4 μs,低电平持续时间为496 μs,即频率为2 kHz的四路触发脉冲。

图2 8 kHz波形仿真

2.2 门控模块

门控模块提供四路信号,控制超声回波的门前沿和门宽[10],为简化电路,降低成本,提高柔性,用CPLD的内部逻辑单元代替传统用4片82C54实现门控。图3为门控模块的波形仿真。由门控模块的波形仿真图知,设置门前沿和门宽的时序(以B通道为例):

1) 触发使能信号tri-en=0,禁止触发;

2) 门控片选cs-gate=2,选择B通道门前沿,7位数据线data-gate[7..0]=8;

3) 门宽写使能gate-wr-en产生下降沿,将data-gate的数据写入B通道门前沿寄存器gate-pB,即gate-pB=8,完成门前沿设置。

同理,cs-gate=3,选B通道门宽,在gate-wr-en下降沿,将data-gate的数据写入B通道门宽寄存器gate-wB,即gate-wB=6,完成门宽设置。

图3 门控模块波形仿真

由门控模块波形仿真图知,门前沿和门宽的控制过程(以B通道为例):

1) tri-en=1允许触发,四路8 kHz触发脉冲tri-ABCD=2,表明B通道产生触发脉冲,同时触发标志tri-flag输出脉冲信号,tri-flag等于四路触发信号的逻辑或,供调试使用;

2) B通道门控信号gate1=1,门前沿计数寄存器rg-p,在2 MHz时钟信号clk-2M的上升沿,在tri-flag的下降沿从0开始进行门前沿计数;

3) 当rg-p=8时,gate1=0门前沿计数结束,计数值为8,即门前沿时间为4 μs;同时门宽计数寄存器rg-w,在clk-2M的上升沿,从0开始进行门宽计数;

4) 当rg-w=6时,gate1=1门宽计数结束,计数值为6,门宽时间为3 μs。

另外,门前沿计数结束后的下一个时钟,rg-p归零;门宽计数结束后的下一个时钟,rg-w归零。因为rg-p和rg-w都是7位寄存器,所以门前沿、门宽的范围都是0.5~63.5 μs;时钟信号周期为0.5 μs,所以门前沿、门宽的精度都是0.5 μs。那么,门控范围为1~127 μs。

2.3 DAC模块

TLC5620是一种四路、SPI接口的8位电压输出型数模转换器DAC,四路基准电压可独立设置。TLC5620有四种控制方式,本文选用工作方式1,即装载线LOAD控制方式,要求装载DAC控制信号LDAC恒为低电平,电路中可直接将LDAC引脚与地线连接。串行数据输入顺序依次为:A1、A0、RNG、D7、D6、D5、D4、D3、D2、D1、D0,其中:A1、A0为地址选择,00、01、10、11依次选择通道A、B、C、D;RNG为输出是否倍增,RNG=0不倍增,RNG=1倍增;D7~D0为8位串行数字量。在时钟CLK下降沿,将数据线DATA的数据送入串行寄存器。在LOAD的下降沿,将输入的数字数据锁入输出门,并刷新电压输出。图4为TLC5620工作方式1的仿真时序。图4中:需要24个clk-1M,完成1次对TLC5620的操作;地址线addr-tlc5620=2,同时第1个、第2个串行时钟clk-tlc5620的下降沿,串行数据输入端din-tlc5620分别为1和0,表明选择C通道;第3个clk-tlc5620的下降沿,din-tlc5620=0,表明RNG=0输出不倍增;数据线data-tlc5620=0x9A,即154,同时第4个到第11个clk-tlc5620的下降沿,din-tlc5620依次为1、0、0、1、1、0、1、0,根据DA转换公式:

(1)

式中:Vout为DA转化结果,即输出的电压,V;Vref为输入的基准电压,V;Din为输入的数字量,取值范围为0~255;RNG为输出是否倍增,RNG=0不倍增,RNG=1倍增。系统中,Vref=2.5 V,Din=154,RNG=0,经计算Vout=1.50 V,实测10次得其均值为1.49 V,误差为0.01 V。选用REF3025为2.5 V基准电压芯片,其精度为0.2%,因此,DAC模块的理论误差为0.02 mV。

图4 TLC5620工作方式1的仿真时序

2.4 TDC模块

TDC-GP1是一种高精度时间数字测量芯片,本采集卡选用0.1 μs~1.6 ms的测量范围。在超声无损检测中回波时间一般在几μs到上百μs。本采集卡选用TDC-GP1在高分辨率模式下的测量范围2,分辨率可达到125 ps,测量时间t:

(2)

式中:Tref为外部输入的基准时钟周期;N为基准时钟的分频数,可为0~6的整数,由控制寄存器CR4的位5到位7设置;n为TDC-GP1的计数值,可由32位的结果寄存器RR0~RR7得到;FC1为开始信号与相邻校准时钟上升沿的时间差;FC2为停止信号与相邻校准时钟上升沿的时间差;C1、C2分别为1个、2个校准时钟周期。

由于触发信号为串行方式,因此可用1片TDC-GP1实现A、B、C和D四路超声发射与接收信号间的时间差测量,降低硬件成本和电路结构。此时要对四路收发信号进行四选一处理,可通过2条assign语句:“assign Dec-STA=Tri-A|Tri-B|Tri-C|Tri-D”和“assign Dec-STO=Echo-A|Echo-B|Echo-C|Echo-D”实现。其中Tri-A、Tri-B、Tri-C、Tri-D为四路触发脉冲信号,Echo-A、Echo-B、Echo-C、Echo-D为四路回波脉冲信号,Dec-STA、Dec-STO分别为四选一后的触发和回波信号,分别控制TDC-GP1的启动和停止计时。

图5为TDC模块逻辑符号,该模块设置TDG-GP1和读取时间测量结果。其中设置TDG-GP1的数据来自USB总线,分以下几个步骤,该操作需要7 μs:

1) 通过4位地址总线addr-usb-wr[3..0]选择设置的寄存器;

2) 通过8位数据总线data-usb-wr [7..0]设置选择的寄存器;

MS条件:EI源,电子能量70 eV;离子源温度200℃,四级杆温度150℃,质量数扫描范围35~350 amu。

3) 通过写命令线wr-en-tdc启动写程序,按照1 MHz的时钟clk-1M对TDG-GP1操作。

图5 TDC模块的逻辑符号

读取TDG-GP1的测量结果需要32 μs,分以下几个步骤:

1) 通过读命令线rd-en-tdc启动读写程序,并按照clk-1M对TDG-GP1进行读写操作。

2) 写入初始化TDC和ALU单元命令(11,0x07);

3) 依次读取小数部分的低8位、高8位,整数部分的低8位、高8位数据,并通过RAM写控制信号ram-wr-tdc和数据线result-tdc[7..0]将数据依次写入RAM。

式(2)中的n值可通过式(3)求取:

(3)

式中:FL,FH分别为小数部分的低8位、高8位;IL、IH分别为整数部分的低8位、高8位。因为FH的最高位为符号位,所以n的最大值nmax=32768。同时将Tref=0.05 ns(系统中TDC-GP1的外部时钟为20 MHz),N=0,代入式(2)并忽略校准参数,经计算得Δt的最大值Δtmax≈1.6ms,Δt的最小值Δtmin=0.1 μs;如果N=6,则Δtmax≈104.9 ms,Δtmin=6.4 μs。如果用ns表示,则

Δtmin=1.5×Tref×2N+25.

(4)

2.5 存储模块

IS64WV10248B是一款并行、1 MB、高速RAM,本文用2片IS64WV10248B通过字扩展实现2 MB容量存储时差,1次超声收发的时差需要4 B的存储单元,2 MB容量可存储218次时差数据。

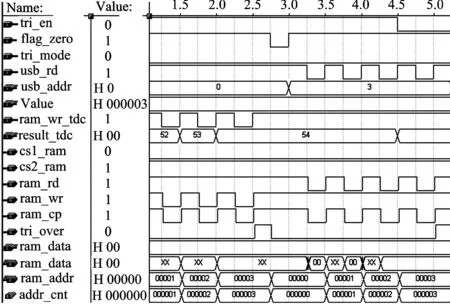

图6 RAM读写的波形仿真

图6为RAM读写的波形仿真。tri-en为触发使能信号,tri-en=1启动触发;tri-mode为触发模式信号,tri-mode=0固定点数触发(检测模式),tri-mode=1连续触发(调试模式);flag-zero为地址清零信号,下降沿使RAM读写地址归零;value为检测模式下RAM读写的最大地址;ram-cp为RAM读ram-rd和RAM写ram-wr信号的逻辑或,ram-cp使读写RAM时既可减少逻辑单元,又可简化程序结构;tri-over为高电平有效,检测模式下标志触发完成。由RAM读写的波形仿真图看出,写RAM时序为:

1) tri-en=1, flag-zero=1,在ram-wr-tdc的4个下降沿,RAM地址总线ram-addr从0递增到3,将0x51、0x52、0x53、0x54共4个数,通过RAM数据总线ram-data写入RAM;

2) tri-mode=0检测模式,ram-addr和value 相等(值都为3),tri-over=1表明触发完成。

读RAM时序为:

1) flag-zero产生下降沿,ram-addr归零;

2) usb-addr=3表明要读取RAM数据,flag-zero=1,在usb-rd的4个下降沿,ram-addr从0递增到3,从RAM内部依次连续读取4个字节数据放入ram-data。

由于ram-data是三态总线,所以仿真时不能查看ram-data端的数据。

3 结论

通过系统分析和实测表明:

1) 采用TDC-GP1其测量范围和精度,可满足透射时差法超声无损检测的时间测量要求;

2) 采用CPLD内部逻辑单元代替82C54实现门控,范围和精度都满足要求,且降低了硬件成本,简化了电路结构;

3) RAM的读RD、写WR控制统一为1个控制信号CP,减少了逻辑单元,简化了控制过程。

[1]李文强,马福昌,张英梅,等.新型超声无损检测方法的研究[J].太原理工大学学报,2011,42(2):126-129.

[2]李文强.透射时差法超声无损检测技术研究与系统实现[D].太原:太原理工大学,2011.

[3]朱斌,殷晨波,陶春旻,等.基于恒流配气方式的微气体传感器测试系统研究[J].仪器仪表学报,2011,32(12):2681-2687.

[4]封洲燕,陈丹,肖乾江.一种闭环式神经电刺激系统的设计[J].仪器仪表学报,2012,33(2):279-285.

[5]张稳稳,吴朝新,朱仁龙,等.有机电致发光器件稳定性测试系统的设计与实现[J].西安交通大学学报,2011,45(2):64-67.

[6]周建新,李藜,康文,等.旋转线圈测量系统信号采集设备的研制[J].原子能科学技术,2013,47(5):893-896.

[7]彭勇,王克鸿,周琦,等.基于CPLD的电子束同步扫描控制系统[J].焊接学报,2011,32(11):57-60.

[8]沈春龙,彭勇,周琦,等.真空高能电子束瞬态数据采集及预处理[J].焊接学报,2013,34(3):1-4.

[9]李桓,王俊红,艾丹凤,等.弧焊过程中多信息同步采集系统[J].天津大学学报,2012,45(2):184-189.

[10]李文强.杨录.超声回波门参数数字化控制方法的研究与实现[J].仪表技术与传感器,2012,50(7):100-104.

(编辑:刘笑达)

DesignandImplementationonDigitalUltrasonicAcquisitionCardBosedonTime-differenceMethod

LIWenqiang1,HUANGGang2,YANGLu1

(1.StateKeyLaboratoryforElectronicMeasurementTechnology,NUC,Taiyuan030051,China;2.DepartmentofElectronicEngineeringTIT,Taiyuan030008,China)

In order to meet the need of engineering, this paper designs a four-channel digital ultrasonic acquisition card based on time. The key research methods and three results of the card include: Firstly, D/A module TLC5620,which outputs voltage from 0 to 2.5 VDC with a precision of 0.01 V, can offer voltage control signal to VCA in ultrasonic receiving circuit. Secondly, gate control module used logic units in CPLD,which controls time from 1 to 127 μs with a precision of 0.5 μs, can offer signal to control forward gate and width gate for echo. At last, time measurement module TDC-GP1 can measure time difference between ultrasonic transmitting signal and ultrasonic receiving signal, which gives the measurement of time range from 0.1 to 1.6 ms with a resolution of 125ps. A series of measurements show that, the card can meed the needs of ultrasonic nondestructive testing technology based on time-of-flight transmission method, also can provide a platform for its engineering application.

ultrasonic acquisition card; CPLD; time-difference method; gate control

2013-08-25

山西省科技攻关项目(20130321014-02);山西省自然科学基金项目(2011011015-2);教育部新型传感器与智能控制教育部重点实验室(太原理工大学)开放课题基金资助项目(N201309)

李文强(1976-),男,陕西渭南人,博士,讲师,主要从事仪器仪表与自动检测研究,(Tel)13994238622

1007-9432(2014)02-0255-04

TB551

:A