基于串行FRAM的固态存储器构建

张小鸣,宋 磊

(常州大学信息科学与工程学院,江苏常州213164)

基于串行FRAM的固态存储器构建

张小鸣,宋 磊

(常州大学信息科学与工程学院,江苏常州213164)

为简化嵌入式系统利用NAND闪存保存大容量数据的设计复杂性,提出一种利用铁电随机存储器(FRAM)构建固态存储器实现快速高效存取的方法。制定串行FRAM与RAM相结合的最优存储协议,给出查询存储器块的概念和串行FRAM存储数据的快速查询算法,介绍串行FRAM与RAM相结合的存储协议和FM24W256的块读写算法。51单片机的电机驱动总成载重测试仪设计与工业性实验结果表明,利用FRAM设计的固态存储器,具有软硬件开销小、存取速度快、实现简单可靠的特点,能满足嵌入式系统长期存储的要求。

固态存储器;铁电随机存储器;存储协议;I2C总线;数据查询;块读/写

1 概述

目前嵌入式系统扩展固态(不易失)存储器的类型主要有3种:EEPROM存储器,NAND FLASH存储器,FRAM存储器。这3种固态存储器各有优缺点,应用场合不尽相同。EEPROM的字节存取速度慢(毫秒级),写入一般需要5 ms~10 ms的等待数据写入时间,功耗大(毫安级),可擦写有限次(约10万次),容量千比特级,适合小数据量的慢速、非频繁存储[1]。NAND FLASH(NAND闪存)存储器的字节存取速度快(纳秒级),功耗小(毫安级),可擦写有限次(约100万次),容量兆比特级,适合大数据量的快速、频繁存储[2]。铁电存储器(Ferroelectric Random Access Memory,FRAM)是一种兼备随机存储器和非易失性存储器特性的高性能不易失存储器,字节存取速度快(串行FRAM为微妙级~毫秒级,并行FRAM为纳秒级),功耗极低(微安级),可擦写无限次(100兆以上,即1014次),容量千比特级,写入后无需任何延时等待,适合小数据量快速、频繁存储[3]。

鉴于串行FRAM存储器种类更多,接口更简单,应用领域更广,本文提出一种串行FRAM与RAM

相结合的存储协议,并在此基础上给出串行FRAM快速存取算法,克服串行FRAM存储器数据查询繁琐的局限。

2 背景介绍

电可擦除可编程只读存储器(Electrically Erasable Programmable Read-Only Memory,EEPROM)兼备了RAM和ROM的基本特点,既可随机读写,也可断电后数据不易失。EEPROM分为串行EEPROM和并行EEPROM,串行EEPROM因占用引脚少、容量扩展配置灵活以及读写操作相对简单而在嵌入式系统中作为一种固态存储器得到了广泛应用。目前,较为常用的串行EEPROM是24C系列,但是由于串行EEPROM的读写速度较慢,主要用于保存设备所需要的配置数据等存取频率不高的场合[4]。

NAND FLASH存储器容量大,已成为嵌入式系统的大容量存储器。但是,NAND FLASH存储器由于生产工艺的原因可能存在无效块,需要通过软件检测跳过无效块,无形中增加了软件开销[5]。NAND FLASH存储器只能按页写(每页由256 Byte~2 048 Byte组成),按块(32页)擦除,存取不灵活,块擦除时间与页读写时间相对长[6]。文献[7]介绍了一种基于FPGA控制器对多片NAND FLASH并行总线控制实现高速大容量存储的设计方法,但实现方法复杂。为了解决NAND闪存存储器按页长时间存储与A/D实时采样频率之间的矛盾,文献[8]采用主、从单片机分别控制A/D转换器实时采集数据和NAND闪存存储器的实时存储,通过双口RAM实现采集数据共享和实时存储。采用双口RAM芯片成本较高,接口控制较复杂。

串行FRAM存储容量在0.5 KB~2 MB之间[9],超低功耗,I/O接口简单,成本低,体积小,存储数据安全稳定,已经成为嵌入式系统长时间保存数据的首选固态存储器。文献[10]介绍了Linux下的串行FRAM驱动程序的设计方法,但没有介绍FRAM的存储协议等核心存储技术。文献[11]介绍一种基于单片机的I2C总线FRAM存储器的软硬件设计方法,但未提及数据采集模块的实现以及与FRAM模块的存取关系。文献[12]介绍了基于DSP控制器的I2C总线FM24L64存储器的接口设计方法,存储数据来自GPS接收机RS232串口接收的弹载数据。文献[13]介绍了基于单片机的无线压力检测系统设计,利用压力传感器检测到超阈值压力信号触发唤醒平时处于休眠状态的无线压力传感器节点,激活采集功能模块,将超阈值压力值存储到I2C总线FRAM存储器中。文献[14]介绍了基于蓝牙通信技术的人行动轨迹采集记录系统设计,将人行动轨迹数据实时保存到I2C总线1Mb FRAM存储器中,并周期性发送到服务器。文献[15]介绍了智能水质浊度分布式测量系统的设计,利用I2C总线FRAM芯片FM24CL16存储水质浊度数据,由于水质浊度号变化缓慢,对A/D转换器的采样实时性要求不高。文献[16]介绍了基于PIC单片机的浆果冲击记录装置设计,利用SPI接口FRAM芯片FM25V10(128 KB)存储每次浆果跌落的加速度采集数据。每次跌落实验间隔足以保证A/D采集时序与FRAM存储时序分时进行。文献[17]介绍了基于无线传感器网络的康复治疗用人体运动检测装置,应用I2C总线FRAM芯片FM24V10(128 KB)来存储各种配置参数和算法参数等,但没有用来存储实时采集数据。

随着嵌入式系统对实时性处理要求越来越高,如何充分发挥FRAM存储器的快速存储、存储稳定的优点来满足实时性的要求成为一个现实的问题。到目前为止,FRAM存储器作为嵌入式系统的固态存储器受到2个限制:

(1)并行FRAM存储器,存取速度快,价格较高,在读操作后必须有个预充电过程,来恢复数据位。与传统SRAM在时序上有所不同而不能直接替换。

(2)串行FRAM存储器,存取速度较快,价格较低,种类多,分I2C接口2线FM24系列和SPI接口3线FM25两大系列,时序与传统的24、25型的EEPROM芯片兼容,可以直接替换。SPI存取速度比I2C要快一个数量级,还可实现全双工。但串行FRAM的存储数据查询繁琐,须加载到系统内存RAM中才能查询,软件开销较大。

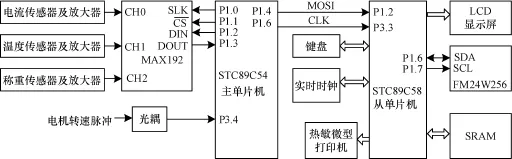

3 电机驱动总成载重测试仪系统框图

电机驱动总成测试仪是电机总成驱动测试台的配套设备,用于不定期抽检一个批次电机驱动总成的载重特性数据,并长期保存在FM24W256中,以备查询,便于分析该批次电机驱动总成的售后质量。通常要求保存期限为1年~2年。电机驱动总成的载重特性数据包括载重实验周期中的最大载重量、最大电机电流、最大电机外壳温升,最大、最小、平均电机转速。测试仪由单片机采集板、单片机显示键盘板、热敏微型打印机等组成,系统结构框图如图1所示。

图1 电机驱动总成载重测试仪系统结构框图

由图1可见,测试仪采用主、从双单片机结构,满足实时处理要求。主单片机控制A/D转换器周期采样称重传感器调理信号,霍尔电流传感器调理信号,温度传感器调理信号,累计单位时间内电机转速脉冲个数,进行标度变换和BCD变换,变换为BCD码格式测试数据,快速发送给从单片机进行数据缓存、实时显示、数据保存。主、从单片机通过模拟SPI接口进行实时通信。制定多字节同步字符通信协议和从机防死锁机构,实现了同步、可靠通信。

内存RAM开辟显示数据缓存区和查询数据缓冲区。显示数据缓存区存放实时采集的测试数据、实时时钟时间值和实时计算产生的载重特性数据。键盘与LCD交互菜单中的测试数据命令激活实时显示测试数据、载重特性数据以及测试周期累计值。保存命令激活单片机与FM24W256之间建立I2C总线读写时序操作,将测试开始实时时钟时间值,载重特性数据和测试周期累计值一起作为一条测试记录保存到FM24W256指定存储区。查询命令激活单片机与FM24W256之间建立I2C总线读时序操作,将FM24W256中对应查询关键字可能覆盖的一个局部存储块中的所有记录均读到查询数据缓冲区中,以便在内存中高效查询,快速找到相匹配的一条或若干条测试记录,送LCD屏调阅显示。打印命令可以将调阅的历史记录打印输出。

4 串行FRAM存取特性

串行FRAM存储结构和存取特性决定了查询数据必须先读出后加载到系统存储级内存才能查询。串行FRAM的存取特性由串行FRAM串行数据帧格式、读写时序以及读/写速率共同决定。

4.1 串行FRAM数据帧格式

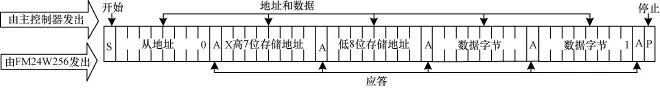

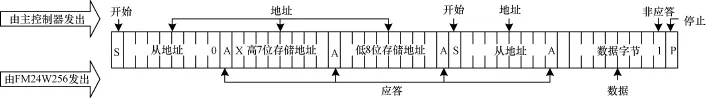

以FM24W256为例,FM24W256的多字节连续写操作串行数据帧格式与传统的24系列EEPROM芯片24C256的一致,如图2所示。

图2 FM24W256多字节写数据帧格式

但是,FM24W256的多字节连续读操作串行数据帧格式与24C256有所不同:FM24W256的连续读操结束非应答位“1”由微控制器主动发出,而不是由FM24W256发出。24C256采用页读操作,每当连续读到64个字节为1页后,24C256自动发出读操结束的非应答位“1”,因此,若需要连续读64个以上的字节长度时,必须分页读,导致存取效率大大降低。

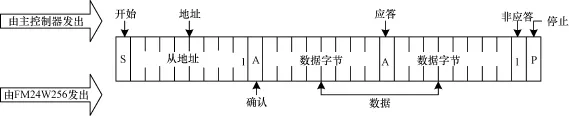

FM24W256的连续读操作数据帧格式只须写I2C总线的同一器件从地址,接着就可从现行存储地址+1开始,顺序读后续地址存储单元的字节,连续读串行数据帧格式如图3所示。

图3 FM24W256多字节读数据帧格式

FM24W256现行存储地址既可以由随机读操作确定,也可以由单字节写操作时序确定。一般来说, FM24W256的连续读操作与一次随机读操作配合使用,即先执行一次随机读操作来确定要顺序读的首地址,即现行存储地址。随机读操作数据帧格式不仅要求写I2C总线的指定器件从地址,而且要求写指定存储单元的15位地址,最后读出该存储单元的8位数据, FM24W256的随机读串行数据帧格式如图4所示。

图4 FM24W256随机读数据帧格式

4.2 串行FRAM读/写时序

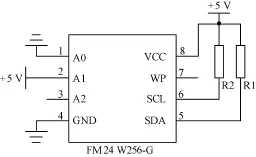

与传统24C256相比,FM24W256读写时序有2个重大改进:(1)在读写时序上不需要任何延时(即使延时也无妨),而24C256必须有至少6 ms以上的延时。(2)FM24C256的连续读/写时序对顺序读字节长度没有限制,而24C256只限为64个字节为一页的页读/写,因此,FM24W256的连续读字节长度完全可以覆盖整个芯片存储容量,为铁电存储器的高效、快速查询奠定了硬件基础。FM24W256的I2C总线最高速率为1 MHz。FM24W256与单片机接口电路实例如图5所示,其中,SCL是串行时钟输入线;SDA是串行输入输出数据线。

图5 FM24W256接口电路实例

5 内存与FRAM存储协议

由于串行FRAM采用串行总线存取,数据读/写要经历一个串并转换(读)和并串转换(写)的过程,因此保存到FRAM的测试数据,必须先缓存在RAM内存中,查询FM24W256中保存的测试纪录,读出并加载到RAM内存中。制定最好的RAM和FRAM存储协议就显得非常关键。最好的存储协议应包括查询关键字存取历史记录最快捷,最简单,适合嵌入式系统内存空间相对较小,微处理器运行速度相对较慢,不能实现复杂查询算法的特点,即要设计出相对简单,易于实现查询算法的存储协议。

5.1 内存存储协议

内存存储协议包括制定测试数据存储格式, RAM和FRAM的映射图等。

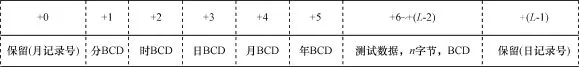

(1)测试数据存储格式

测试数据除了应包含实时测试数据外,还应包含查询关键字和索引号,对于测试仪来说,测试数据都是时间触发事件,最有效的查询关键字就是测试时间信息,例如测试开始时刻的年、月、日、小时、分等。索引号包括月记录号和日记录号。假设测试数据包含实时测试数据字节和测试周期共计n个字节,测试数据开始时间信息为5个字节(年、月、日、时、分),月记录号为1个字节,日记录号为1个字节,则一组测试数据占用的字节长度为L字节(n+ 7)。采用小端模式设计的测试数据存储格式如图6所示。

图6 RAM缓冲器测试数据存储格式

在图6中,偏移地址+0的存储单元在FRAM中映射为月记录号,即1个月中的记录总条数,应根据FRAM存储的现有月记录号基础上递增更新回写,到该保留字节。偏移地址+(L–1)的存储单元在FRAM中映射为日记录号,即一天中的记录总条数,应根据FRAM存储的现有日记录号基础上递增更新回写到该保留字节。测试数据采用BCD码格式存放是为了便于转换成LCD码显示。

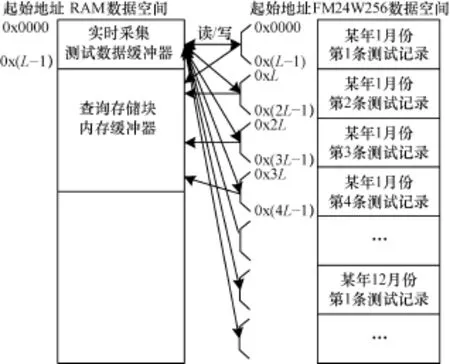

(2)RAM和FRAM的映射图

在测试日期下,RAM缓冲器暂存的实时测试数据,用保存命令陆续写入FRAM的不同存储空间。故只需设置一个内存RAM缓冲器,但索引号要根据FRAM存放的对应年、月上一条记录的索引号来计算确定,并加载到RAM缓冲器测试数据的索引号单

元中。索引号的计算公式为:

若本测试数据的日号=上一条测试记录的日号,且上一条测试记录的日记录号<日记录号上限,且上一条测试记录的月记录号<月记录号上限,则本测试数据日记录号=(上一条测试记录的日记录号+1),且本测试数据月记录号=(上一条测试记录的月记录号+1),否则,本测试数据不能保存。

若本测试数据的日号(上一条测试记录的日号,且上一条测试记录的月记录号<月记录号上限,则本测试数据日纪录号=1,本测试数据月记录号= (上一条测试记录的月记录号+1),否则,本测试数据不能保存。

RAM和FRAM的映射图如图7所示。RAM数据空间的查询存储块内存缓冲器用于缓存从FRAM读出的多条测试记录,便于高效查询。

图7 RAM和FRAM的映射图

5.2 FRAM存储协议

FRAM存储协议包括制定测试记录存储格式,确定查询存储器块容量,设置查询索引号单元等。

(1)测试记录存储格式

由图7可知,FRAM的测试记录存储格式就是内存测试数据存储格式的连续映射。由串行FRAM的存取特性可知,从FRAM存储器中一次连续读多条记录的效率远远大于一次读一条记录。又从内存存储协议可知,每条记录保存有月记录号和日记录号,将一个月的所有记录作为一个查询存储器块一次连续读出加载到内存再查询,综合查询效率最高。因此,可确定一个查询存储器块容量Sb为:

其中,N为月记录号;D为日记录号。

将FRAM存储器按每年12个月划分为12个存储器块,就可以制定出测试记录存储格式。以典型I2C总线串行FM24W256为例,存储器容量为256 KB,即32 KB×8位。假设每条记录占用的最大字节长度L=32(20H),规定一天最多允许保存4条测试记录,一个月最多允许测试保存40条记录,则一个查询存储器块的容量为500H。12个月占用的存储器块容量为3C00H。因此,FM24W256可以保存2年的测试记录,将32 KB平分为2个16KB,低16KB (0x0000~0x3FFF)空间存储奇年测试记录,高16KB (0x4000~0x7FFF)空间存储偶年测试记录,例如: 2013年数据存于低16 KB内存单元,2014年数据存于高16 KB内存单元。为了简化查询算法,将一年的12个月份分别对应于12个不同的存储器块,每个存储器块的地址范围是固定的,每个存储器块中每条记录的地址范围也是固定的。FM24W256奇年和偶年测试记录存储格式如图8所示。

图8 奇/偶年FM24W256测试记录存储格式

(2)查询索引号单元

奇/偶年的12个查询索引号单元用于保存12个月的测试记录总数,约定月测试记录总数最大为40。奇/偶年码存储单元用于存放奇/偶测试年码,每当写测试数据时,先将测试年码读出,与RAM缓冲器中的测试数据奇/偶年码存储单元内容比较,若不同,则将12个索引号单元清零。然后将奇/偶测试年码存入奇/偶年码存储单元。若相同,读取奇/偶测试年对应月索引号单元中的内容,若小于40,进行加一回写操作,若等于40,说明该月记录已满。

由此可见,满足串行FRAM查询的RAM加载存储器容量下限值Sd为:

其中,Sb为FRAM的一个查询存储器块容量。

最优的查询机制是根据查询日期,能快速定位相匹配的FRAM查询存储块,读出加载到查询存储块内存缓冲器,再执行快速查询算法就能以较少的软件开销,高效查询到相匹配的测试记录。

6 FRAM块读/写与快速查询算法

6.1 FRAM块写算法

将RAM缓冲器中的测试数据写入FM24W256存储器的块写算法步骤为:

(1)测试数据奇/偶年码与从FM24W256奇/偶年号存储单元读出的年码相比较,若相等,转入步骤(2)。若不相等,表明测试数据年码是新年码,本

测试数据为欲写的第1条记录,则立即将新年码写入FM24W256的奇/偶年码存储单元,并将对应该年的12个月索引号单元清零,转入步骤(3)。

(2)从FM24W256对应测试月索引号单元读取月记录号N,若N为0,表明该测试月尚无记录被保存,转入步骤(3)。若N=40,则说明当月记录保存数已满,则置本月记录已满标志为1,退出块写操作。若N(40,则转入步骤(4)。

(3)将测试数据月记录号存储单元和日记录号存储单元均置1,由月记录号N和日记录号D,计算测试数据保存到FM24W256存储单元首址Aorg的公式为:

其中,OEorg为写测试记录的FM24W256奇/偶年码首地址;L为每条记录的字节长度。以Aorg作为FM24W256块写子程序入口参数1,写测试记录RAM缓冲器首址作为入口参数2,记录字节长度L作为入口参数3,调用FM24W256块写子程序,块写算法结束。

(4)从FM24W256对应测试月的上一条测试记录的日存储单元读取日码,与测试数据的日码相比较,若相等,表明测试数据与上一条保存的测试记录属于同天测试,则再从FM24W256保存的上一条测试记录的日记录号单元读取日记录号,若该日记录号=4,说明当日记录保存数已满,则立即置“本日记录已满”标志为1,退出块写操作。若该日记录号(4,表明本条测试记录可以写入FM24W256,故将该日记录号加1,回写入RAM缓冲器测试数据的日记录号单元,同时,从FM24W256保存的上一条测试记录的月记录号单元读取月记录号,将该月记录号加1,回写到RAM缓冲器测试数据中月记录号单元,转入步骤(5)。若不相等,表明待写测试数据与上一条保存记录不属于同一天测试,则将RAM缓冲器测试数据的日记录号存储单元置1,同时,从FM24W256上一条测试记录的月记录号单元读出月记录号,将该月记录号加1,回写入RAM缓冲器测试数据的月记录号单元,转入步骤(5)。

(5)由式(3)计算Aorg,作为FM24W256块写子程序入口参数1,测试数据RAM缓冲器首址作为入口参数2,测试数据字节长度L作为入口参数3,调用FM24W256块写子程序。最后,把FM24W256对应测试月的月索引号单元内容读出,加1再写回,块写算法结束。

6.2 FRAM块读算法

为了降低查询FM24W256存储器数据的复杂度,把存放在FM24W256中对应查询月的所有测试记录,即1个查询存储器块的全部测试记录读出加载到RAM查询块内存缓冲器,再进行日码匹配查询。故只须利用查询年、月信息来计算FM24W256块读首地址,将块长度为500H的存储空间的内容顺序读出并顺序加载到RAM指定查询块内存缓冲器。一个查询存储器块读出加载到RAM查询块内存缓冲器的块读算法步骤如下:

(1)查询日期的年码与从FM24W256年码存储单元读出年码相比较,若相等,转入步骤(2)。若不相等,说明查询的年码不在存储范围,立即将无记录标志位置1退出查询,通知主程序报警显示“无此年记录”。

(2)从FM24W256对应查询月的月索引号单元读出索引号N,若N=0,说明本月无任何记录,立即置无记录标志位为1,退出查询,通知主程序报警显示“无此月记录”。若N(0,转入步骤(3)。

(3)由查询月计算存放在FM24W256的查询存储器块首址Borg的公式为:

以Borg作为FM24W256块读子程序的入口参数1,RAM查询块内存缓冲器首地址作为入口参数2,读块长度N×500H作为入口参数3,调用FM24W256块读子程序,块读算法结束。

6.3 内存映射快速查询算法

由于每月抽检测试的日期是不定的,每月测试记录存储空间第1个测试记录存储区可以存放任一日的测试记录,这就使RAM查询块加载缓冲器的记录查询不能采用二分法等传统快速缩小查询区间的查询法,只能用顺序查询。但可以利用月索引号N作为查询次数计数器,大于N条记录对应的缓冲器空间就不需要查询,从而可以加快查询速度。查询存储块内存缓冲器快速查询算法步骤如下:

(1)查询指针初始化指向RAM查询块内存缓冲器第1条记录的“日码”存放单元首址,查询月记录计数器初始化初值为月索引号N。查询结果指针初始化指向查询结果匹配记录指针表首址,查询记录匹配计数器始化初值为0。

(2)由查询指针顺序读取每条记录的“日、月、年”码与键盘输入需查询记录的“日、月、年”码逐一相比较,若相等,转入步骤(3)。若不相等,转入步骤(4)。

(3)将查询记录匹配计数器加1,查询指针存入查询结果指针表中,查询结果指针+2指向查询结果匹配记录指针表的下一个指针单元首址。判月记录计数器当前值是否小于等于4,若小于等于4,则立即将月记录计数器减1,转入步骤(4)。若大于4,则立即将月记录计数器置为3,转入步骤(4),因为日测试记录是顺序存放的,而且协议规定一天只允许保存4条测试记录,所以找到第1条日记录,只要再

顺序查询3条记录的存储空间就可以快速结束查询,实现了快速查询。

(4)查询指针+每条记录长度,指向下一条记录日码存放单元首址,记录计数器减1,判断记录计数器是否为0,若不等于0,转到步骤(2),若等于0,转到步骤(5)。

(5)查询记录匹配计数器的非零数字表示查询到的某天测试记录总数。查询结果匹配记录指针表存放每条匹配记录的日码存放单元首址,查询算法结束。显示程序就可以根据查询结果来调用测试记录显示和打印。

6.4 RAM与FRAM数据一致性保护

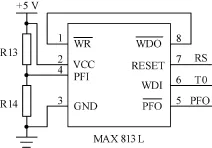

若微处理器正在执行FRAM块写测试数据操作,突然发生电源掉电故障,就有可能导致RAM缓冲器测试数据写入FRAM不完整。为了保障断电瞬间RAM缓冲器的测试数据与FRAM保存的测试记录一致,设计一个电源故障检测电路,当电源电压跌落到掉电故障电平以上某一预警值时,就立即向微处理器发出NMI(不可屏蔽中断)或高优先级中断请求,微处理器响应中断后,立即判断当前是否正在写测试数据,若是,立即停止写操作,并将RAM缓冲器测试数据立即保存到后备电池保护RAM中,以便电源故障解除后,根据重写标志,恢复数据,重写测试数据。一般来说,实时时钟芯片电路都内嵌有后备电池保护RAM电路。设计的电源故障检测电路如图9所示。利用电源监视芯片MAX813L的电源电平监视功能,将电源故障输入引脚PFI设置为单片机故障电平4.5 V以上的某一预警电平,例如4.65 V,当系统正常电源电压+5 V因故障跌落到4.65 V时,MAX813L的电源故障输出引脚PFO产生一个低电平脉冲,将PFO连接到微处理器的NMI (不可屏蔽中断输入)引脚或高优先级的可屏蔽中断引脚上,触发电源故障中断请求。

图9 电源故障检测电路

7 结束语

针对串行FRAM存储器占用I/O资源少、存取速度快、读写无限次等突出优点,本文提出采用串行FRAM存储器构建嵌入式系统固态存储器的实用方法。通过制定FRAM与系统RAM相结合的最优存储协议,设计出串行FRAM存储器快速查询算法。电机驱动总成载重测试仪工业性实验表明,FRAM存储器保存的测试数据安全可靠,历史查询快速准确,满足嵌入式系统长期保存大量数据和快速查询的需要。

[1]刘 静,王计元.24C系列串行EEPROM与单片机的接口设计及应用[J].上海电力学院学报,2011, 27(4):353-357.

[2]马丰玺,杨 斌,卫洪春.非易失存储器NAND Flash及其在嵌入式系统中的应用[J].计算机技术与发展, 2007,7(1):203-205,209.

[3]Ramtron International Corporation.FM24W256.pdf[EB/ OL].(2012-07-23).http://www.ramtron.com.

[4]朱 磊.CCS环境两次编程实现DSP串行EEPROM自举的方法[J].微计算机应用,2010,31(2):72-75.

[5]刘 晋,王政林,薛凯方.基于STC12C5A60S2单片机的LED显示屏硬件设计[J].微型机与应用,2011, 30(22):24-27.

[6]袁春柱,朱庄生,孙 科.微小卫星星上数据存储单元设计与实现[J].数据采集与处理,2010,25(z1): 110-115.

[7]陆 浩,王振占.高速大容量固态存储器设计[J].计算机工程,2011,37(15):226-227,231.

[8]梁亚军,刘培基.双口RAM用于闪存实时数据存储研究[J].青岛大学学报:工程技术版,2008,33(2): 18-21.

[9]2013年Cypress(原RAMTRON)铁电存储器选型表[EB/OL].(2013-09-23).http://pan.baidu.com/ share/link shareid=4286959507&uk=4147947078&fid =4137793134.

[10]孙宇航,秦贵和,于新波,等.嵌入式Linux下的FRAM驱动程序设计[J].计算机工程,2011,37(11): 264-266.

[11]林春平,张兴龙.铁电存储器在机舱油气浓度数据记录仪的应用[J].中国航海,2010,33(1):30-32,69.

[12]黄建军,张志安,陈 俊,等.基于铁电存储器的弹载数据高速存储系统研究[J].测试技术学报,2013, 27(1):50-55.

[13]Hufenbach W,Bö2hm R,Thieme M,et al.Damage Monitoring in Pressure Vessels and Pipelines Based on Wireless Sensor Networks[J].Procedia Engineering, 2011,10:340-345.

[14]Cabero J M,Molina V,Urteaga I,et al.Acquisition of Human Traces with Bluetooth Technology:Challenges and Proposals[J].Ad Hoc Networks,2014,12:2-16.

[15]Tai Haijiang,Li Daoliang,Wang Cong,et al.Design and Characterization of a Smart Turbidity Transducer for Distributed MeasurementSystem[J].Sensorsand Actuators A Physical,2012 175:1-8.

[16]Yu Pengcheng,Li Changying,Rains G,et al.Development of the Berry Impact Recording Device Sensing System: Hardware Design and Calibration[J].Computers and Electronics in Agriculture,2011,79:103-111.

[17]Olivares A,Olivares G,Mula F,et al.Wagyromag: Wireless Sensor Network for Monitoring and Processing Humanbody Movement in Healthcare Applications[J].Journal of Systems Architecture,2011,57:905-915.

编辑 顾逸斐

Construction of Solid-state Memory Based on Serial FRAM

ZHANG Xiaoming,SONG Lei

(College of Information Science and Engineering,Changzhou University,Changzhou 213164,China)

In order to simplify the design complexity of using NAND flash storage to save mass data in embedded systems,a method of constructing solid state memory using Ferroelectric Random Access Memory(FRAM)to achieve fast and efficient access is presented.The optimal protocol of the combination of serial FRAM and RAM is developed.The concept of memory block query and fast query algorithm of serial FRAM data storage are proposed.The storage protocol of the combination of serial FRAM and RAM and the algorithm of block read/write are introduced.The design of motor drive system load tester based on 51 single chip microcomputer and industrial tests show that the solid state memory designed by ferroelectric memory has smaller software and hardware overhead,faster access speed,the realization of simple and reliable.It meets the long-term storage requirements of embedded systems.

solid state memory;Ferroelectric Random Access Memory(FRAM);storage protocol;I2C bus;data query; block read/write

张小鸣,宋 磊.基于串行FRAM的固态存储器构建[J].计算机工程,2015,41(3):64-70.

英文引用格式:Zhang Xiaoming,Song Lei.Construction of Solid-state Memory Based on Serial FRAM[J].Computer Engineering,2015,41(3):64-70.

1000-3428(2015)03-0064-07

:A

:TP333

10.3969/j.issn.1000-3428.2015.03.012

张小鸣(1958-),男,教授、博士,主研方向:嵌入式系统;宋 磊,硕士研究生。

2014-03-10

:2014-05-27E-mail:xm0298@163.com